# MULTIOBJECTIVE SYNTHESIS OF LOW-POWER REAL-TIME DISTRIBUTED EMBEDDED SYSTEMS

Robert P. Dick

A DISSERTATION

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

ELECTRICAL ENGINEERING

November 2002

© Copyright 2005 by Robert P. Dick.

All rights reserved.

## **Abstract**

This dissertation presents methods for automating the synthesis of embedded systems, i.e., special-purpose computers. In addition, it describes a method for analyzing the manner in which real-time operating system use influences embedded system power consumption.

After introducing the embedded system synthesis problem and summarizing previous work in the field, we present four evolutionary algorithms that simultaneously optimize the different costs of embedded systems, e.g., price, power consumption, response time, and area, while ensuring that hard real-time constraints are met. These algorithms generate multiple solutions that present tradeoffs between different architectural costs. Each algorithm targets a different embedded system domain. The first algorithm synthesizes distributed embedded systems. The second synthesizes systems-on-chip composed of intellectual property cores that may come from different vendors. It does clock selection, floorplanning block placement, and bus topology generation. The third synthesizes distributed client-server systems in which the bandwidth of client-server communication is tightly constrained, e.g., wireless embedded systems. It incorporates a novel scheduling method tailored to embedded systems with multiple clients for each server. The fourth synthesizes embedded systems that may contain reconfigurable processors. In addition, we present a method of analyzing the effects of real-time operating system usage on the overall performance and power consumption of embedded systems.

# **Acknowledgments**

First, I would like to thank my advisor, Niraj Jha. We closely collaborated on all the work presented in the body of this dissertation. He has all the traits of an excellent research advisor; he is intelligent, diligent, methodical, careful, imaginative, and even-tempered. I appreciate the corrections and suggestions offered by my dissertation readers: Niraj Jha, Sharad Malik, and Anand Raghunathan. In addition, Keith Vallerio helped me with numerous administrative and research problems while I was writing this dissertation.

I would like to thank Zhen Luo for modifying his design rule checking software [1] in order to collect metal density information from a number of layouts. This information was used to build the system-on-chip synthesis benchmarks described in Sections 6.8 and 7.10.2. It also reinforced my view that one can relate global routing layer metal density to floorplanner quality. I appreciate Zhigang Pan's help in answering the questions I asked while implementing his, and Jason Cong's, wiring delay model [2] for use in the work described in Section 7.7. I thank David Dobkin for his suggestions during design of the bus topology generation algorithm described in Section 7.8. He helped me to look at the problem from an unconventional perspective. I-Jong Lin's suggestions helped in developing the clock frequency selection algorithm (Section 7.10.1).

In addition to Niraj Jha, Anand Raghunathan and Ganesh Lakshminarayana collaborated on the real-time operating system power consumption analysis work described in Chapter 10. Much of this work was done during my term as an employee of NEC Computer and Communications Research Laboratories. I would like to thank Dr. Leslie French, from NEC C&C Research Labs, for helpful discussions on real-time operating systems and his assistance with the Ethernet interface example. David Rhodes, Wayne

Wolf, and I collaborated on the parametric task graph and resource database project described in Appendix A.

I would like to thank André Tits for correcting a multiobjective optimization terminology error in Section 4.5 and Forrest Brewer for encouraging me to describe a method of supporting streaming data communication within the task set model in Section 3.5.

Niraj Jha, Sun-Yuan Kung, Margaret Martonosi, Sharad Malik, Larry Peterson, and Andrew Yao gave competent instruction and advice about numerous engineering problems. I was glad to have the opportunity to discuss research with Jiong Luo, Li Shang, Tat Kee Tan, Shaojie Wang, Keith Vallerio, Yuan Xie, and Lin Zhong. Sarah Griffin, Sheila Gunning, and Karen Williams helped me deal with the university's bureaucracy. In addition, Sheila and Karen advised me as if I were a younger brother.

Financial support for my work at Princeton University was provided by an NSF Graduate Fellowship, NSF Grant Number MIP-9423574, a grant from NEC C&C Research Labs, Princeton University's George Van Ness Lothrop Fellowship in Engineering, Army CECOM, and DARPA under contract number DAAB07-00-C-L516.

# **Contents**

| Al | Abstract |                                                 |    |

|----|----------|-------------------------------------------------|----|

| A  | know     | vledgments                                      | iv |

| 1  | Intr     | oduction                                        | 1  |

|    | 1.1      | Embedded system design automation               | 3  |

|    | 1.2      | Multiobjective embedded system design           | 5  |

|    | 1.3      | Power consumption                               | 6  |

|    | 1.4      | Dissertation overview                           | 8  |

| 2  | Past     | work                                            | 11 |

|    | 2.1      | Hardware-software co-design research            | 12 |

|    | 2.2      | Hardware-software co-synthesis                  | 15 |

| 3  | Defi     | nitions                                         | 21 |

|    | 3.1      | Hardware-software co-synthesis decisions        | 22 |

|    | 3.2      | Problem taxonomy                                | 22 |

|    | 3.3      | Constraint specifications: Multi-rate task sets | 24 |

|    | 3.4      | Multi-rate task sets for real-time systems      | 26 |

|    | 3.5      | Modification of the task set model for          |    |

|    |          | pre-computation and streaming                   | 29 |

|   | 3.6  | Processing elements (PEs)                            | 30 |

|---|------|------------------------------------------------------|----|

|   | 3.7  | Communication resources                              | 31 |

| 4 | Opti | mization algorithms                                  | 33 |

|   | 4.1  | Solving NP-hard problems                             | 33 |

|   | 4.2  | Simulated annealing                                  | 38 |

|   | 4.3  | Genetic algorithms                                   | 40 |

|   | 4.4  | Parallel recombinative simulated annealing (PRSA)    | 43 |

|   | 4.5  | Multiobjective optimization                          | 43 |

| 5 | Synt | hesis of Low-Power Heterogeneous Distributed Systems | 49 |

|   | 5.1  | Requirements for the optimization algorithm          | 50 |

|   | 5.2  | Specialized hardware resources                       | 51 |

|   | 5.3  | Solution representation                              | 53 |

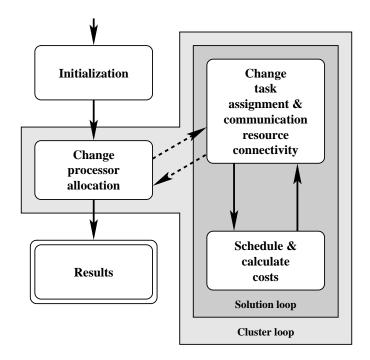

|   | 5.4  | Optimization algorithm                               | 56 |

|   | 5.5  | Clusters                                             | 57 |

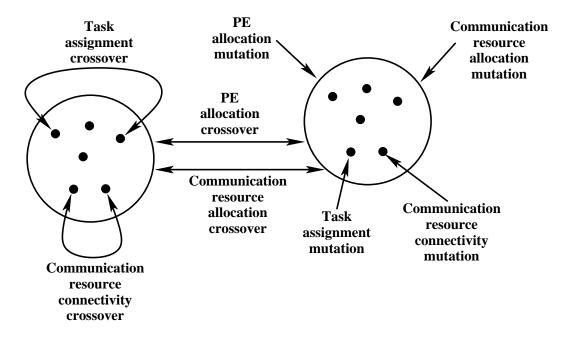

|   | 5.6  | Initialization and genetic operators                 | 61 |

|   | 5.7  | Solution evaluation                                  | 64 |

|   |      | 5.7.1 Scheduling                                     | 65 |

|   |      | 5.7.2 Task graph copies                              | 69 |

|   |      | 5.7.3 Cost calculation                               | 71 |

|   |      | 5.7.4 Constraint violation                           | 72 |

|   | 5.8  | Ranking and reproduction                             | 73 |

|   | 5.9  | Experimental results                                 | 75 |

|   |      | 5.9.1 Price optimization                             | 76 |

|   |      | 5.9.2 Multi-objective power and price optimization   | 82 |

|   | 5 10 | Conclusions                                          | 96 |

| 6 | Enh   | anced Low-Power Heterogeneous Distributed Systems Synthesis          | 87 |

|---|-------|----------------------------------------------------------------------|----|

|   | 6.1   | Communication and memory model                                       | 88 |

|   | 6.2   | Optimization infrastructure                                          | 89 |

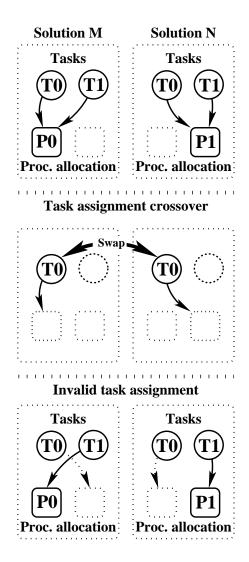

|   | 6.3   | Multidimensional locality preserving crossover                       | 91 |

|   | 6.4   | Guided task assignment mutation                                      | 94 |

|   | 6.5   | Initialization                                                       | 00 |

|   | 6.6   | Cost calculation                                                     | 01 |

|   | 6.7   | Solution cache                                                       | 02 |

|   | 6.8   | Benchmarks                                                           | 03 |

|   | 6.9   | Experimental results                                                 | 06 |

|   |       | 6.9.1 Multiobjective optimization for the E3S benchmarks 1           | 06 |

|   |       | 6.9.2 Price-only optimization for examples from the the literature 1 | 07 |

|   | 6.10  | Conclusions                                                          | 13 |

| 7 | Intel | llectual Property Core-Based System-on-Chip Synthesis 1              | 15 |

|   | 7.1   | Motivation                                                           | 16 |

|   | 7.2   | IP core model                                                        | 17 |

|   | 7.3   | Algorithm overview                                                   | 18 |

|   | 7.4   | Clock selection                                                      | 20 |

|   | 7.5   | Tie prioritization                                                   | 28 |

|   | 7.6   | Floorplan block placement                                            | 29 |

|   | 7.7   | Wiring delay and power consumption model                             | 31 |

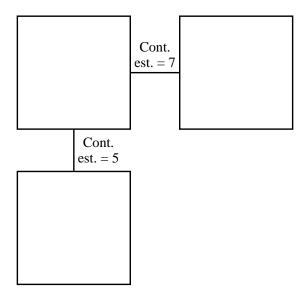

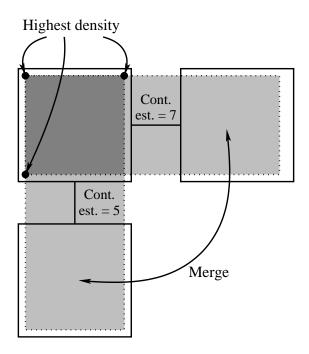

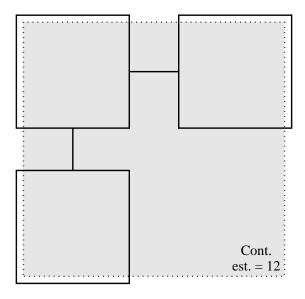

|   | 7.8   | Bus topology generation                                              | 32 |

|   |       | 7.8.1 Motivation                                                     | 32 |

|   |       | 7.8.2 Definitions and assumptions                                    | 33 |

|   |       | 7.8.3 Overview                                                       | 34 |

|   |       | 7.8.5 Overview                                                       |    |

|    | 7.9  | Cost calculation                                                     | 138 |

|----|------|----------------------------------------------------------------------|-----|

|    | 7.10 | Experimental results                                                 | 139 |

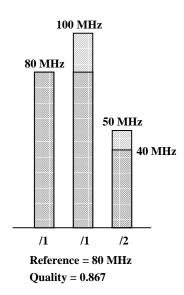

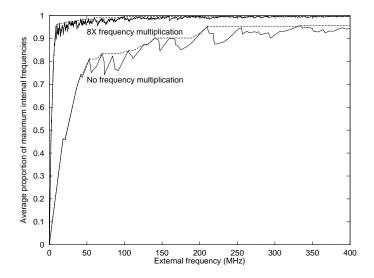

|    |      | 7.10.1 Clock selection                                               | 140 |

|    |      | 7.10.2 Impact of floorplanning block placement and bus topology gen- |     |

|    |      | eration                                                              | 141 |

|    |      | 7.10.3 Multiobjective optimization for the E3S benchmarks            | 147 |

|    | 7.11 | Conclusions                                                          | 148 |

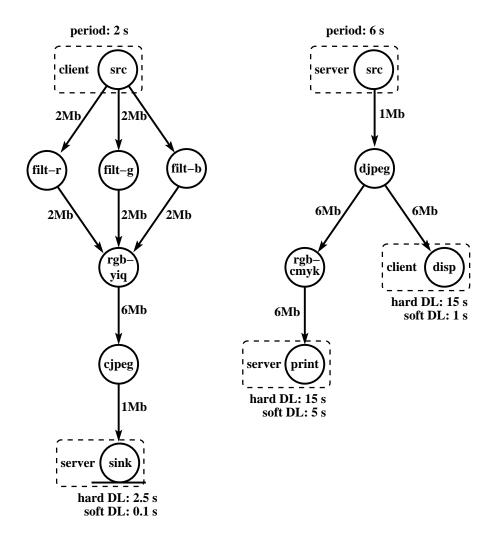

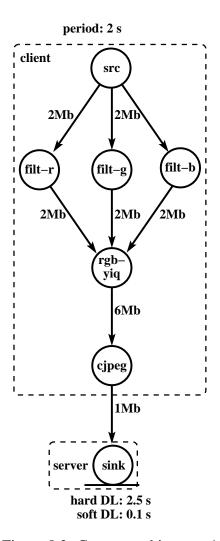

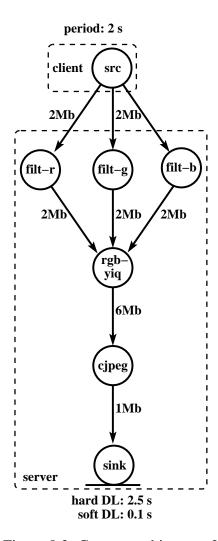

| 8  | Wire | eless Low-Power Client-Server System Synthesis                       | 151 |

|    | 8.1  | Problem formulation                                                  | 153 |

|    | 8.2  | Motivating example                                                   | 155 |

|    | 8.3  | Scheduling and client-server pipelining                              | 159 |

|    | 8.4  | Cost calculation                                                     | 168 |

|    | 8.5  | Experimental results                                                 | 169 |

|    |      | 8.5.1 Multiobjective optimization for the E3S benchmarks             | 169 |

|    | 8.6  | Conclusions                                                          | 174 |

| 9  | Synt | hesis of Dynamically Reconfigurable Embedded Systems                 | 175 |

|    | 9.1  | Motivation                                                           | 176 |

|    | 9.2  | FPGA model                                                           | 177 |

|    | 9.3  | Scheduling                                                           | 179 |

|    | 9.4  | Experimental results                                                 | 183 |

|    | 9.5  | Conclusion                                                           | 188 |

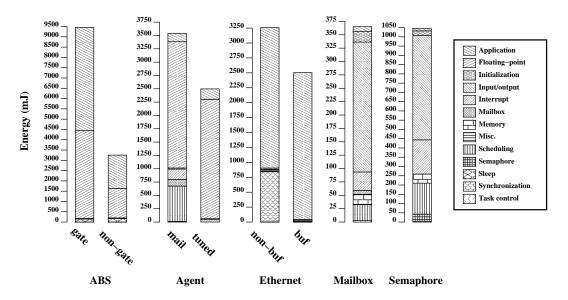

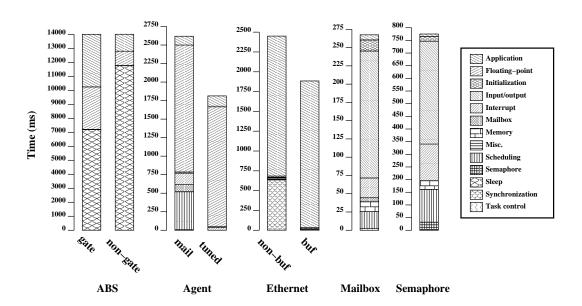

| 10 | Anal | ysis of Energy Consumption in Embedded Operating Systems             | 189 |

|    | 10.1 | Introduction                                                         | 190 |

|    | 10.2 | Related work and contributions                                       | 193 |

|    | 10.3 | Motivation for RTOS energy analysis                                  | 195 |

| В  | Impl | ementa    | tion                                             | 245 |

|----|------|-----------|--------------------------------------------------|-----|

|    | A.4  | Conclu    | sions                                            | 243 |

|    | A.3  | Databa    | se generation                                    | 241 |

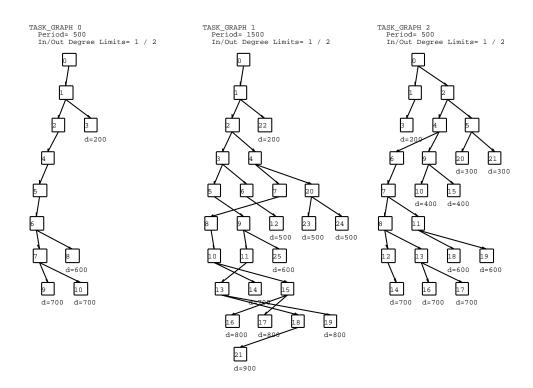

|    | A.2  | Task se   | t generation                                     | 235 |

|    | A.1  | Introdu   | ction                                            | 233 |

| A  | Task | Graphs    | s for Free                                       | 233 |

| 12 | Cont | tribution | ns and Conclusions                               | 229 |

| 11 | Com  | parison   | s with Related Work                              | 225 |

|    | 10.6 | Conclu    | sions and recommendations                        | 222 |

|    |      |           | and case studies                                 |     |

|    |      |           | Extending our approach to other embedded systems |     |

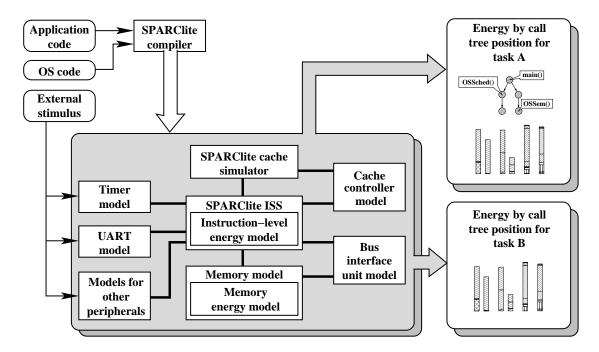

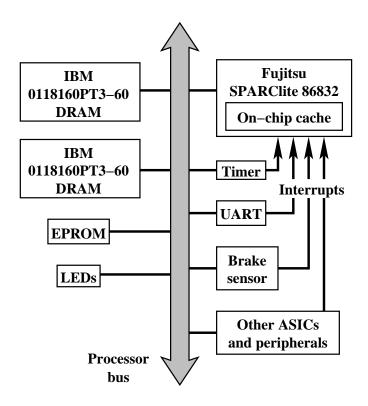

|    |      | 10.4.3    | System details                                   | 211 |

|    |      | 10.4.2    | System overview                                  | 207 |

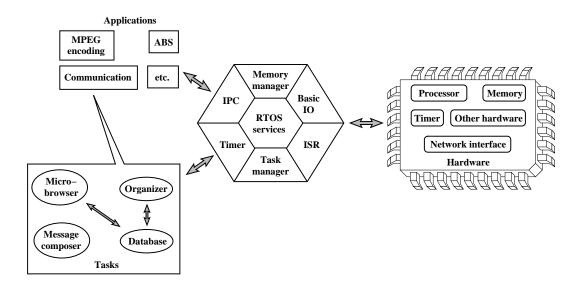

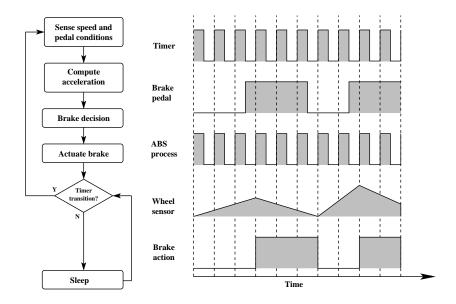

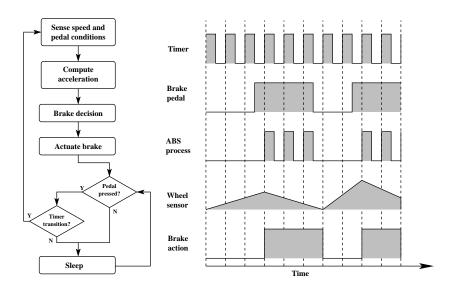

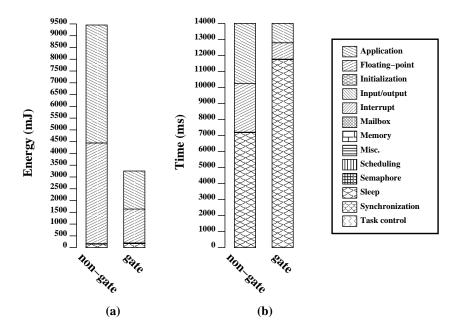

|    |      | 10.4.1    | Inputs and outputs                               | 203 |

|    | 10.4 | Energy    | analysis infrastructure                          | 203 |

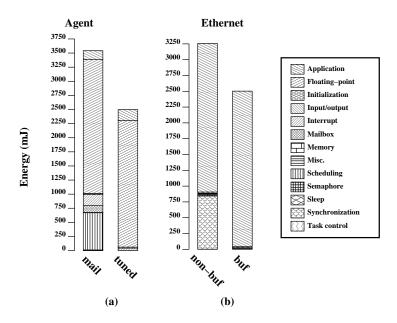

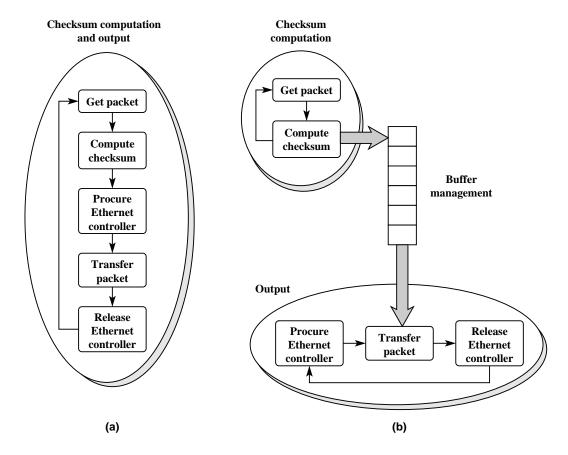

|    |      | 10.3.3    | Ethernet interface example                       | 201 |

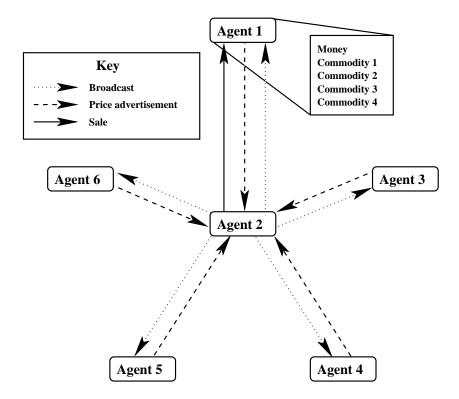

|    |      | 10.3.2    | Commodity trading agent example                  | 198 |

|    |      | 10.3.1    | Anti-lock braking example                        | 196 |

# **Chapter 1**

# Introduction

An embedded system is a computer within a host device, when the host device, itself, is not generally considered to be a computer. For example, the computers within automobiles, medical devices, and range finders are embedded systems. In most applications, well-designed, correctly functioning embedded systems are almost invisible to their users. Although consumers might be pleased that their cars automatically adjust their engine timing to achieve the best non-pinging performance possible with the currently available gasoline, they are unlikely to consider the fact that an embedded system makes this possible. It is also unlikely that most realize embedded systems are responsible for 30% of the price of the average car [3] and that microprocessors, alone, account for 10% of the price [4].

We are surrounded by embedded systems. When I wake up in the morning, the first thing I hear is the speaker of my digital alarm clock, activated by an embedded system. I get out of bed and put my breakfast in the microwave, allowing its water vapor sensing embedded system to perfectly cook my cereal. I call my parents and sister on my cell phone, a wireless client-server embedded system. The call is routed through a telecommunications infrastructure composed of numerous high-performance embedded systems. I get into my car, filled with embedded systems (15 in the average car [5]), and drive to my office, in which I am surrounded by embedded systems (in the copier, in my

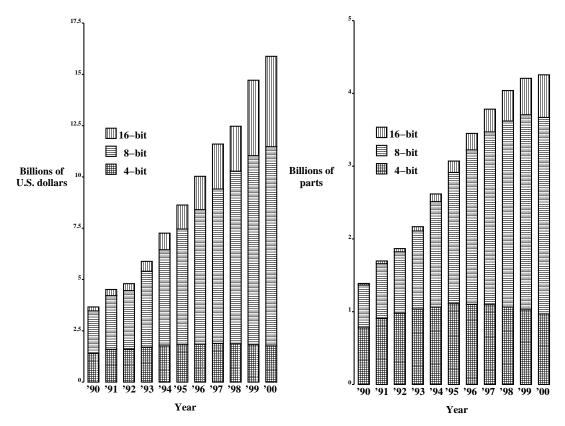

Figure 1.1: Estimated global microcon-troller sales in billions of U.S. dollars [4]. troller sales in billions of parts [4].

calculator, in the printer, and in the vending machine). I use these embedded systems because they make my life better: they make it easier to communicate with those I love, they help me to schedule my time, they improve the speed and safety of travel, they help me to manage information, and they assist me with hundreds of other tasks. Embedded systems make it possible for me to carry out these tasks perfectly without investing the time and energy necessary to become a specialist in hundreds of different skills.

Many consumers value embedded systems. It naturally follows that the size of the embedded systems market is large. Microcontrollers are processors typically used in embedded systems. They may differ from general-purpose processors by having more input/output support integrated on-chip or by having smaller caches. They may be less

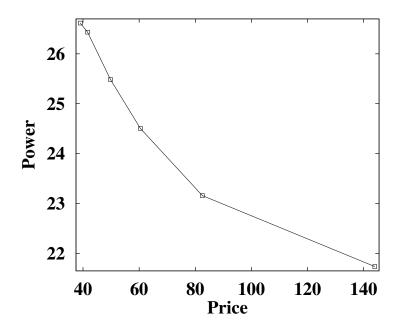

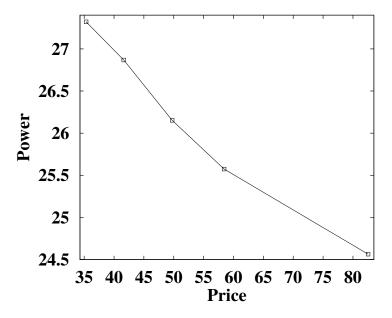

expensive, have lower power consumption, or be designed for specialized tasks. Although embedded systems are composed of many other electronic components in addition to microcontrollers, information about the microcontroller market gives some insight into the embedded systems market. Figures 1.1 and 1.2 give dollar and part volumes for sales of 4-bit, 8-bit, and 16-bit microcontrollers. These figures indicate that the size of the microcontroller market is substantial (approximately \$16 billion in the year 2000) and growing rapidly. Note that microcontrollers only account for a portion of the costs of embedded systems; the embedded system market is substantially larger than the microcontroller market.

In 1998, approximately 250 million 32-bit and 64-bit embedded microprocessors were sold [5], [6]. Even though this number is much higher than that for personal computers, workstations, and supercomputers (100 million [5]), it is dwarfed by the number of 4-bit, 8-bit, and 16-bit microcontrollers sold that year (approximately four billion as shown in Figure 1.2).

### 1.1 Embedded system design automation

Embedded system designers have difficult jobs. Customers have stringent expectations for embedded systems, some of which are listed in Figure 1.3. The first two characteristics in Figure 1.3 imply that embedded system designers need to carefully test their designs to confirm that the designs contain no errors and that every hard deadline is met. Any error has the potential to reduce the profitability of a product. The rigorous design required to meet customer expectations is time-consuming and expensive. A designer might be able to decrease the probability that an embedded system will miss real-time deadlines by using faster and more expensive processors. However, this conflicts with the third and fourth characteristics: people want inexpensive and cool

- 1. Software or hardware errors are not acceptable. Although many people tolerate it when a general-purpose operating system crashes, this sort of behavior is not acceptable for an anti-lock brake system. Many embedded systems have tasks with hard real-time deadlines. Missing a hard deadline is an error.

- 2. Embedded systems should not require bug fixes or upgrades. Expecting customers to change the software or hardware in their cars is unreasonable. Embedded systems are generally more difficult to upgrade than general-purpose applications. If a designer discovers a software error in an embedded system after it has been shipped, correcting that error in the field is likely to be more difficult than upgrading the software of a general-purpose application. Correcting hardware errors is even more difficult.

- 3. An embedded system should be sold at a lower price than competing products, i.e., price competition can be intense. Numerous competitors exist in many embedded systems market segments, e.g., mobile communication devices, home appliances, automobiles, and consumer electronics.

- 4. Power consumption should be low. High power consumption increases the price, weight, and volume of the cooling systems and energy sources used by an embedded system. This is particularly important for portable battery-powered embedded systems.

Figure 1.3: Customer expectations for embedded systems.

products with long battery lifespans. Each favorable attribute of an embedded system design conflicts with other favorable attributes, making it necessary to consider tradeoffs between them.

The incompatible expectations listed above conspire to make an embedded system designer's job difficult and unpredictable. A CMP Media LLC survey of 1,100 embedded system developers in 2001 indicated that the majority of their projects were running late, with a four-month lag the norm. The majority also failed to achieve even half of their expected performance [7]. We advance the following conjecture:

The unpredictability of the embedded system design process is due to the predominance of manual, ad-hoc embedded system design.

According to Napper, "Embedded system design is largely the same as it was 20 years ago, when 8-bit microcontrollers were the state of the art" [8]. Consumer expectations have increased the demands on embedded systems. However, design automation software has not kept pace with the resulting increase in embedded system complexity.

Automation has the potential to help designers keep pace with increasing problem complexity. Its value has been demonstrated in a number of lower-level disciplines. As shown in Table 1.1, design automation has followed the historical trend from automation of low-level stages of the design process toward automation of increasingly high-level stages of the design process. High-level stages of the design process generally have more ambiguous problem definitions than low-level stages. Embedded system synthesis and hardware-software co-synthesis are still open problems. As they become increasingly well-defined and solved, embedded system designers will finally have a practical alternative to ad-hoc design.

### 1.2 Multiobjective embedded system design

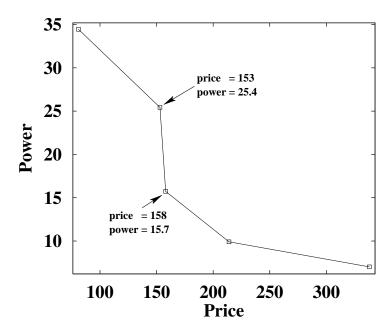

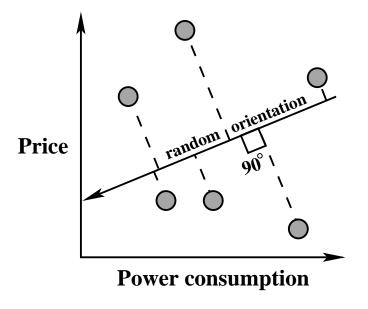

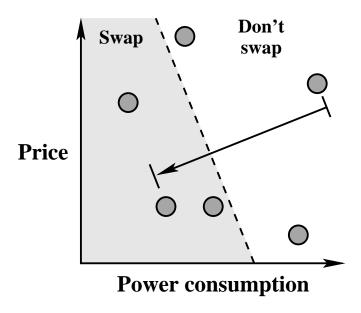

As noted in the previous section, embedded systems have numerous attributes designers attempt to optimize, e.g., power consumption, price, and speed. It is frequently possible to improve one attribute only at the cost of another. This implies that, in order to understand the interplay between different embedded system costs, a designer needs to consider different alternative architectures.

The process of exploring the embedded system design space is equivalent to designing and analyzing numerous different embedded systems. Doing this manually would be time-consuming and expensive. Co-synthesis algorithms automatically synthesize

embedded system architectures. However, the vast majority of existing co-synthesis algorithms are capable of optimizing only one system cost: price. The few co-synthesis algorithms that attempt to minimize other costs either do so in an informal way, replace all but one cost with constraints, or combine multiple costs into a single cost with a weighting sum. Each of these approaches has significant disadvantages, as discussed in Section 4.5. In our research, we have taken care to avoid these disadvantages by developing a truly multiobjective approach to embedded system synthesis.

### 1.3 Power consumption

Although embedded system power consumption is only one cost among many, it has become increasingly important in recent years. In the past, embedded system power consumption was frequently ignored, or modeled in extremely coarse and inaccurate ways. However, proliferation of portable embedded systems during the past few years has focused attention on the reduction of power consumption. Numerous embedded systems (e.g., cellular phones, personal digital assistants, clocks, and games) are portable. It is important that they be light and compact. High power consumption implies high heat dissipation. Embedded systems with high heat dissipation require bulky cooling devices, e.g., heat sinks or fans. In addition, a portable embedded system with high power consumption requires bulkier batteries in order to have the same run time as a lower-power embedded system. Although portability is not a factor for stationary embedded systems, high power consumption is still a disadvantage. It increases the price of running and cooling the embedded system.

Table 1.1: Design tools development [9]

| I            |                                                       |

|--------------|-------------------------------------------------------|

| 1950-1965    | Manual design                                         |

| 1965-1975    | Layout Editors                                        |

|              | Automatic routers (for PCB)                           |

|              | Efficient partitioning algorithm                      |

| 1975-1985    | Automatic placement tools                             |

|              | Well-defined phases of circuit design                 |

|              | Significant theoretical development in all phases     |

| 1985-1990    | Performance-driven placement and routing tools        |

|              | Parallel algorithms for physical design               |

|              | Significant development in underlying graph theory    |

|              | Combinatorial optimization problems for layout        |

| 1990-present | Over-the-cell routing tools                           |

|              | Three-dimensional interconnect based physical design  |

|              | Synthesis tools mature and gain widespread acceptance |

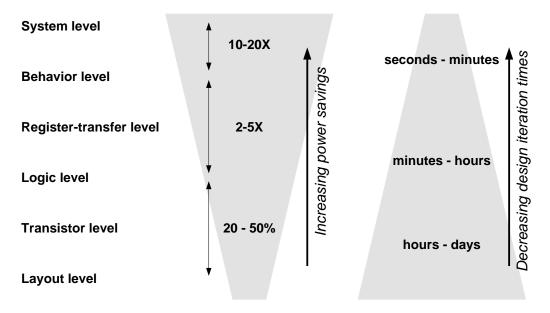

#### Power reduction opportunities Power analysis iteration times

Figure 1.4: Benefits of high-level power analysis and optimization. Used with permission [10].

Power optimization has followed the same general trend as design automation (see Table 1.1 and Figure 1.4). Initially, power consumption was optimized only at the transistor and gate levels. As time progressed, researchers began considering power consumption at the register-transfer and behavioral levels. A few researchers have recently started optimizing power consumption at the system level. Although formulating concrete problem definitions at this level of the design process is more difficult than at the lower levels, the potential for power consumption reduction is greater [10]. In our work, we have taken care to consider the impact of system-level design decisions on power consumption.

### 1.4 Dissertation overview

In Chapter 2, we survey the work of other embedded system synthesis research groups. In Chapter 3, we provide definitions that are useful when discussing hardware-software co-synthesis and embedded system synthesis, formalize the basic hardware-software co-synthesis problem, and describe the evolutionary optimization framework we use to solve this problem. Chapter 4 describes and classifies optimization algorithms that may be used for hardware-software co-synthesis and embedded system synthesis.

In Chapters 5–9, we describe our algorithms to synthesize low-power heterogeneous distributed systems (5 and 6), embedded systems-on-chip (7), client-server embedded systems (8), and distributed embedded systems containing dynamically reconfigurable hardware (9). We present experimental results produced by the software implementations of each of these algorithms. In Chapter 10, we describe our real-time operating system power analysis framework. Chapter 11 contrasts our work with closely related work of other researchers. We summarize our contributions and present conclusions in Chapter 12. Appendix A describes TGFF, a tool that may be used to automatically

generate task sets and resource databases. Appendix B gives details about the software implementations of our hardware-software co-synthesis and embedded system synthesis algorithms.

# Past work

Hardware-software co-design is the concurrent design of the hardware and software portions of a computer system. Most of the work in this field targets embedded systems [11]. Hardware-software co-synthesis is the automated design of a hardware-software computer system. Hardware-software co-synthesis algorithms generally target embedded systems. A number of authors have surveyed the co-design and co-synthesis fields [12]–[18].

Although our work relies on and draws from, or advances, research in numerous fields (e.g., asynchronous design, computer graphics, evolutionary algorithms, interface synthesis, physical design, real-time operating systems, reconfigurable computing, scheduling, simulated annealing, wireless communication), it is most strongly tied to hardware-software co-design and hardware-software co-synthesis. This chapter provides a survey of previous work in these fields. Summaries of related research in other fields are deferred until the relevant sections in the following chapters of this dissertation.

### 2.1 Hardware-software co-design research

This section provides a survey of previous work in the field of hardware-software co-design. Although the software described in this section does not automatically synthesize embedded systems, it assists designers in determining the resources used in an embedded system, and the ways in which they are used. Although it requires a designer in the loop, some of the following software assists in the management of implementation details that are often ignored or modeled in an abstract way in hardware-software co-synthesis systems. In other words, many hardware-software co-design tools tackle less ambitious problems than hardware-software co-synthesis tools but solve them in a way that may sooner be practical for designers to use.

Some researchers have examined the manner in which constraints on an embedded system are specified. Dasarathy described a way to represent and validate timing constraints in embedded systems [19]. Gong et al. developed an algorithm that automatically refines constraint specifications after manual partitioning [20].

Others have focused on performance analysis of hardware-software systems. Calvez and Pasquier developed an event monitor to analyze the performance of an existing hardware-software system [21]. It is often useful to evaluate the performance of an embedded system that has been designed but not yet built. The simulation of hardware-software systems can be time-consuming. As a result, a number of researchers have focused on simulator acceleration. Benner et al. devised a way of rapidly simulating application-specific integrated circuits (ASICs) by using field programmable gate arrays (FPGAs) [22]. Coumeri and Thomas accelerated the simulation of hardware-software systems by running hardware and software simulators on separate processors [23]. Hines and Borriello designed a hardware-software co-simulator that changes its level of detail in order to speed up simulation when accuracy is not essential, while

maintaining accuracy when necessary [24]. Kuttner described a method of rapidly prototyping hardware-software systems by synthesizing and simulating processors [25]. Rowson and Sangiovanni-Vincentelli designed an event-based simulator that sacrifices superfluous details to improve simulation speed [26]. [26]. Thomas et al. used separate Unix processes to simulate hardware and software described in Verilog [27].

Researchers have worked on automating the communication-oriented portions of embedded system design. Castelluccia et al. developed software to automatically compile efficient protocol code from an abstract specification [28]. Freund et al. automated the assignment, bus scheduling, and protocol optimization of communication events [29]. Jirachiefpattana and Lai provided utilities to verify protocol descriptions and translate them between different languages [30]. Smith and De Micheli automated the generation of synchronous interfaces between different hardware elements described with a hardware description language [31].

Some work does not cleanly fit into any of the major co-design categories. Adé et al. developed an algorithm to compute the minimal buffer memory required for deadlock-free satisfaction of multi-rate data flow graph specifications [32]. Coelho et al. automated the process of determining whether old software will function correctly on a new, modified, version of hardware [33]. Gogniat et al. developed a parametric hardware architecture template that is sufficiently general for some special-case applications [34]. Hadjiyiannis et al. developed software that automatically generates an assembler, given a high-level description of a machine [35].

Many researchers have built hardware-software co-design infrastructures that assist a designer in partitioning an embedded system implementation between hardware and software. The ASAR project is a collection of tools and languages that assist a designer in a number of tasks, e.g., specifying the behavior of real-time systems, generating systolic arrays, describing reactive systems, and generating pipelined signal-processing architectures [36]. Bolsens et al. developed a co-design tool that allows interactive refinement of an embedded system specification [37]. The design may be partitioned among multiple heterogeneous processors. Buck et al. built a general signal processing co-design infrastructure [38]. Chiodo et al. automated the analysis of manually partitioned embedded system specifications [39]. Chou and Borriello described transformations and partitioning of embedded system specifications written in a hierarchical state transition language [40]. Hu et al. described the hierarchical refinement of an automotive powertrain architecture [41]. They used increasingly detailed analysis during refinement, as the number of potential solutions decreased. Ismail et al. developed an interactive hardware-software partitioning tool that represents architectures with an extended finite-state machine model [42]. Kalavade and Lee built a manual partitioning, automatic analysis, system for digital signal processing applications [43]. Passerone et al. developed a virtual prototyping infrastructure in which they represented tasks with finite-state machines [44]. They used a homogeneous timing model for hardware and software to allow rapid migration of tasks between the two.

A number of companies sell tools to assist in hardware-software co-design. Most of these are co-simulation software packages for use in co-verification. Co-simulation or, more formally, hardware-software co-simulation, is the process of simulating the interacting hardware and software portions of an embedded system. Generally, the software's behavior is specified using a programming language and the hardware's behavior is specified using a hardware description language (HDL). Although it is possible to use conventional simulators running on general-purpose processors to do co-simulation, this approach is sometimes too slow to be used for co-verification. Co-verification is the process of confirming that the hardware and software portions of an embedded system

function correctly together. Co-simulation tools can be used for co-verification only if they are fast enough to allow a significant portion of an embedded system's functionality to be exercised in a reasonable amount of time. As a result, a number of companies accelerate co-simulation by using special-purpose hardware, e.g., field programmable gate array (FPGA) based hardware emulation engines.

The Virtual Component Codesign (VCC) tools, from Cadence Design Systems, Inc., allow the simulation and modeling of hardware components described in VHDL or Verilog, and algorithms described in C, C++, or a specialized signal processing description language. The N2C Design System, from CoWare, Inc., provides a co-simulation environment for hardware described in Verilog or VHDL. In addition, hardware described in their C and C++ variants can be rapidly simulated through the use of an executable specification. These hardware simulators interface with processor simulators from other vendors. The Seamless hardware-software co-verification environment, from Mentor Graphics, integrates a collection of instruction set simulators for popular embedded processors and logic simulators. Mentor Graphics also sells the Platform Express system-on-chip co-simulation environment. Virtual-CPU Pro, from Summit Design, Inc., allows processor descriptions to be written in C or C++ and rapidly simulated without the use of a logic simulator. The Eagle tools, from Synopsys, Inc., link together hardware simulators from numerous vendors. However, these products suffered from performance problems and Synopsys recently discontinued their sale.

# 2.2 Hardware-software co-synthesis

In this section, we survey past work in the field of hardware-software co-synthesis. Work in this field tackles the ambitious problem of automatically synthesizing embedded systems without guidance from a designer.

A substantial amount of research has focused on a version of the co-synthesis problem in which only a few processing elements (PEs) are allowed (typically one generalpurpose processor and one ASIC), or the communication model is too simple to represent many real embedded systems. Ambrosio and Hu developed a hardware-software partitioning algorithm that uses very high-level estimates of the probability that an architecture can be scheduled [45]. Chatha and Vemuri developed an iterative improvement algorithm to partition task graphs between a single hardware coprocessor and a generalpurpose processor [46]. Eles et al. developed simulated annealing and tabu search hardware-software partitioning algorithms [47]. Ernst et al. developed an algorithm that iteratively migrates embedded system functionality from software to hardware [48]. Gajski et al. developed an algorithm that allows a designer to manually or automatically partition an embedded system specification between different processors [49]. Gupta and De Micheli developed an iterative improvement algorithm to partition real-time embedded systems between a co-processor and a general-purpose processor [50]. Henkel and Ernst developed a dynamic granularity simulated annealing algorithm for hardwaresoftware partitioning [51]. Kalavade and Lee designed a constructive algorithm that partitions a system specification between hardware and software by traversing a list of tasks [52]. It dynamically changes the relative weights of speed and area in the optimization criterion. Karakehayov developed an algorithm to automatically partition embedded system specifications among homogeneous distributed processors [53]. Knudsen and Madsen used dynamic programming to minimize the execution time of a single general-purpose processor, single ASIC embedded system under an area constraint or minimize the area under an execution time constraint [54]. Koroušić-Seljak and Cooling optimized task assignments with a genetic algorithm [55]. Lee and Shin solved the homogeneous task assignment problem, with consideration of communication, for homogeneous arrays or trees [56]. They transformed this problem to the minimum-cut,

maximum-flow problem and solved it in polynomial time. Liu and Wong developed an iterative improvement algorithm that integrates hardware-software partitioning and scheduling [57]. The algorithm migrates tasks from up to two general-purpose processors to an ASIC. Potkonjak and Rabaey formulated the ASIC algorithm selection problem in a fashion similar to the classical task assignment problem [58]. They used a constructive algorithm to optimize throughput or price. Saha et al. developed a genetic algorithm for hardware-software partitioning [59]. Towlsey efficiently solved the heterogeneous distributed system assignment problem for execution time minimization in the absence of hard real-time deadlines [60]–[62]. Vahid et al. explained the advantages of functional partitioning over structural partitioning [63]. These authors also described a way of functionally partitioning a system-level specification between hardware and software [64].

Recently, researchers have started to consider the heterogeneous distributed embedded system problem without tight limits on resource allocations. Axelsson compared the solutions produced by three different types of algorithms when run on a simplified version of the hardware-software co-synthesis problem: a tabu search algorithm, a simulated annealing algorithm, and a genetic algorithm [65]. See Chapter 11 for a critique of this work. Bender solved this problem with mixed integer linear programming (MILP) [66]. He used a linear weighting sum to combine execution time, processor prices, and communication resource prices. He claimed optimality. However, his approach must use a sub-optimal heuristic pre-processing stage to have any chance of solving complicated (realistic) problems in a reasonable amount of time. Dave et al. used a constructive algorithm to solve the classical multi-rate distributed system cosynthesis problem. This work was extended to target low-power embedded systems [67],

hierarchical embedded systems [68], and embedded systems containing dynamically reconfigurable processors [69]. Hsiung developed a hardware-software co-synthesis algorithm for massively parallel homogeneous software applications in which a small set of solutions is enumerated [70]. Solutions that do not satisfy the specified constraints are eliminated. Jeong et al. developed a hardware-software co-synthesis algorithm that allows the use of incrementally, dynamically reconfigurable hardware [71]. Karkowski and Corporaal allocated and partitioned an ANSI-C specification among homogeneous processors on a single chip [72]. Kuchcinski used constraint logic programming to minimize the price of an embedded system under time constraints [73]. The computational complexity of his algorithm may be arbitrarily reduced, as long as one is willing to tolerate sub-optimal solutions. We believe this is the most formal existing approach to solving a problem similar to the hardware-software co-synthesis problem that, at the same time, remains computationally tractable. Lee et al. developed an A\* search algorithm in order to optimize embedded system resource allocations [74]. This algorithm uses earliest deadline first scheduling integrated with a load balancing assignment algorithm borrowed from behavioral synthesis. It does not model inter-task dependencies. Oh and Ha developed an iterative algorithm targeting the heterogeneous distributed system co-synthesis problem [75]. See Chapter 11 for a more detailed discussion of this work. Prakash and Parker developed a MILP solver for the distributed hardwaresoftware co-synthesis problem [76]. Schwiegershausen and Pirsch developed a MILP solver for the heterogeneous distributed system synthesis problem [77]. Srinivasan and Jha developed a heuristic constructive algorithm that synthesizes fault-tolerant real-time distributed embedded systems [78]. Teich et al. applied an evolutionary algorithm to the co-synthesis problem. They repaired bad solutions instead of avoiding their creation [79]. Their algorithm optimized period and price in the absence of hard real-time constraints. See Chapter 11 for a more detailed comparison between our work and this algorithm. Wolf developed a fast greedy iterative improvement for the classical cosynthesis problem [80]. His algorithm may be used to model communication. However, in the presence of non-zero communication times, this algorithm is no longer guaranteed to produce the minimal cost solutions that meet deadlines. Yen and Wolf also developed an iterative improvement algorithm for the hardware-software co-synthesis problem [81].

A few researchers have focused on improving the way embedded system constraints are expressed to hardware-software co-synthesis systems. Xie and Wolf described an iterative improvement hardware-software co-synthesis algorithm that allows the use of conditionals within task graphs [82]. Kordon and Kaim developed a hierarchical communicating state machine model for large distributed systems [83]. They generated code and Petri nets from this model in order to facilitate implementation and verification of the embedded system.

Some researchers have found ways of preprocessing embedded system specifications in order to allow the co-synthesis algorithm to arrive at better results in less time. Hou and Wolf described a task clustering method to speed co-synthesis and, under some circumstances, improve solution quality [84]. Knudsen and Madsen used a coarse-grained control/data flow graph to build a specification suitable for hardware-software partitioning [85]. They did transformations, selected a task granularity, and conducted communication analysis on the graph.

Others have worked on specifying and computing timing information. Dasdan, et al. explained a method for determining maximum execution rates starting from a generalized task graph specification [86]. Gupta described a sophisticated method for specifying timing constraints for embedded systems [87]. Hu and Sambandam developed a co-synthesis algorithm that treats timing behavior as a multi-valued approximation and produces multiple solutions that trade off different components of the timing behavior,

e.g., feasibility probability and price [88]. Rhee et al. developed a timing tool that computes conservative execution times of tasks on a reduced instruction set computer, taking into account pipelining and cache effects [89].

Communication between PEs, or between the hardware and software portions of an embedded system, has drawn the attention of a few authors. Benner and Ernst developed a simulated annealing co-synthesis algorithm that focuses on the communication process timing model and protocol [90]. Chou et al. synthesized the interface between the hardware and software portions of an embedded system [91]. They simulated the embedded system before, during, and after synthesis. Rhodes and Wolf developed a cosynthesis algorithm featuring a detailed communication model that takes into account real-time operating system preemption costs [92].

Others have worked on analyzing the performance and cost of implementing tasks on different processors and ASICs. Li and Malik devised an algorithm to derive the worst-case performance of software [93]. Rabaey and Guerra described a method for making rough estimates of the complexities of implementing simple digital signal processing algorithms on ASICs [94]. Xie and Wolf developed a way of automatically estimating the performance of different ASICs used as PEs in co-synthesis, and optimizing their implementations [95].

# **Definitions**

This chapter provides definitions that will be useful when describing our hardware-software co-synthesis and embedded system synthesis algorithms. In this dissertation, we use the units conventions of the International System of Units (SI) and International Electrotechnical Commission (IEC), i.e., b is the symbol for bits, B is the symbol for bytes, k is the symbol for  $10^3$ , Ki is the symbol for  $2^{10}$ , and Mi is the symbol for  $2^{20}$ .

Section 3.1 explains the architectural decisions a hardware-software co-synthesis algorithm must make. Section 3.2 gives a taxonomy of the different classes of problems within the hardware-software co-synthesis and embedded system synthesis research areas. Sections 3.3, 3.4, and 3.5 define, and explain enhancements to, multi-rate task sets. This type of specification is used to represent problem constraints in our algorithms, and by other researchers working in hardware-software co-synthesis. Sections 3.6 and 3.7 describe basic models for the computation and communication resources used within embedded systems. This chapter should give the reader a more formal understanding of the co-synthesis problem, and our models for embedded system problem constraints and resources. The definitions presented in this chapter will later be expanded to suit different problem domains.

### 3.1 Hardware-software co-synthesis decisions

There are three decisions that must be made during synthesis of distributed heterogeneous systems. This section describes these decisions.

- **Allocation**: Determine the quantity of each type of resource, e.g., processing elements or communication resources, to use.

- Assignment: Select a resource to execute each task and communication event.

- Scheduling: Determine the time at which each task and communication event occurs.

In addition to making these three decisions, a hardware-software co-synthesis algorithm must evaluate embedded system performance. The costs of an architecture, e.g., price, speed, area, and power consumption, must be computed.

Each of the three decisions, listed above, influences others. Therefore, attempting to consider a decision in isolation, or without feedback from subsequent decisions, is likely to result in poor quality solutions. We have taken care to allow incremental feedback in our algorithms.

Some authors use terms that differ from ours when referring to the decisions made by embedded system synthesis algorithms. *Allocation* is sometimes used to refer to the decisions we separate into *allocation* and *assignment*. Others use *binding* or *mapping* as synonyms for what we call *assignment*.

### 3.2 Problem taxonomy

In this section, we define and classify embedded system synthesis problems. To solve the homogeneous system synthesis problem, one must decide upon an allocation

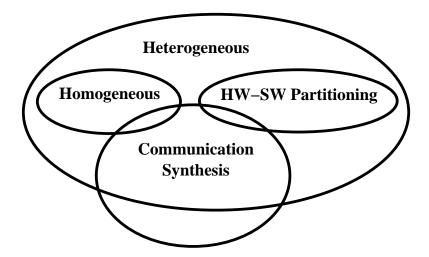

Figure 3.1: Taxonomy of hardware-software co-synthesis problems.

of identical processors, an assignment of tasks to processors, and a schedule for these tasks. The heterogeneous system synthesis problem is similar to the homogeneous system synthesis problem. However, the types of processors in the allocation may differ from each other. The hardware-software partitioning problem allows only two different processors, of different types, in the allocation. To solve the communication synthesis problem, it is necessary to determine a communication resource allocation and assign communication events to communication resources.

As shown in Figure 3.1, algorithms capable of solving the heterogeneous system synthesis problem are also generally capable of solving the homogeneous system synthesis problem and the hardware-software partitioning problem. Some communication synthesis algorithms also tackle the heterogeneous system synthesis problem, the homogeneous system synthesis problem, or the hardware-software partitioning problem, although communication synthesis algorithms need not do processing element allocation, assignment, and scheduling.

In the multi-rate system synthesis problem, cyclic specifications may contain tasks with different intervals of time between subsequent executions. Algorithms that can handle the multi-rate problem can also handle a single rate problem, in which all tasks have the same period. Synthesis algorithms that can handle problems containing data dependencies are also capable of handling problems without data dependencies, i.e., problems containing only independent tasks.

Our algorithms solve problems that are supersets of the classical hardware-software co-synthesis problem or, more formally, the heterogeneous multi-rate distributed system synthesis problem with communication synthesis and data-dependent tasks.

# 3.3 Constraint specifications: Multi-rate task sets

There are a number of methods that may be used to specify the behavior of real-time embedded systems. Many of these representations constrain the allocations and assignments that will ultimately be used for implementation, and are therefore not suitable for use in a synthesis algorithm that needs the freedom to generate its own allocations, assignments, and schedules. State machine based representations can naturally represent the behavior of reactive embedded systems that do not execute complicated algorithms. In addition, they're suitable for use in synthesis because they do not constrain implementation. However, they have historically had the problem of state explosion, e.g., in order for a finite state machine (FSM) to represent two concurrent n-state subsystems,  $n^2$  states are required. Some FSM variants have been developed to reduce this problem [96], [97]. However, timing analysis is often difficult for these variants. Many other representations exist, each of which has its own advantages and disadvantages [98]–[101]. In our system synthesis work, we have modeled embedded system behaviors and timing constraints with muti-rate task sets. This is a natural model for data flow and signal processing behaviors. It is amenable to detailed timing analysis.

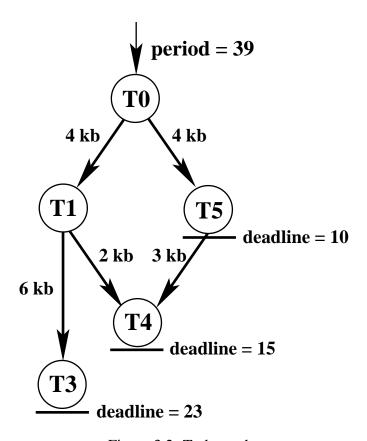

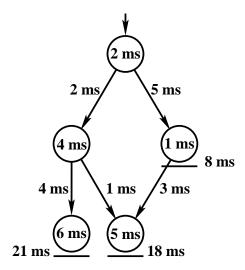

Figure 3.2: Task graph.

This is especially useful for synthesis of hard real-time embedded systems: it allows a synthesis algorithm to guarantee that hard real-time constraints will be met.

Multi-rate task sets may be used to specify some of the requirements a designer places upon an embedded system. A task graph, as shown in Figure 3.2, is a directed acyclic graph in which each node is associated with a task and each edge is associated with a scalar indicating the amount of data that must be transferred between the two connected tasks. Each task may only begin executing after all of its data dependencies have been satisfied. Thus, in Figure 3.2, task T4 may only begin execution after tasks T1 and T5 have each completed execution and transferred two and three kilobits of data, respectively, to task T4.

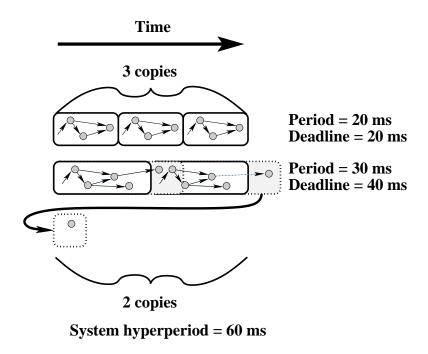

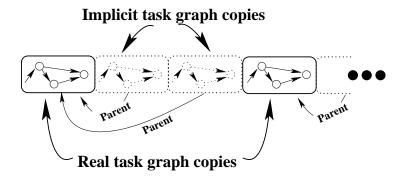

Embedded system synthesis research generally assumes coarse-grained tasks, i.e., each task is complicated enough to require numerous microprocessor instructions. The *period* of a task graph is the amount of time between the earliest start times of its consecutive executions. A node with no outgoing edges is called a *sink* node. A *deadline*, the time by which the task associated with the node must complete its execution, may exist for any node. The deadline of a task graph is the maximum of all the deadlines specified in it. Our task graph model supports hard and soft deadlines. Hard deadlines may not be violated. Soft deadlines need not be met, but violating them is undesirable. If a task should finish executing as soon as possible, it may be given a soft deadline at time zero. A multi-rate task set contains one or more task graphs, each of which may have a different period. The *hyperperiod* of a multi-rate task set is the least common multiple of the periods of the task graphs within the task set.

#### 3.4 Multi-rate task sets for real-time systems

In this section, we consider the advantages and disadvantages of using representations that are closely related to multi-rate task sets for constraint specification in realtime distributed embedded systems.

Some researchers are dissatisfied with multi-rate tasks sets for specifying constraints in real-time distributed embedded systems [102]. It is sometimes claimed that multi-rate task sets are too simple and need to be more expressive in order to allow embedded systems to be realistically modeled. Although the claim that they are simple is correct, researchers sometimes propose adopting extensions from constraint representations that are used to represent problems without hard real-time constraints. However, many of these extensions have significant drawbacks when applied to hard real-time systems. In

this section, these drawbacks are described. In addition, we note one extension that has value when used to specify real-time systems.

Some constraint specification formats are more general than task sets [39], [103], [104]. Such formats might better represent constraints without hard real-time deadlines. However, many of these representations add nothing to a synthesis system targeting hard real-time problems. In other words, when the multi-rate task set representation is extended to handle many apparently interesting generalizations, the extensions must be bounded to allow synthesis of embedded systems that are guaranteed to meet hard real-time constraints. This results in a representation that can be losslessly converted back to a classical multi-rate task set.

If one starts from a multi-rate task set and introduces unbounded loops between start and deadline nodes, it becomes impossible to guarantee that down-stream deadlines in the graphs are met. If one constrains the specification by requiring a bound on the number of times a loop may be executed, then it becomes possible to guarantee that deadlines are met. However, one must guarantee that sufficient time is available, in the schedule, to host the worst-cast number of executions. This leaves one with a representation that is more complicated than a multi-rate task set but provides no advantage. One could achieve the same goal by unrolling loops in a pre-pass transformation into conventional task sets. This transformation would increase the time required for explicit scheduling by approximately the same amount as using a bounded loop representation.

If one starts from multi-rate task sets, introducing a representation for fine-grained parallelism internal to tasks may seem useful in order to allow some tasks to be dynamically split among numerous processors. However, one could pre-process such a graph, splitting nodes conservatively based on the properties of the resources available and thereby convert it, in a mildly lossy way, back into a conventional task graph.

If one starts from multi-rate task sets and introduces communication between nodes in task graphs with different periods, one can losslessly transform such a modified task set into a conventional task set by unrolling the task graphs into the hyperperiod and adding the new communication events. There is another straightforward change required involving start node offsets. For scheduling algorithms that unroll to the multi-rate hyperperiod [105], the resulting increase in scheduling time would not be dramatic.

If one starts from multi-rate task sets and introduces tasks that may start executing before their incoming data have arrived, this format can be transformed into a conventional task set by splitting each such task into a zero-duration parent task that accepts the pre-start arc, and a normal-duration child task that must be assigned to the same processing element as the parent task and that accepts the post-start arc.

If one starts from multi-rate task sets and introduces internal conditionals, it is necessary to reserve sufficient time in the schedule to ensure that the more time-consuming task, and down-stream tasks, can execute. We know of no lossless transformation from a task set with conditionals into a classical task set. Unlike a number of other task set enhancements, conditionals make task sets more expressive, even for hard real-time systems. Eles et al. describe scheduling of conditional task graphs in embedded system synthesis [103]. Their specifications support conditionals. Xie and Wolf developed an embedded system synthesis algorithm that allows task sets to contain conditionals [82]. Their algorithm detects mutually exclusive tasks instead of enumerating all condition combinations. Ziegenbein et al. described a way of representing correlations between the execution of tasks and a small set of execution modes [104]. Although their approach may allow some types of embedded systems to be represented more directly than would be possible with conditionals, it does not substantially reduce the complexity of conducting real-time system synthesis; constraint specifications to which this approach

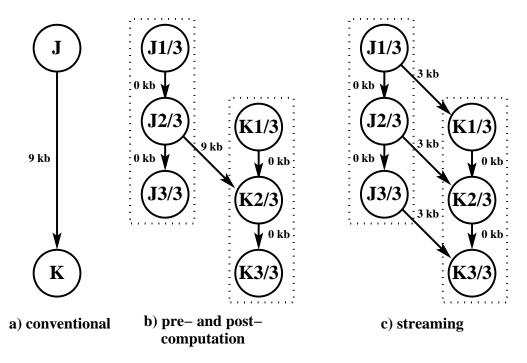

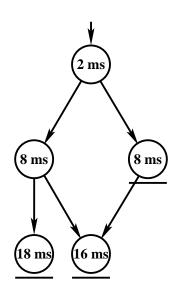

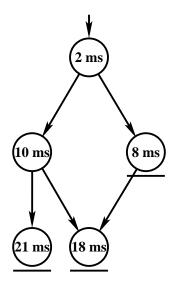

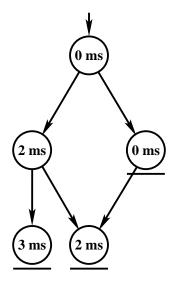

Figure 3.3: (a) conventional model and task assignment grouping to model (b) precomputation and post-computation, as well as (c) streaming data communication.

may practically be applied cannot contain a number of condition combinations that is exponential in the number of graph nodes.

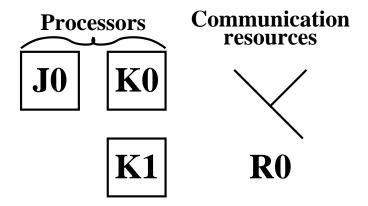

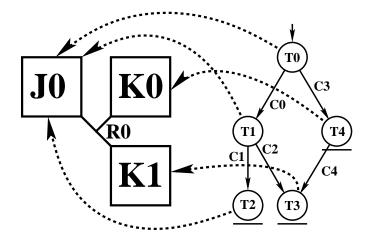

## 3.5 Modification of the task set model for pre-computation and streaming

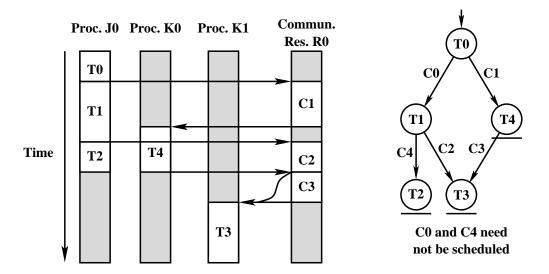

Our algorithms support a task graph model that allows the assignments of multiple tasks within the same task graph to be tied to the same processing element. This makes it possible to model pre-computation and post-computation [76], as well as course-grained streaming data communication. Figure 3.3a illustrates a conventional communication

event between task J and task K. Task J completes execution, 9 kb of data are transferred from task J to task K, then task K executes. In Figure 3.3b, tasks J and K are each split into three sub-tasks. All a task's sub-tasks have their assignment tied to the same processing element, as indicated by the dashed box containing them. This enables pre-computation and post-computation. For example, sub-task K1/3 can execute before sub-task K2/3's input data have arrived (pre-computation), and sub-task J2/3 can transmit output data before sub-task J3/3 has completed execution (post-computation). Figure 3.3c shows a similar use of task assignment tying to model streaming data communication. In this example, instead of first completing task J's execution before conducting one 9 kb communication event, the communication is split into three 3 kb chunks that occur during task J's execution. After each of task J's subtasks (J1/3, J2/3, and J3/3) completes execution, a 3 kb communication event may occur. Note that this streaming data model can easily be made more fine-grained by breaking a task into more subtasks. However, making the streaming data representation more fine-grained will result in an increase in the CPU time required for scheduling.

#### 3.6 Processing elements (PEs)

A PE executes tasks. Our hardware-software co-synthesis and embedded system synthesis algorithms model many types of PEs: general-purpose processors, digital signal processors (DSPs), application-specific integrated circuits (ASICs), multiprocessor integrated circuits (ICs), intellectual property (IP) cores, and FPGAs. However, in this definition, we will describe only the general model for general-purpose processors, DSPs, and ASICs. The features peculiar to multiprocessor ICs, IP cores, and FPGAs will be described in the chapters devoted to the algorithms that use them: Chapters 5, 7, and 9.

A solution may contain multiple instances of the same type of PE. Our algorithms require databases that describe the relationships between tasks and PEs. Characterizing a PEs in this manner requires that the designer know the input vectors that elicit the worst-case execution time for each task-PE pair. Alternatively, one may use worst-case performance analysis tools to determine an upper-bound on execution time, without requiring a specific input vector [89], [106]. In addition, the average power consumption for each task-PE pair must be known or estimated. The power consumption of general-purpose and application-specific processors can be estimated by using models, simulation, and explicit analysis [10], [107]–[111].

The following information establishes the relationships between tasks and PEs:

- A two-dimensional array indicating the worst-case execution time of each task on each PE.

- A two-dimensional array indicating the average power consumption of each task on each PE.

In addition to these arrays, each PE has a price, I/O energy per communicated bit, and idle power consumption. PEs may be buffered, in which case they can communicate and compute at the same time, or unbuffered, in which case communication and computation may not overlap in time. In the case of buffered communication it is, of course, still necessary for a task's incoming data to arrive before it can begin execution.

#### 3.7 Communication resources

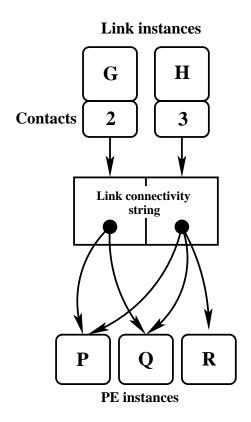

Communication resources have the following attributes: controller price, bits per packet, transmission time per bit, power consumption during operation, number of contacts, and idle power consumption. The number of contacts a communication resource

supports is the number of integrated circuits (ICs) it can connect, i.e., a communication resource with two contacts is a point-to-point communication resource and a communication resource with more than two contacts is a bus. The method of deriving these attributes depends on the type of architecture being synthesized. For example, in a distributed system, the parameters of a communication bus can be determined from the bus specifications, as well as the controller datasheets. If one is targeting a system-on-chip, the behavior of the on-chip busses can be derived from the fabrication process parameters and floorplan using a wire delay and power consumption model, as described in Section 7.7. Each task graph edge must be assigned to a communication resource. The worst-case communication time and average power consumption of an edge are linearly dependent on the integer number of packets transferred via its communication resource. There may be more than one communication resource connected to a PE instance. In previous distributed computing work, it is commonly assumed that communication between tasks that are assigned to the same IC consume an insignificant amount of time and power. We also make this assumption in our distributed system synthesis algorithms. However, we use a detailed wire delay model in our system-on-chip (SOC) synthesis algorithm. If an architecture contains two communicating tasks that execute on separate ICs, the architecture is invalid if there are no communication resources connecting the ICs.

### **Optimization algorithms**

This chapter presents preliminary concepts that will later be used in the description of our evolutionary optimization framework. Section 4.1 gives a brief survey of methods for solving NP-hard problems. Sections 4.2 and 4.3 describe two problem-solving heuristics that are closely related to the optimization infrastructure used in our evolutionary optimization algorithms. This class of algorithms, parallel recombinative simulated annealing algorithms, are described in Section 4.4. In Section 4.5 we explain some of the challenges of solving multiobjective problems, and explain how parallel recombinative simulated annealing algorithms can be adapted to simultaneously optimize multiple costs.

#### 4.1 Solving NP-hard problems

This section gives an introduction to the classes of algorithms that may be used to solve the hardware-software co-synthesis problem and system synthesis problem.

Hardware-software co-synthesis, and embedded system synthesis, contain multiple NP-complete, and therefore NP-hard, problems within them. Worse yet, these problems are interdependent. Allocation/assignment and scheduling are each known to be NP-complete for distributed systems [112]. Any instance of an NP-complete problem can

be converted to an instance of any other NP-complete problem in an amount of time that is, at worst, polynomially dependent on the size of the instance. For decades, clever people have searched for solutions to NP-complete problems that requite time polynomially dependent on the size of the problem instance. However, nobody has ever published an algorithm that optimally solves an NP-complete problem in, at worst, polynomial time. As a result, most algorithm designers operate under the conjecture that finding a guaranteed-optimal solution to an NP-complete problem requires an algorithm that may take an amount of time exponentially dependent on the size of the problem instance. If one can be sure to encounter only very small problem instances, it is practical to use potentially exponential-time algorithms, e.g., A\* [113], dynamic programming [114], mixed integer linear programming [115], branch-and-bound [116], or one of the trivial exhaustive searches. However, if one might encounter large problem instances, the above conjecture implies that one must settle for an algorithm producing solutions that are not guaranteed to be optimal.

Approximation algorithms may be used to produce solutions to NP-complete problems in polynomial time [114], [117]. Although the solutions produced may sometimes be optimal, optimality is not guaranteed. However, approximation algorithms are guaranteed to produce solutions with bounded deviations from optimal cost. Devising approximation algorithms for NP-complete problems remains an area of vigorous research; there are still numerous problems for which approximation algorithms have not yet been developed and analyzed. When attempting to solve such problems, researchers often resort to heuristic algorithms. Good heuristic algorithms can be empirically demonstrated to produce high-quality solutions to important problems most of the time, although no formal proof bounding the deviation of solution costs from optimality may be known. Many effective heuristics fall within one of seven algorithm classes:

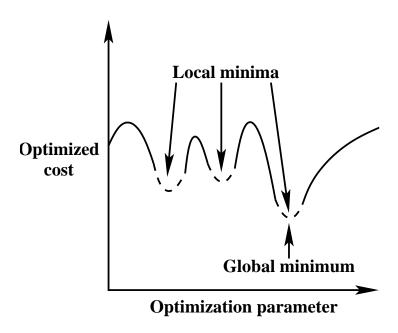

Figure 4.1: Local and global minima.

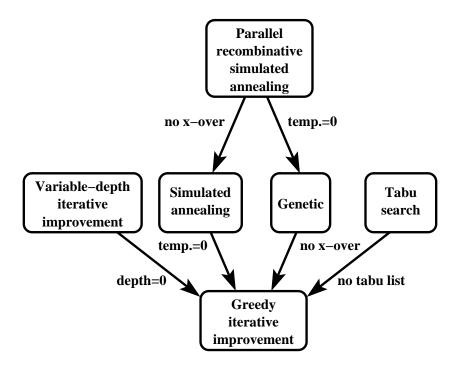

constructive, greedy iterative improvement, variable depth iterative improvement, tabu search, simulated annealing, genetic, and parallel recombinative simulated annealing.

An *optimized cost* is a value optimization algorithms attempt to minimize, e.g., price. For any problem instance, the optimized cost is a function of the *optimization parameters*. An optimization algorithm attempts to find a value of the optimization parameters such that the optimized cost is minimized. The *neighborhood* of a solution to an optimization problem is the set of other solutions that can be reached in one discrete step of the optimization algorithm. A *local minimum* is a solution for which no other solution within that solution's neighborhood has a lower optimized cost. This implies that the local minima in a solution space are based on the optimization algorithm-dependent definition of neighborhood. The *global minima* are those solutions for which the optimized cost is the lowest value possible for the problem instance. In general, optimization algorithms attempt to locate global minima and avoid becoming trapped in local minima. This concept may be illustrated with an example. The curved line in Figure 4.1 shows

the relationship between a problem's optimization parameter and optimized cost. The dashed portions of the line are the neighborhoods surrounding the solutions at the local and global minima. As indicated, although the two local minima on the left are not global minima, there are no lower-cost solutions within the neighborhoods of these solutions. An optimization algorithm with the indicated neighborhoods could become trapped in one of the sub-optimal local minima.

Constructive algorithms generate finished solutions that are not later improved upon. Generally, constructive algorithms are fast. However, they usually follow a fixed set of rules that result in a tightly constrained exploration of the solution space. The qualities of solutions produced by a constructive algorithm are strongly dependent on the amount of problem-specific knowledge built into the algorithm. Greedy constructive algorithms are prone to becoming trapped in local minima.

Iterative improvement algorithms generate a solution and make changes to it in an attempt to improve its quality. We do not require that an algorithm evaluate and rank all possible local moves during each iteration in order classify it as an iterative improvement algorithm. Formally, an iterative improvement algorithm must contain a constructive algorithm within it in order to generate the initial solution. However, most problem-specific knowledge in an iterative improvement algorithm is usually incorporated in the improvement portion of the algorithm, instead of the constructive portion.

Greedy iterative improvement algorithms repeatedly make incremental changes to a solution. If a change results in an improvement, it is accepted. If it results in a degradation, it is rejected. As soon as the solution reaches a position from which no incremental change results in an improvement, the algorithm halts. As a result, this type of algorithm is liable to become trapped in a local minimum.

Variable-depth search algorithms are a type of iterative improvement that is capable of backing out of local minima of arbitrary, but bounded, depth [117]. Of course, run

Figure 4.2: Iterative improvement taxonomy.

time depends on the backtracking depth selected. A variable-depth search algorithm with an infinite backtracking depth may be optimal, assuming its repertoire of changes is sufficient to explore the entire solution space. A variable-depth search algorithm with a backtracking depth of zero is equivalent to a greedy iterative improvement algorithm. Therefore, variable-depth search algorithms are a superset of greedy iterative improvement algorithms, as shown in Figure 4.2.

Tabu search is a form of iterative improvement in which some moves are dynamically prohibited [118]. A tabu list is maintained. This list prevents recently visited solutions from being revisited. A tabu search algorithm with a tabu list of length zero is equivalent to a greedy iterative improvement algorithm. Therefore, tabu search algorithms are a superset of greedy iterative improvement algorithms, as shown in Figure 4.2.

#### 4.2 Simulated annealing

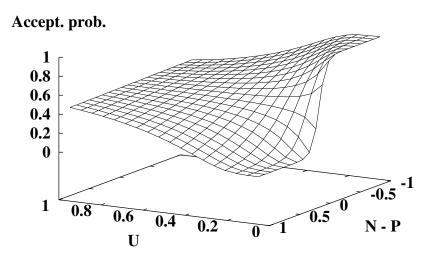

In an iterative improvement algorithm, we define *greediness* as the probability that a cost-decreasing change to a solution will be preferred instead of a cost-increasing change. Simulated annealing algorithms are iterative improvement algorithms in which greediness increases during the run of the algorithm [119]. Simulated annealing algorithms conduct *Boltzmann trials* between solutions before and after modifications; changes are accepted with probability

$$\frac{1}{1 + e^{(N-P)/T}}$$

where T is the global temperature, P is the cost of the old solution and N is the cost of the modified solution.

Boltzmann trials are more easily described with the use of an illustration. Note that, in order to start a simulated annealing algorithm with approximately equal probabilities of selecting changes that decrease or increase cost, it is necessary to initially have a global temperature near infinity. In order to smoothly illustrate the behavior of a Boltzmann trial as the global temperature varies from infinity to zero, we introduce

$$U = 1 - \frac{1}{T+1}$$

U gradually varies from a value near one to zero during the run of a simulated annealing algorithm, causing T to gradually vary from a value near infinity to zero.

When a simulated annealing algorithm begins execution, the global temperature is set to a high value, i.e., U is approximately one. As a result, changes that increase the cost of a solution are selected with approximately the same probability as changes that decrease its cost, as can be seen in Figure 4.3. When U is near one, the acceptance probability is approximately 0.5, independent of the difference between the cost of the current solution, P, and the cost of the modified solution, N. In this explanation,

Figure 4.3: Boltzmann trial acceptance probability.

we assume that  $P,N \in [0,1]$ . At this stage, the algorithm is capable of easily escaping local minima. However, it is not particularly effective at reducing the value of the optimized cost. As time elapses, the global temperature is reduced, gradually changing the behavior of Boltzmann trials until changes that decrease the cost of a solution are always selected and changes that increase the cost are always rejected. In other words, as the global temperature approaches zero, a simulated annealing algorithm degrades to a greedy iterative improvement algorithm. This greedy behavior is depicted by the portion of Figure 4.3 at which U is zero; an improvement in solution quality will always be accepted and a degradation in solution quality will always be rejected. Greedy iterative improvement is a special case of simulated annealing. Therefore, simulated annealing is a superset of greedy iterative improvement, as shown in Figure 4.2.

#### 4.3 Genetic algorithms

Genetic algorithms maintain a pool of solutions that evolve in parallel over time. During each *generation*, genetic operators that allow randomized local changes and the exchange of information between solutions are applied to the solutions in the current pool in order to improve them. The lowest quality solutions are then removed from the pool [120]. Genetic algorithms have the ability to escape local minima and communicate information among solutions. A genetic algorithm with a solution pool containing only a single solution is equivalent to a greedy iterative improvement algorithm. Therefore, genetic algorithms are a superset of greedy iterative improvement algorithms, as shown in Figure 4.2.

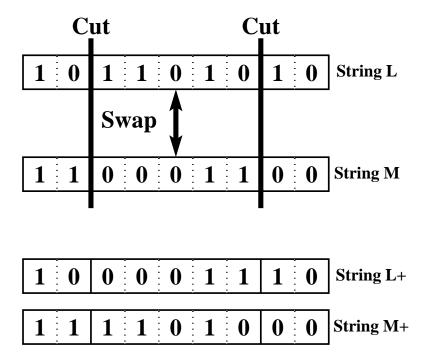

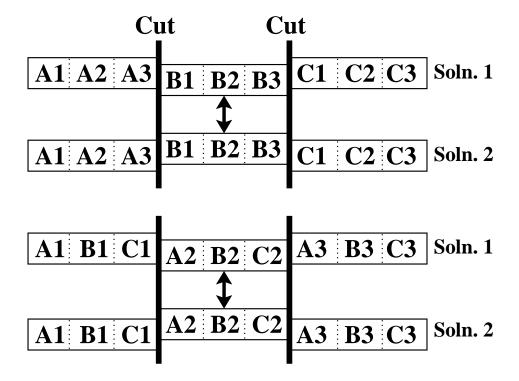

In a conventional genetic algorithm, a solution is represented by a one-dimensional array, or *string*, of values. All changes to strings are made with two operators: mutation and crossover. *Mutation* randomly changes part of a solution's string. *Crossover* swaps portions of different solutions. Two different types of crossover are commonly used: one-cut and two-cut. In one-cut crossover, a pair of strings is selected and the portions to the left of a randomly selected offset into the strings are swapped. In two-cut crossover, a pair of strings is selected and the portions between two randomly selected offsets into the strings are swapped. Figure 4.4 shows an example of two-cut string crossover. In this illustration, crossover occurs between strings L and M. Two-cuts are made and the portions of L and M between these cuts are swapped, producing strings L+ and M+. Crossover is the operator that gives genetic algorithms their strength; it allows different solutions to share information with each other.

An *independent sub-solution* is a portion of a solution for which the optimal configuration is not influenced by the configurations of other sub-solutions. It is important that the string encoding used to represent a solution maintain *locality*, i.e., it is important for data representing each independent sub-solution to be located contiguously, instead of

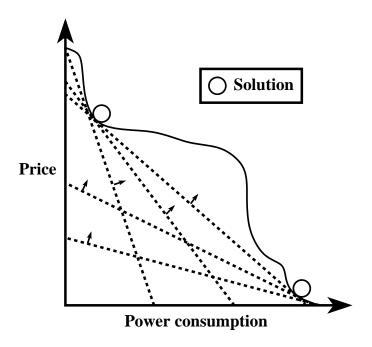

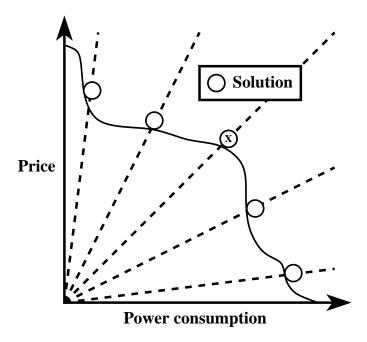

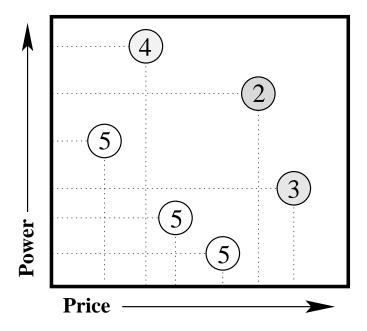

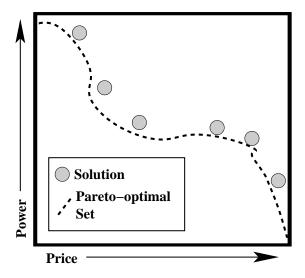

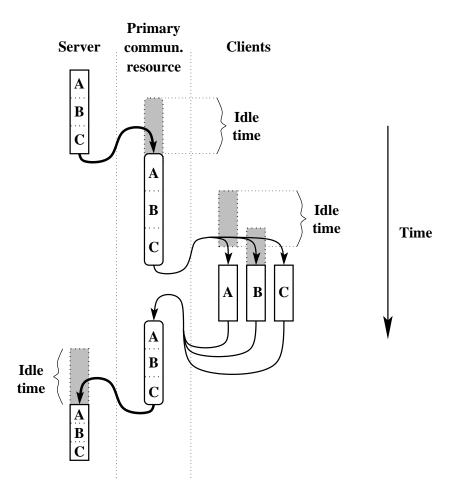

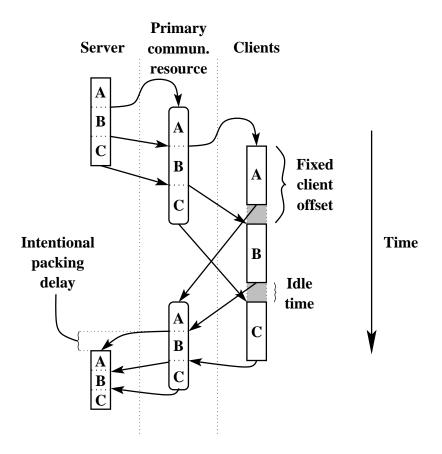

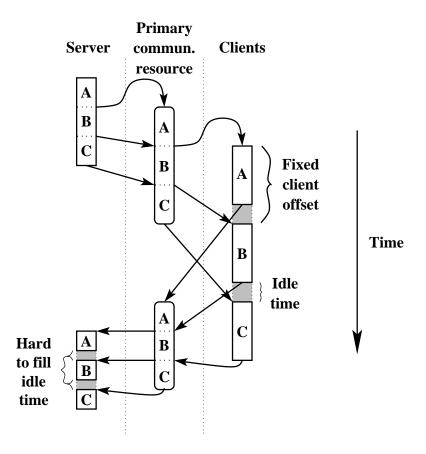

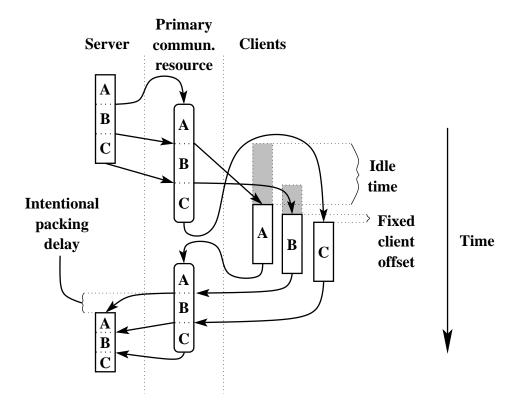

Figure 4.4: Crossover.