## REAL-TIME SYSTEM DESIGN UNDER PHYSICAL AND RESOURCE CONSTRAINTS

A Dissertation

Submitted to the Graduate School of the University of Notre Dame in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Thidapat Chantem

Xiaobo Hu, Director

Graduate Program in Computer Science and Engineering Notre Dame, Indiana April 2011 © Copyright by Thidapat Chantem 2011 All Rights Reserved

## REAL-TIME SYSTEM DESIGN UNDER PHYSICAL AND RESOURCE CONSTRAINTS

#### Abstract

#### by

#### Thidapat Chantem

This dissertation presents several design techniques for resource-constrained, dependable embedded real-time systems, which can be found everywhere from cellular phones to automotive electronic systems to medical devices. Specifically, three important challenges in embedded real-time system design are identified and addressed: temporal overloads, energy concerns, and temperature problem.

Due to cost constraints, as well as our inability to foresee worst-case operating scenarios, many systems are designed based on average-case scenarios and must provide graceful performance degradation during occasional system overloads. In this dissertation, we focus on two types of overloads: processor overloads and network overloads. Processor overload occurs because of user's inputs or external conditions. We present robust algorithms that allow the system to quickly handle different operating scenarios without requiring advanced knowledge of the situations based on optimization theory. As a result, fewer resources are needed to deliver expected performance.

As for network overloads, which can often occur especially now that most electronic devices have wireless capability, we discuss an energy-aware integrated framework that allows for the processor and network card to work together to transmit the most important information first. This framework is robust against rapid changes in network conditions, guarantees the transmission of the most important set of information, and allows the system to save energy.

Finally, as device sizes continue to shrink, physical constraints such as system temperature have become a main concern. High temperature can severely reduce both performance and system lifetime. We first present an optimal voltage selection policy to maximize computation without exceeding the temperature threshold. We then present a method to minimize the peak temperature of a hard real-time system running on multi-core architectures that help to avoid deadline misses at run time. To my parents, who have always insisted that education is their only lasting gift to me.

## CONTENTS

| FIGUR | ES       | vii                                                                                                                                           |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE | S        | x                                                                                                                                             |

| ACKNO | OWLED    | GMENTS                                                                                                                                        |

| СНАРТ | 'ER 1: 1 | INTRODUCTION                                                                                                                                  |

| 1.1   | Overvi   | ew of Real-Time Systems                                                                                                                       |

| 1.2   |          | Challenges in Real-Time Systems                                                                                                               |

|       | 1.2.1    | Temporal Overload Conditions                                                                                                                  |

|       |          | 1.2.1.1 Processing Overloads                                                                                                                  |

|       |          | 1.2.1.2 Network Overloads                                                                                                                     |

|       | 1.2.2    | Power/Energy Concerns                                                                                                                         |

|       | 1.2.3    | Temperature Problem                                                                                                                           |

| 1.3   | Main (   | Contributions and Organization                                                                                                                |

| СНАРТ | 'ER 2:   | PERIOD AND DEADLINE SELECTION FOR SCHEDU-                                                                                                     |

|       |          | IN REAL-TIME SYSTEMS                                                                                                                          |

| 2.1   | Introdu  | uction $\ldots \ldots \ldots$ |

|       | 2.1.1    | Problem Overview                                                                                                                              |

|       | 2.1.2    | Related Work                                                                                                                                  |

|       | 2.1.3    | Contributions                                                                                                                                 |

|       | 2.1.4    | Organization                                                                                                                                  |

| 2.2   | System   | Model and Problem Definition                                                                                                                  |

|       | 2.2.1    | Task Model         15                                                                                                                         |

|       | 2.2.2    | Schedulability Tests                                                                                                                          |

|       | 2.2.3    | Problem Definition                                                                                                                            |

| 2.3   | Motiva   |                                                                                                                                               |

| 2.4   | Period   | and Deadline Selection Heuristic                                                                                                              |

|       | 2.4.1    | Identifying Infeasible Regions Using Simple Tests 22                                                                                          |

|       | 2.4.2    | Efficiently Conducting the Search Process                                                                                                     |

| 2.5   | Experimental Results                                                                                                                                       | 4 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|       | 2.5.1 Experimental Setup                                                                                                                                   | 5 |

|       | 2.5.2 Heuristic Performance                                                                                                                                | 7 |

| 2.6   |                                                                                                                                                            | 8 |

|       |                                                                                                                                                            |   |

| CHAPT | ΓER 3: A HOLISTIC SCHEDULING FRAMEWORK FOR ENERGY-                                                                                                         |   |

| CON   | NSTRAINED WIRELESS REAL-TIME APPLICATIONS 4                                                                                                                | 0 |

| 3.1   | Introduction                                                                                                                                               | 0 |

|       | 3.1.1 Problem Overview                                                                                                                                     | 1 |

|       | 3.1.2 Related Work                                                                                                                                         | 2 |

|       | 3.1.3 Contributions                                                                                                                                        | 3 |

|       | 3.1.4 Organization                                                                                                                                         | 4 |

| 3.2   | Preliminaries                                                                                                                                              | 4 |

|       | 3.2.1 Task and Packet Model                                                                                                                                | 4 |

|       | 3.2.2 Hardware and Power Model                                                                                                                             | 5 |

|       | 3.2.3 Motivation                                                                                                                                           | 7 |

| 3.3   |                                                                                                                                                            | 2 |

| 3.4   |                                                                                                                                                            | 4 |

| 3.5   |                                                                                                                                                            | 2 |

|       | 3.5.1 Uniprocessors                                                                                                                                        | 2 |

|       |                                                                                                                                                            | 4 |

| 3.6   | *                                                                                                                                                          | 6 |

|       | 3.6.1 Extensions to Task and Packet Models 6                                                                                                               | 6 |

|       | 3.6.2 Leakage Considerations                                                                                                                               | 7 |

|       | 3.6.3 Applicable Network Types                                                                                                                             | 8 |

| 3.7   | Evaluation                                                                                                                                                 | 8 |

|       | 3.7.1 Pre-Scheduling Packets                                                                                                                               | 8 |

|       |                                                                                                                                                            | 0 |

|       | 3.7.3 Entire Framework                                                                                                                                     | 4 |

| 3.8   | Summary                                                                                                                                                    | 0 |

|       |                                                                                                                                                            |   |

| СНАРЛ | ΓER 4: ONLINE WORK MAXIMIZATION UNDER A PEAK TEM-                                                                                                          |   |

| PEF   | RATURE CONSTRAINT                                                                                                                                          | 2 |

| 4.1   | Introduction                                                                                                                                               | 2 |

|       | 4.1.1 Problem Overview                                                                                                                                     | 3 |

|       | 4.1.2 Related Work $\ldots \ldots \ldots$  | 4 |

|       | 4.1.3 Contributions $\ldots \ldots \ldots$ | 6 |

|       | 4.1.4 Organization $\ldots \ldots \ldots$  | 7 |

| 4.2   |                                                                                                                                                            | 7 |

|       | 4.2.1 Task and Processor Models                                                                                                                            | 7 |

|       | 4.2.2 Problem Definition                                                                                                                                   | 9 |

| 4.3  |                                    |                                                           |     |  |  |  |

|------|------------------------------------|-----------------------------------------------------------|-----|--|--|--|

|      | 00                                 | gible Transition Overhead                                 | 89  |  |  |  |

| 4.4  | Non-Negligible Transition Overhead |                                                           |     |  |  |  |

| 4.5  |                                    |                                                           |     |  |  |  |

| 4.0  | Simulation Results                 |                                                           |     |  |  |  |

| 4.0  | 4.6.1                              | Simulation Setup                                          | 108 |  |  |  |

|      | 4.0.1<br>4.6.2                     | Performance Comparison of Different Speed Selection Poli- | 108 |  |  |  |

|      | 4.0.2                              | cies with Negligible Transition Overhead                  | 110 |  |  |  |

|      | 4.6.3                              | Performance Comparison of Different Speed Selection Poli- | 110 |  |  |  |

|      | 4.0.5                              | cies with Non-Negligible Transition Overhead              | 112 |  |  |  |

| 4.7  | Summ                               | ary                                                       | 112 |  |  |  |

| 4.1  | Sum                                | Iary                                                      | 114 |  |  |  |

| CHAP | ΓER 5:                             | TEMPERATURE-AWARE SCHEDULING AND ASSIGN-                  |     |  |  |  |

| ME   | NT FO                              | R HARD REAL-TIME APPLICATIONS ON MPSOCS                   | 119 |  |  |  |

| 5.1  | Introd                             | luction                                                   | 119 |  |  |  |

|      | 5.1.1                              | Problem Overview                                          | 120 |  |  |  |

|      | 5.1.2                              | Related Work                                              | 122 |  |  |  |

|      | 5.1.3                              | Contributions                                             | 125 |  |  |  |

|      | 5.1.4                              | Organization                                              | 125 |  |  |  |

| 5.2  | Syster                             | m Model and Problem Definition                            | 126 |  |  |  |

|      | 5.2.1                              | Task Model                                                | 126 |  |  |  |

|      | 5.2.2                              | Thermal Model                                             | 127 |  |  |  |

|      | 5.2.3                              | Problem Definition                                        | 131 |  |  |  |

| 5.3  | Motiv                              | ations                                                    | 131 |  |  |  |

| 5.4  | MILP                               | -based Approach                                           | 134 |  |  |  |

|      | 5.4.1                              | MILP Formulation                                          | 135 |  |  |  |

|      | 5.4.2                              | Modeling Power Consumption                                | 140 |  |  |  |

|      | 5.4.3                              | Incorporating Dynamic Voltage Scaling                     | 142 |  |  |  |

|      | 5.4.4                              | Using Finer-Grained Thermal Model                         | 143 |  |  |  |

|      | 5.4.5                              | Modeling Inter-Task Communication                         | 144 |  |  |  |

|      | 5.4.6                              | Limitations of MILP-based Approach                        | 144 |  |  |  |

| 5.5  | Sched                              | uling Heuristic Framework                                 | 145 |  |  |  |

|      | 5.5.1                              | Steady-State Analysis Based Heuristic                     | 147 |  |  |  |

|      | 5.5.2                              | Transient Analysis Based Heuristic                        | 148 |  |  |  |

| 5.6  | Delay                              | Insertion                                                 | 148 |  |  |  |

| 5.7  | Exper                              | imental Results                                           | 152 |  |  |  |

|      | 5.7.1                              | Experimental Setup                                        | 152 |  |  |  |

|      | 5.7.2                              | MILP Formulation Performance                              | 154 |  |  |  |

|      | 5.7.3                              | Performance of Steady-State Analysis Based Heuristic      | 162 |  |  |  |

|      | 5.7.4                              | Performance of Transient Analysis Based Heuristic         | 164 |  |  |  |

| 5.7.5 Performance of Transient Analysis Based Heuristic with De- |     |

|------------------------------------------------------------------|-----|

| lay Insertions                                                   | 165 |

| 5.8 Summary                                                      | 166 |

| CHAPTER 6: CONCLUSIONS                                           | 169 |

| 6.1 Summary                                                      | 169 |

| *                                                                | 170 |

| 6.2.1 Designing for High-Performance and Dependability on Mul-   |     |

| ticore and Many-Core Systems                                     | 170 |

| 6.2.2 Designing Highly-Adaptive, Highly-Reconfigurable Cyber-    |     |

| Physical Systems (CPS)                                           | 170 |

|                                                                  |     |

| BIBLIOGRAPHY                                                     | 172 |

## FIGURES

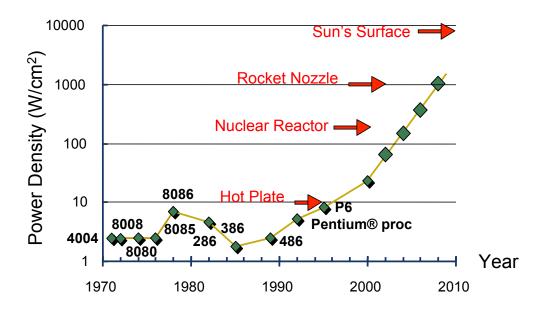

| 1.1  | Power density trends (adapted from Rabaey [86])                                                                                                                                                                                                                                                                                 |    |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

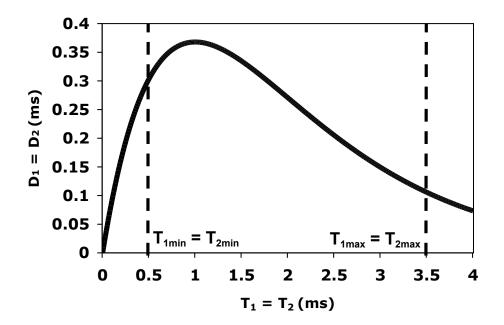

| 2.1  | Task deadlines in milliseconds as a function of task periods, also in milliseconds. The area inside the vertical dotted lines denotes the acceptable period ranges for the task set in Table 2.1.                                                                                                                               | 21 |  |  |  |

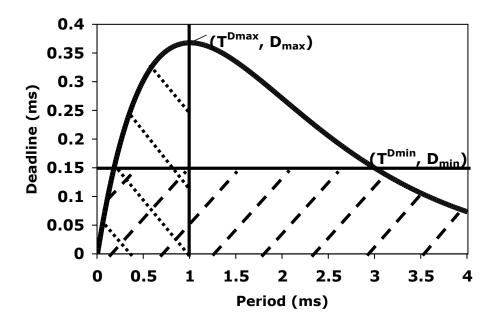

| 2.2  | Task deadline in milliseconds as a function of task periods, also in<br>milliseconds. The left-slanted and right-slanted areas denote infea-<br>sible period and deadline combinations. The unpatterned region<br>represents possibly feasible period and deadline combinations and<br>is where the search process is conducted | 24 |  |  |  |

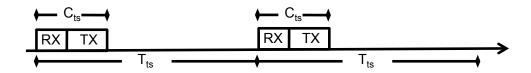

| 3.1  | Network communication model.                                                                                                                                                                                                                                                                                                    | 47 |  |  |  |

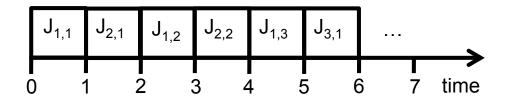

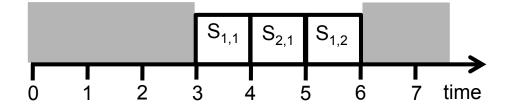

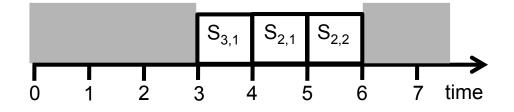

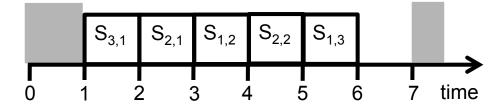

| 3.2  | EDF job schedule.                                                                                                                                                                                                                                                                                                               | 48 |  |  |  |

| 3.3  | EDF packet schedule.                                                                                                                                                                                                                                                                                                            | 49 |  |  |  |

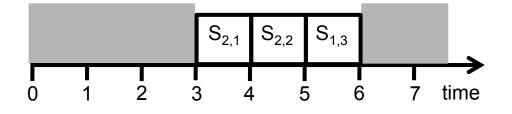

| 3.4  | Importance-based packet schedule.                                                                                                                                                                                                                                                                                               | 50 |  |  |  |

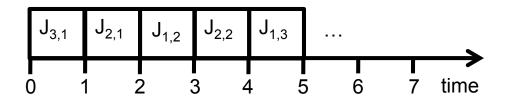

| 3.5  | Value-based job schedule.                                                                                                                                                                                                                                                                                                       | 50 |  |  |  |

| 3.6  | Resulting packet schedule.                                                                                                                                                                                                                                                                                                      | 51 |  |  |  |

| 3.7  | Resulting packet schedule with longer network access time                                                                                                                                                                                                                                                                       | 51 |  |  |  |

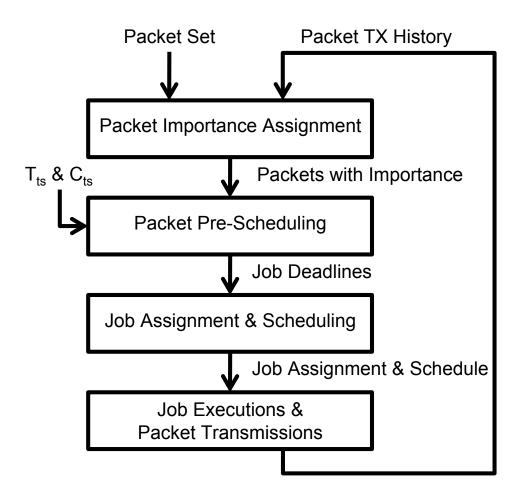

| 3.8  | Proposed framework.                                                                                                                                                                                                                                                                                                             | 53 |  |  |  |

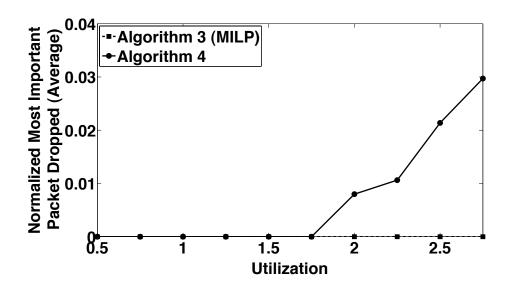

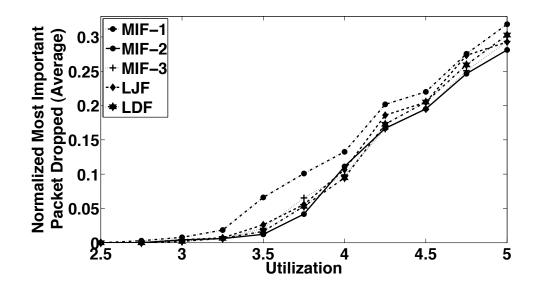

| 3.9  | Value of most important packet dropped from different packet schedul-                                                                                                                                                                                                                                                           |    |  |  |  |

|      | ing algorithms.                                                                                                                                                                                                                                                                                                                 | 70 |  |  |  |

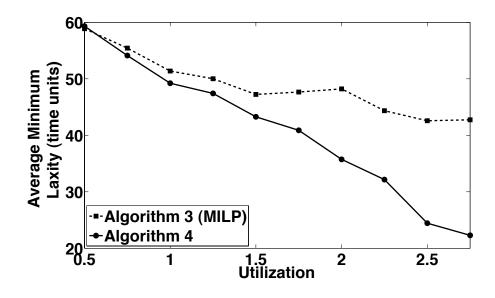

| 3.10 | Minimum job laxity of different packet scheduling algorithms                                                                                                                                                                                                                                                                    | 71 |  |  |  |

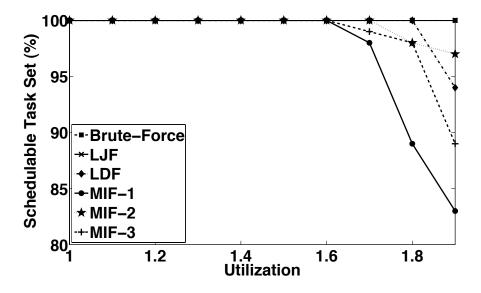

| 3.11 | Number of dropped jobs by different job assignment algorithms for<br>the two-core case                                                                                                                                                                                                                                          | 72 |  |  |  |

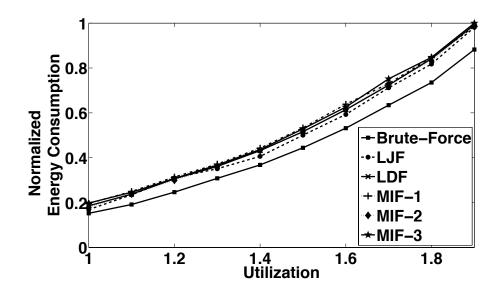

| 3.12 | Energy consumption of different job assignment algorithms for the two-core case.                                                                                                                                                                                                                                                | 73 |  |  |  |

| 3.13 | Value of most important job dropped from different job assignment algorithms for the four-core case.                                                                                                                                                                                                                            | 74 |  |  |  |

| 3.14 | Energy consumption of different job assignment algorithms for the four-core case                                                                                                                                                                                                                             | 75      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

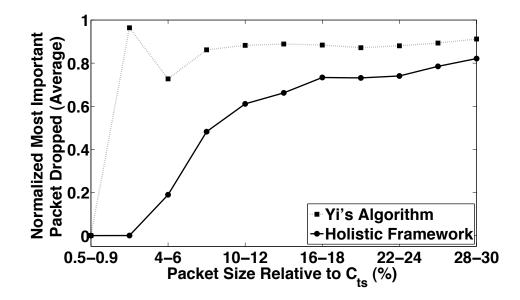

| 3.15 | Comparison to the work in [114] in terms of minimizing the maxi-<br>mum importance of dropped packets                                                                                                                                                                                                        | 76      |

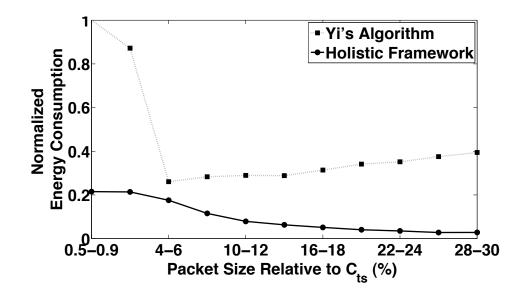

| 3.16 | Comparison to the work in [114] in terms of energy consumption.                                                                                                                                                                                                                                              | 77      |

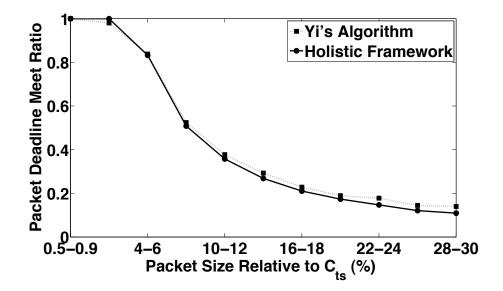

| 3.17 | Comparison to the work in [114] in terms of packet deadline meet ratio.                                                                                                                                                                                                                                      | 78      |

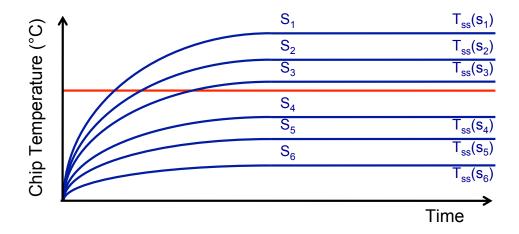

| 4.1  | The RC curves showing chip temperatures as a function of time due to different speed levels                                                                                                                                                                                                                  | 89      |

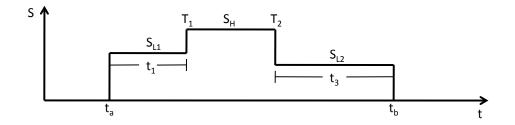

| 4.2  | Graphical depiction of the speed schedule in the statement of Lemma $$                                                                                                                                                                                                                                       | 4.1. 91 |

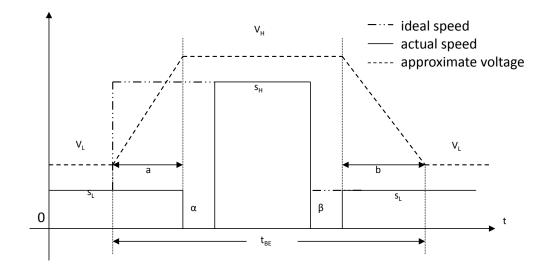

| 4.3  | Waveforms of speed and voltage levels for two transitions, where $S$ and $V$ denote speed and voltage, respectively. During transitions, the voltage is increased or decreased in a small step size and thus there is a delay associated with each transition                                                | 105     |

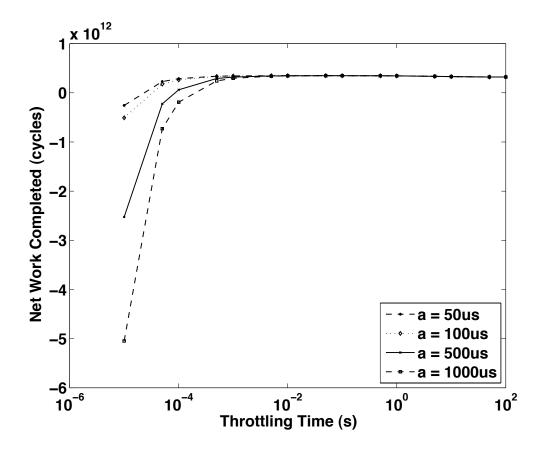

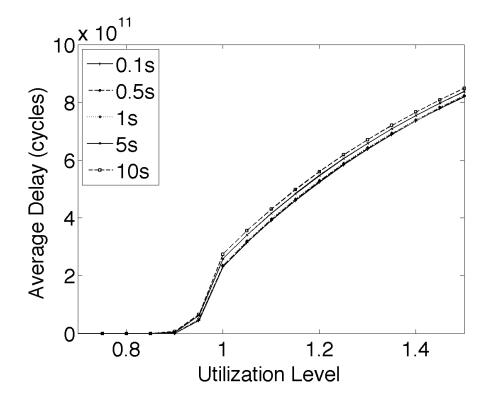

| 4.4  | Net number of cycles completed as a function of throttling time,<br>where $a$ is the voltage changing time from the low speed level to<br>the high speed level. With non-negligible transition overhead, in-<br>finitesimally small throttling time does not lead to the maximum<br>amount of work completed | 106     |

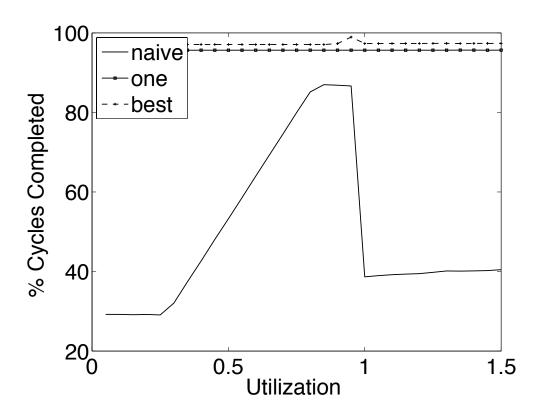

| 4.5  | Average number of cycles completed $(\%)$ for different speed selection policies with throttling time of 10 s                                                                                                                                                                                                | 112     |

| 4.6  | Average number of deadline misses for different speed selection policies with throttling time of 10 s                                                                                                                                                                                                        | 113     |

| 4.7  | Average deadline miss delay (cycles) for different speed selection policies with throttling time of 10 s                                                                                                                                                                                                     | 114     |

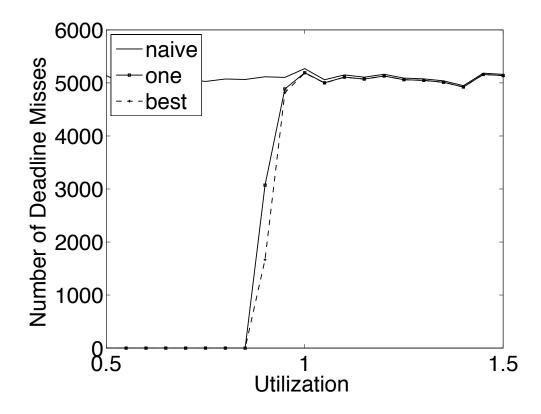

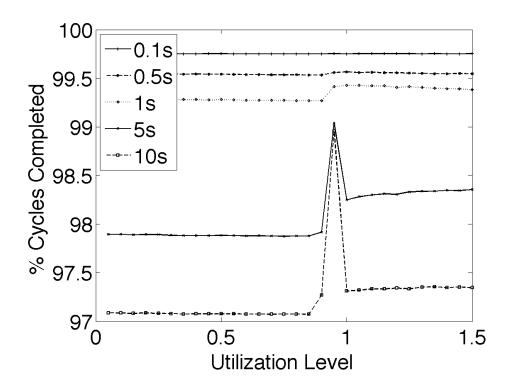

| 4.8  | Average number of cycles completed (%) for different throttling times for the best speed selection policy.                                                                                                                                                                                                   | 115     |

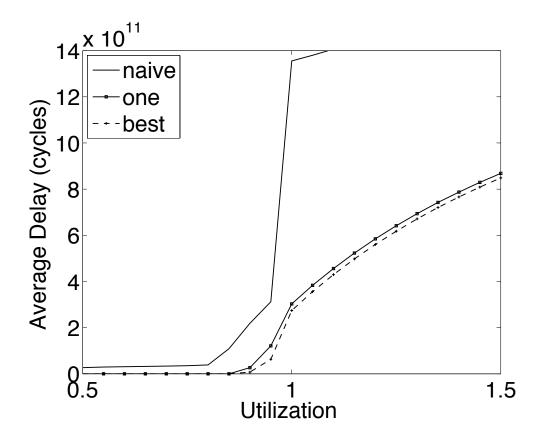

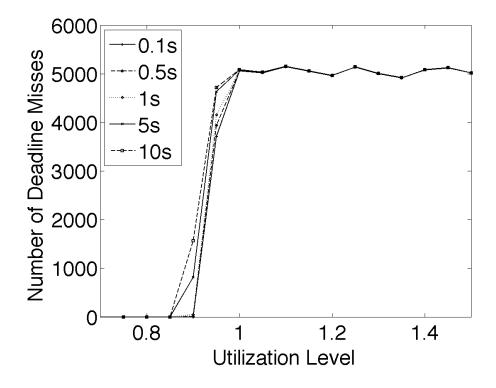

| 4.9  | Average number of deadline misses for different throttling times for<br>the best speed selection policy                                                                                                                                                                                                      | 116     |

| 4.10 | Average deadline miss delay (cycles) for different throttling times for the best speed selection policy.                                                                                                                                                                                                     | 117     |

| 4.11 | Average number of cycles completed as a function of throttling time<br>when transition overhead is considered. A very small throttling<br>time can result in a negative net number of cycles completed                                                                                                       | 118     |

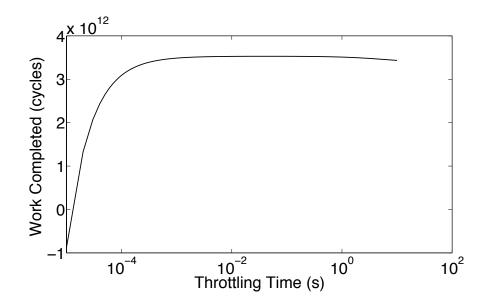

| 5.1 | Equivalent circuit diagram of the thermal model. In this example,<br>core $m$ is connected to its neighboring core $n$ and is under heatsink<br>element $h$ . The power consumption and capacitance of core $m$<br>are represented by the current source $P_m$ and the capacitor $C(m)$ ,<br>respectively. The heatsink element $h$ is connected to other neigh-<br>boring heatsink elements, a capacitor, as well as to the ambient,<br>which is denoted by the voltage source $T_A$ | 129 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

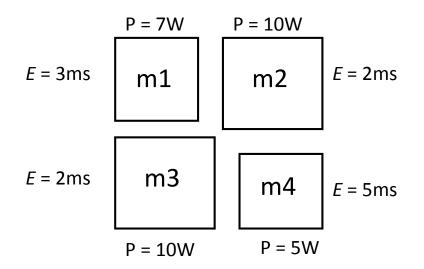

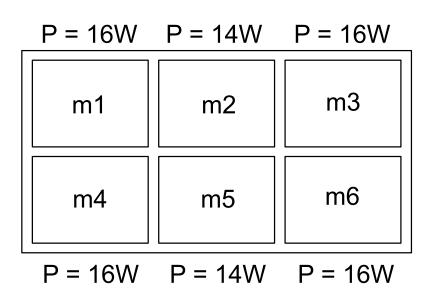

| 5.2 | Floorplan for the motivating example in Section 5.3, where both task execution times $(E)$ and power consumption $(P)$ are shown for each core.                                                                                                                                                                                                                                                                                                                                       | 132 |

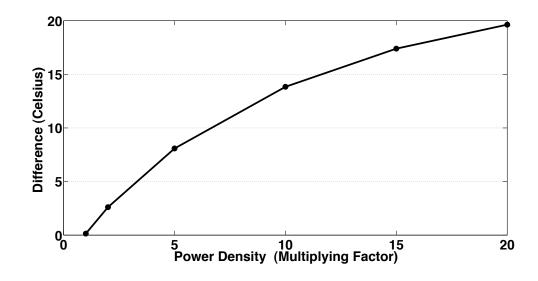

| 5.3 | Differences in peak temperatures between energy minimization and<br>peak temperature approaches. The x-axis shows the values (i.e.,<br>multiplying factors) that were multiplied to the original chip power<br>density. In this example, peak power minimization yields the same<br>peak temperature as energy minimization                                                                                                                                                           | 133 |

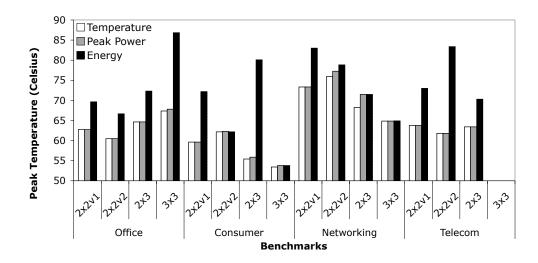

| 5.4 | Peak temperature minimization vs. energy and peak power mini-<br>mization. The results were obtained by solving the MILPs directly.<br>Clearly, energy minimization is not effective in reducing the chip<br>peak temperature.                                                                                                                                                                                                                                                        | 157 |

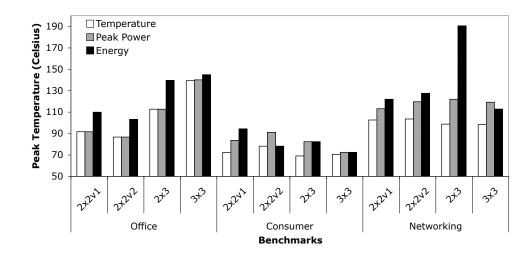

| 5.5 | Peak temperature minimization vs. energy and peak power mini-<br>mization for higher power density chips. The results were obtained<br>by solving the MILPs directly. Here, as the chip power density<br>increases, spatial thermal variation becomes significant and peak<br>power minimization is not effective in reducing the chip peak tem-<br>perature                                                                                                                          | 158 |

| 5.6 | An example 2×3 floorplan with associated power consumption for<br>each core                                                                                                                                                                                                                                                                                                                                                                                                           | 159 |

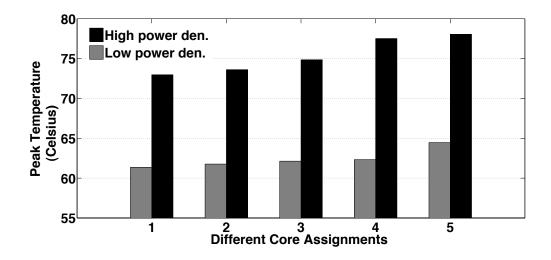

| 5.7 | Bar plot illustrating the resultant peak temperatures for the dif-<br>ferent core assignments that can be obtained given the same peak<br>power. The maximum difference in peak temperatures is higher<br>than 5 °C for the Networking benchmark, which contains only 12<br>tasks                                                                                                                                                                                                     | 161 |

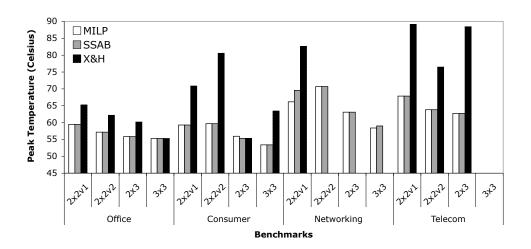

| 5.8 | Performance comparison between the steady-state analysis based heuristics (based on HotSpot), the MILP, and Xie and Hung's heuristic [111]                                                                                                                                                                                                                                                                                                                                            | 162 |

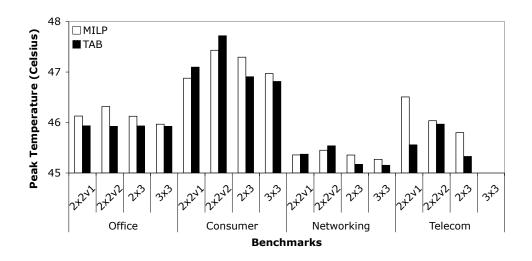

| 5.9 | Performance comparison between the transient analysis based heuris-<br>tics (based on HotSpot) and the MILP. Here, the MILP sometimes<br>results in a higher peak temperature because it uses the steady-<br>state thermal analysis, which ignores dynamic thermal effects                                                                                                                                                                                                            | 164 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ~ - |

## TABLES

| 2.1 | TASK SET FOR MOTIVATING EXAMPLE ILLUSTRATING THE<br>IMPORTANCE OF THE PERIOD AND DEADLINE SELECTION<br>PROBLEM | 20  |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | PERFORMANCE COMPARISON: PERIOD AND DEADLINE<br>SELECTION HEURISTIC VS. FIXED DEADLINE TECHNIQUE                | 38  |

| 2.3 | PERIOD AND DEADLINE SELECTION HEURISTIC: NUMBER<br>OF ITERATIONS REQUIRED                                      | 39  |

| 3.1 | EXAMPLE TASK SET                                                                                               | 48  |

| 3.2 | ADDITIONAL PARAMETERS FOR SIMULATIONS OVER SEV-<br>ERAL TIME INTERVALS                                         | 80  |

| 3.3 | RESULTS FOR SIMULATIONS OVER SEVERAL TIME INTER-<br>VALS                                                       | 80  |

| 5.1 | FLOORPLAN CONFIGURATIONS                                                                                       | 155 |

| 5.2 | CORE NAMES                                                                                                     | 156 |

| 5.3 | IMPROVEMENTS IN CHIP PEAK TEMPERATURES WHEN iTAB (WITH DELAY INSERTION) IS USED INSTEAD OF TAB                 | 168 |

|     |                                                                                                                |     |

## ACKNOWLEDGMENTS

This dissertation is a result of many years of mentoring and much patience on the part of my advisor, Dr. Sharon Hu. From the day you took me on as a brand new graduate student to today, you have always made time for me and have taught me the value of hard work and persistence. Thank you for making me into the researcher I am today.

To Dr. Robert Dick, I have many reasons to thank you but I am especially grateful for your philosophy in not only producing high quality products but also that the process matters. Because of your high standards, I have continued (and will continue) to improve.

Dr. Michael Lemmon, thank you for your wisdom, especially during my early years at Notre Dame. You were instrumental in my growth as a researcher and I have fond memories of our discussions. Your sense of humor is simply refreshing.

To Dr. Christian Poellabauer, it never ceases to amaze me how you always give incredibly insightful suggestions and ask important (and often overlooked) questions in the most casual way possible. Thank you for keeping me grounded and for reminding me of the true motivations behind my research.

I would like to thank Dr. Liqiang Zhang not only for lending me his expertise in networking, but also for his helpful suggestions during our discussions on my career path and employment search.

The work in this dissertation is supported in part by NSF under grant numbers

CNS-0347941, CNS-0404341, CNS-0410771, CCF-0444405, IIS-0536994, CCF-0702705, CCF-0702761, CNS-0720691, CNS-0834180, CNS-0834230, CCF-0964763, and CNS07-20457, and in part by SRC under grant numbers 2007-TJ-1589 and 2007-HJ-1593. In addition, I gratefully acknowledge the support of the U.S. Department of Education through a GAANN Fellowship (award P200A090044).

I would like to thank my early mentors, Dr. Manimaran Govindarasu and Dr. Mani Mina, for their guidance during my tenure at Iowa State and thereafter. You always have time for me and I feel so privileged. A heartfelt thank goes to all my teachers and professors without whom I would not be here today.

Big thanks are due to my colleagues whom I have worked with or received help from (in no particular order): Dr. Bren Mochocki, Dr. Xiaofeng Wang, Jun Yi, Yun Xiang, Shengyan Hong, David Bild, Xi Chen, Lide Zhang, and Dinesh Rajan.

I am indebted to the support staff in the department. Thank you Curt, M.D., Joyce, Ginny, and Diane.

I have been so fortunate to have such a strong support system, which I find in my family and friends. Thank you Moms and Dads, Grandmas, and Josh. I love you all. To my sister Kate, who takes such good care of me I feel like I am the little sister sometimes, thank you and I love you. I also owe a big thank to all my friends around the world.

Finally, I would like to thank my husband, Ryan, especially for having driven at least 62,000 miles over the years to see me, for letting me make up food menus and cooking the meals without complaints, and, quite simply, for being just the way he is.

## CHAPTER 1

## INTRODUCTION

This chapter introduces readers to some basic concepts in real-time systems as well as important challenges in designing such systems due to physical and resource constraints (temporal overloads, energy concerns, and temperature problem). The chapter concludes with an outline of the main contributions in this dissertation.

### 1.1 Overview of Real-Time Systems

In a general-purpose computing system, the primary performance requirement is correct functionality. For instance, if a user wishes to obtain a list of the first thousand prime numbers, a system meets a functionality requirement if it correctly outputs such a list to the user.

In a real-time system, which can be thought of as a special case of generalpurpose computing systems, timeliness, along with correct functionality, is also a requisite. Consider, for example, a train that is attempting to make an emergency stop within 5 seconds. The fact that the train does stop demonstrates that it performs its task correctly. However, the completion of this task is not useful, to say the least, if the train does not stop on time (i.e., within 5 seconds). A train that does is said to meet the timeliness requirement.

There are three classes of real-time systems: hard, firm, and soft. In a hard real-time system (e.g., the braking system of our example train), missing a deadline could result in catastrophic consequences. For such systems, offline analysis and hardware redundancy are often used to guarantee performance and timing requirements.

As for firm real-time systems, a few deadline misses are not detrimental to the overall performance of the system, but tasks that complete their executions after their deadlines are of no or even negative value. For instance, an out-of-date sample may trigger a control command that worsens the state of the system.

Finally, in a soft real-time system, deadlines may be missed or tasks may be completed late, though as many deadlines should be met as possible to maximize the performance of the entire system. For example, a user who watched a video clip online may rate his or her experience as mostly positive if he or she noticed only a few frame freezes during the entire session. The worst consequence that could result from an extremely unhappy user might be loss of business.

Regardless of the class of the real-time system under consideration, a real-time task is usually associated with worst-case, average-case, and best-case execution times. In this dissertation, we focus on tasks that need to be executed in a periodic manner. An example application might be a control task that needs to sample the water level in a pipe every 10 ms. For periodic real-time systems, task deadlines may be implicit (for the same control task just mentioned, the deadlines would be 10, 20, 30, ... ms), or explicit (e.g., a control task that must execute every 10 ms with a deadline of 5 ms, which means that the deadlines are 5, 15, 25, ... ms.

While task worst-case execution times are usually well-defined given that the physical characteristics of the system are known, acceptable task periods and deadlines may not be a fixed value. Referring back to our water level sampling example, the overall performance of the system may in fact be acceptable if a sample is taken every  $7 \,\mathrm{ms}$  to  $15 \,\mathrm{ms}$ .

#### 1.2 Design Challenges in Real-Time Systems

This dissertation tackles three important challenges in designing real-time systems: temporal overloads, power/energy concerns, and temperature problem. Each of these challenges is briefly discussed below.

#### 1.2.1 Temporal Overload Conditions

For the purpose of this dissertation, we focus on two different types of temporal overloads: processing overloads and network overloads.

### 1.2.1.1 Processing Overloads

A real-time system is said to experience a processing overload if the computation demand exceeds the available computational resources. Consider, for example, the city sewer control system, which is responsible for drainage and waste management. Said system consists of several sensors and actuators, which are spread throughout the city and are controlled by a central computer. The sensors report, among other things, the level of water in their respective pipes, while the actuators may be used to control the flow rate of water in those pipes. Suppose now that part of the city has been experiencing a heavy rain. Since the water level in some of the pipes may be increasing at an alarming rate, we may need to sample the state of the pipes more frequently and send control commands to the relevant actuators more often to avoid flooding. Because of these new requirements, the city sewer control system is temporally under an overload situation, as more attention needs to be paid to the part of the city receiving heavy rainfall. For more information regarding work in control systems on combined sewer overflow (CSO) events, the reader is referred to Ruggaber et al. [90] and Wan and Lemmon [103].

While temporal processing overload conditions can be alleviated to some extent using hardware overprovisioning, this solution is costly and wastes precious resources, especially since overloads tend to rarely occur and the average-case system utilization may be quite low. Additionally, in real systems, many factors are at work and it may be difficult, if not impossible, to predict the worst-case scenarios. For these reasons, many systems are designed based on the average operating scenarios and efficient run-time mechanisms to manage occasional overloads must be in place to rapidly solve the problem. An example overload management mechanism to the city sewer system may be to temporarily reduce the sampling (actuating) rate of sensors (actuators) that are not located in the part of the city receiving heavy rainfall in order to allocate more resources to managing the critical area in the city.

## 1.2.1.2 Network Overloads

A network overload is similar to a processing overload, except that network communications, and not the processing power, are the bottleneck. As most electronic devices now have wireless capability, network overloads occur more frequently, especially in sensor network applications where each node may need to transmit a large amount of data. During a network overload, only a limited amount of information can be transmitted and it is crucial in terms of performance maximization to judiciously select which information to send. For example, in a surveillance system used for intrusion detection, a video frame showing a potential intruder should take precedence over other information.

#### 1.2.2 Power/Energy Concerns

As device size continues to shrink, a relatively larger number of transistors can be packed into a small area, causing an exponential increase in chip power density. Figure 1.1 shows the projected chip power density as a function of years. High power density results in high temperature (we will discuss temperature problem in more detail in the next section) and has several implications.

Figure 1.1. Power density trends (adapted from Rabaey [86])

1. In data centers, which can be considered soft real-time systems since response time is usually a main performance metric, about half of the power is used for cooling [37]. In 2005, about 1.2% of all U.S. electricity use went towards total data center power and cost about \$4.5 billion [37]. These numbers doubled from 2000 to 2005 and the trend is simply unsustainable [37].

- 2. As wireless nodes become common in a variety of applications, their operating lifetimes are now an important performance metric. Although battery technology has advanced over the years, the improvement remains modest and system designers are expected to use energy-aware methods to increase battery life without sacrificing performance.

- 3. Lastly, static or leakage power increases exponentially as supply voltage and threshold voltage are scaled down. According to Borkar, leakage power now makes up about 50% of total power consumption [14].

The high cooling cost and exponential increase in leakage power, as well as wireless and mobility requirements lead to an ever increasing need in designing power/energy-aware systems. Despite the large amount of existing literature on this topic, there are still many challenges to be addressed, especially as multicore systems with networking capabilities become more popular in a wide variety of real-time applications.

### 1.2.3 Temperature Problem

To achieve higher performance and better power efficiently, computer architects have proposed multiprocessor system-on-chips (MPSoCs) as an alternative to and improvement on uniprocessor architectures. However, as a result of shrinking device size, increasing transistor counts, and aggressive frequency scaling, MPSoCs often have high power density and temperature, which causes significant reliability concerns. In fact, a 10–15 °C difference in operating temperature can result in a  $2\times$  difference in the lifespan of a device [102]. Even when high temperature does not immediately lead to permanent failures, it can cause increased interconnect latency and reduction of charge carrier mobility in transistors, which degrade performance. More importantly, high temperature leads to higher temperaturedependent leakage power, which in turns increases power consumption and hence temperature. Clearly, this cycle of dependency must to be broken.

A solution to the temperature problem in MPSoCs would be to design packages and cooling solutions that can handle worst-case thermal profiles. However, this solution is extremely expensive, as the cooling cost increases super-linearly in power consumption [43]. We have also discussed the high cost of cooling data centers in the previous section.

To reduce temperature, most modern processors use hardware throttling to control chip temperature at run time. Throttling is automatically activated when the chip temperature exceeds some prespecified threshold temperature. In addition to saving energy, techniques such as dynamic voltage and frequency scaling (DVFS) can also help to reduce temperature. The most difficult challenge that arises in the design of temperature-constrained real-time system is that processor throttling can cause real-time deadlines to be missed and therefore specific design techniques targeted at real-time systems must be used.

#### 1.3 Main Contributions and Organization

This dissertation extends state-of-the-art techniques on managing physical and resource constrains in real-time systems in several directions.

(1). We present an efficient online technique to solve the temporal processing overload problem for a more general set of real-time tasks (Chapter 2). Prior work assumes task deadlines are fixed and independent of task periods. However, in many control applications, the relationship between task periods and task deadlines is tightly coupled. We show in this chapter that by taking this period-deadline relationship into account, at least 74% of the task sets previously thought to be infeasible are in fact schedulable. An immediate consequence of this work is that fewer resources are needed to handle temporal processing overloads.

- (2). We propose an energy-aware adaptive framework to address network overloads (Chapter 3). Existing work either do not consider job scheduling when performing packet scheduling or vice versa. As a result, packets that are meant to be transmitted may in fact miss their deadlines, degrading performance. In this chapter, we show that using an integrated, importance-based job and packet scheduling framework, system performance doubles while processing energy consumption is significantly reduced.

- (3). We provide an optimal DVFS speed selection policy to maximize the work completed for temperature-constrained soft real-time systems (Chapter 4). The proposed policy is practical in that it does not assume that (1) the system can continuously adjust speed, and (2) a specific set of speed levels is available. As a consequence, our policy can be easily deployed and is shown to improve performance by about 47.7% on average and up to about 68%.

- (4). We present both optimal and heuristic methods to minimize the peak temperature of a multicore system running hard real-time applications (Chapter 5). The optimal method reveals that an energy-minimal system is not necessarily a cool system. Specifically, minimizing energy can lead to a system that is about 9°C hotter on average and up to about 25°C when compared to

systems in which the maximum temperature is minimized. This is because energy minimization ignores both temporal and spatial thermal variations. To solve large problem instances, we propose an efficient heuristic framework that allows system designers to trade off accuracy against running time and insert idle times into a schedule to further cool the system down.

The dissertation concludes in Chapter 6 with some recommendations on future research directions.

## CHAPTER 2

## PERIOD AND DEADLINE SELECTION FOR SCHEDULABILITY IN REAL-TIME SYSTEMS

To alleviate occasional overload conditions in real-time control systems, some control tasks are executed less often to reduce computational demands on the processor. Since control tasks are usually activated periodically, their periods can be used as a tuning knob to determine how often these tasks should execute without compromising control system stability. Existing frameworks assume that only task periods are adjustable and that task deadlines remain unchanged at all times. This chapter formally introduces a more general real-time task model where task deadlines are functions of task periods. This tight coupling between task deadlines and task periods has been discussed in a recent work in control systems and presents a novel real-time scheduling challenge.

Because of the aforementioned task period and deadline relationship, an overload management mechanism must now not only determine suitable task periods, but also consider the impact of the newly changed task deadlines on system schedulability. To solve this problem, which we shall refer to as the period and deadline selection problem, this chapter identifies a feasible period-deadline combination and proposes a heuristic, which iteratively adjusts task periods and deadlines in such a way that the task set becomes schedulable. Experimental results show that the heuristic finds a solution to the period and deadline selection problem over 73% of the time, using less than three search iterations.

#### 2.1 Introduction

In this section, we provide an overview of the problem, review related work, state our contributions, and present the organization of this chapter.

#### 2.1.1 Problem Overview

Task scheduling has long been an important research topic in real-time systems. As stated in Chapter 1, missing a deadline in a hard real-time system may lead to catastrophic consequences, such as failure to stop an automatically controlled train on time [67].

Despite having been traditionally treated as hard real-time systems, many control systems are quite robust in the presence of certain timing perturbations. Generally speaking, depending on the system state, the sampling rate of a control system can vary within some interval without causing significant performance degradation. This observation is very useful when temporal overload situations occur. A real-time system is said to experience an overload when it cannot finish executing one or more tasks on time due to resource constraints. Although robust, if too many deadlines have been missed or if such misses occur in a highly unpredictable manner, a control system may no longer stabilize, even if all system resources are now dedicated to it.

In this chapter, we focus on alleviating temporal overload conditions in realtime control systems by increasing some (or all) task periods in such a way that all task deadlines can be met. As stated previously, we exploit the knowledge that control tasks are quite robust, which allows their periods to vary within some intervals. As an added challenge, whenever a task period changes, its deadline also varies according to some prespecified function. In other words, task deadlines, which are less than or equal to task periods, are also a function of the periods. This interdependency between task periods and task deadlines is not merely an academic exercise; the work in [108] shows that such a relationship is indeed real (we will explain this novel task model later on in this chapter). In summary, we are interested in solving the period and deadline selection problem for real-time systems under overload conditions.

#### 2.1.2 Related Work

There are two main approaches to dealing with overloads in real-time systems: (i) dropping some instances of tasks (i.e., jobs) in a controlled manner, and (ii) increasing task periods, equivalently decreasing the sampling rates, in such a way that no deadlines are missed and the performance of the system remains acceptable.

Many algorithms have been proposed to control job dropping patterns. Some examples are the (m, k) scheduling algorithms [44], the Dynamic Window-Constrained Scheduling (DWCS) algorithm [109], the skip-over algorithms [54], and the algorithms for weakly hard real-time systems [11]. In other work such as the imprecise computation model [29] and reward-based model [6], the aim is to maximize system workload, which is assumed to be proportional to the quality of service (QoS).

Since it is sometimes more suitable to execute jobs less often instead of dropping them or allocating fewer cycles [4], we focus on such an approach in this chapter. Many previous research papers can be found on the management of overloads in real-time systems based on task period adjustments (e.g., [58]). The works in [94], [93] and [12] solve the period selection problem for the earliest-deadline first (EDF), rate-monotone (RM), and fixed-priority scheduling algorithms, respectively. Cervin et al. propose an online period adjustment mechanism with varying task computation times [55]. In [23], Caccamo et al. consider scenarios where the worst-case task execution times can be large but the normal task execution times tend to be very small. To efficiently use system resources while avoiding overruns, the idea of task rate adaptations is combined with the use of a constant bandwidth server to guarantee hard real-time deadlines. Buttazzo et al. propose an optimal period selection algorithm in [20] based on the elastic task model. Many extensions to the elastic task model can be found in [17, 18, 21, 22].

In terms of schedulability tests for task sets with deadlines less than periods, Baruah et al. proposed an exact test with pseudo-polynomial running time [10]. For efficiency, we will use the sufficient test provided in [24, 25]. However, there exist other sufficient conditions for schedulability when task deadlines are less than task periods. For instance, Devi proposed a set of sufficient schedulability tests in [34]. The main difference between this set of tests and the one in [24] is that the former requires N checks while the latter requires only one check. Some extensions to Devi's work include, but are not limited to, an approximate schedulability test [1], an adaptation to fixed-priority systems [38], and novel feasibility tests that are shown to outperform Devi's schedulability conditions [71].

Most previous works on overload management assume that only task periods can change. In [95], task deadlines vary with time, but the tasks do not have periods (i.e., tasks are non-periodic). There has also been work on determining the lower bound on task deadlines using sensitivity analysis in a periodic task model [7]. However, to the best of our knowledge, there has been no work that allows task periods and deadlines to change simultaneously.

### 2.1.3 Contributions

Our first main contribution is the introduction of a more general and realistic task model where both task deadlines and task periods can vary within some intervals. The deadline of a task in a real-time system really denotes the maximum allowable delay that task can tolerate. As shown by the authors in [108], different sampling rates for a control system lead to different acceptable maximum delays (deadlines). Specifically, a higher sampling rate means that the corresponding control task executes more often, which, in turns, allows the system to be more tolerant to a relatively larger delay. Conversely, a larger sampling period could make the system more susceptible to delays and thus a relatively smaller deadline may be required. In other words, the deadline of a task is a function of its period.

The relationship between task periods and task deadlines poses an interesting scheduling problem, as one can no longer assume that increasing task periods will always improve schedulability. Although it is possible to set task deadlines to be the smallest deadlines (specified by the applications) and only vary task periods, doing so may significantly worsen schedulability. As our second main contribution, we study some interesting relationships between task periods and task deadlines that will help to solve the period and deadline selection problem. We then propose an efficient heuristic that can be used to find a set of feasible task periods and deadlines and alleviate an overload situation in a timely manner. Our heuristic can be applied to any real-time task set where task deadlines are less than or equal to task periods and where task deadlines are piecewise first-order differentiable functions of their respective periods. Experimental results indicate that our heuristic finds a solution to the period and deadline selection problem over 73% of the time.

#### 2.1.4 Organization

We introduce the system model and formally define the problem in Section 2.2. Section 2.3 provides a motivating example to highlight the importance and usefulness of our work. We present our formal analysis and heuristic in Sections 2.4. Section 2.5 summarizes some experimental results and the chapter concludes with Section 2.6.

#### 2.2 System Model and Problem Definition

In this section, we describe the system model and review some relevant schedulability tests. We also give a formal definition of the period and deadline selection problem.

#### 2.2.1 Task Model

Our system consists of a set of N periodic, synchronous tasks specified by the following 5-tuple:  $(C_i, T_i, T_{i_{min}}, T_{i_{max}}, D_i)$ ,  $i = 1, \ldots, N$ , where  $C_i$  is the worstcase execution time of task  $\tau_i$ , and  $T_i$  is  $\tau_i$ 's period (to be decided), which must lie somewhere between  $T_{i_{min}}$  and  $T_{i_{max}}$ . The parameter  $T_{i_{min}}$  denotes the most desirable period of  $\tau_i$ , as specified by the application, whereas  $T_{i_{max}}$  represents the maximum period beyond which the system performance is no longer acceptable. The parameter  $D_i$  is the deadline of  $\tau_i$ , and is dependent on the actual task period  $T_i$ . That is, the deadline of a task is a function of its period. Specifically,  $D_i \leq T_i, T_i \in [T_{i_{min}}, T_{i_{max}}]$  and  $D_i$  is some function that is piecewise first-order differentiable.

The utilization of each task  $\tau_i$  is defined as  $U_i = C_i/T_i$  and denotes system resources dedicated to  $\tau_i$ . Since the period of  $\tau_i$ , i = 1, ..., N, can vary between  $T_{i_{min}}$  and  $T_{i_{max}}$ , the minimum utilization of  $\tau_i$ ,  $U_{i_{min}} = C_i/T_{i_{max}}$ , and its maximum (desired) utilization,  $U_{i_{max}} = C_i/T_{i_{min}}$ , are also defined, for i = 1, ..., N.

#### 2.2.2 Schedulability Tests

Throughout this chapter, we will assume that the Earliest Deadline First (EDF) scheduling algorithm [66] is used. When one or more tasks need to decrease their period and/or deadline in response to either internal (e.g., change in sampling rate of one or more tasks in the system) or external (e.g., network traffic) factors, a schedulability test must be performed to assess whether the task set is still schedulable. A schedulability test may also provide some guidance on how to adjust task parameters in such a way that a feasible task set can be obtained. Based on the assumption that the EDF scheduling algorithm is used, there exist some useful schedulability conditions that are briefly reviewed here.

A necessary condition for schedulability of any given task set is stated in the following lemma.

**Lemma 2.1** [24] Consider a task set  $\Gamma$ , let  $C_i$  and  $D_i$  be the execution time and the deadline of task  $\tau_i$ , i = 1, ..., N, respectively. In addition, let all tasks start at time 0 and let the tasks in  $\Gamma$  be ordered in a non-decreasing order of deadlines. Regardless of the choices of periods, any task set that is schedulable must satisfy the following property

$$\sum_{i=1}^{j} C_i \le D_j, j = 1, \dots, N.$$

(2.1)

Since task deadlines can be less than or equal to periods, there exist an exact, albeit complex, schedulability test for EDF as specified by Baruah et al [10]. Said test is restated in the following theorem.

**Theorem 2.1** [10] Consider a periodic task set with  $C_i$ ,  $D_i$ , and  $T_i$  as the execution time, deadline, and period of task  $\tau_i$ , i = 1, ..., N, respectively. Let  $D_i \leq T_i$ , i = 1, ..., N, the task set is schedulable if and only if the following constraint is satisfied  $\forall L \in \{kT_i + D_i \leq \min(B_p, H)\}$  and  $k \in \mathcal{N}$  (the set of natural numbers including 0), where  $B_p$  and H denote the busy period and hyperperiod as defined in [16], respectively,

$$L \ge \sum_{i=1}^{N} \left( \left\lfloor \frac{L - D_i}{T_i} \right\rfloor + 1 \right) C_i.$$

(2.2)

Verifying that (2.2) is satisfied for all L is the main source of complexity in the above schedulability test. To reduce the complexity of the test in Theorem 2.1, the authors in [24] proposed the following sufficient condition for schedulability.

**Theorem 2.2** [24] Given a set  $\Gamma$  of N tasks that satisfy Lemma 2.1. Let  $C_i$ ,  $D_i$ , and  $T_i$  be the execution time, deadline, and period of task  $\tau_i$ , i = 1, ..., N, respectively. In addition, let the tasks in  $\Gamma$  be sorted in a non-decreasing order of deadlines. The task set  $\Gamma$  is schedulable if

$$L^* \ge \sum_{i=1}^{N} \left( \frac{L^* - D_i}{T_i} + 1 \right) C_i$$

(2.3)

where

$$L^* = \begin{cases} D_2 & : \quad D_1 + T_1 \le D_2 \\ \min_{i=1}^N (T_i + D_i) & : \quad \text{otherwise.} \end{cases}$$

For completeness, we include another existing sufficient condition for EDF schedulability.

**Theorem 2.3** [67] Consider a set  $\Gamma$  of N tasks where  $C_i$  and  $D_i$  are the execution time and deadline of task  $\tau_i$ ,  $i = 1, \ldots, N$ , respectively. The task set  $\Gamma$  is schedulable by the EDF policy if

$$\sum_{i=1}^{N} \frac{C_i}{D_i} \le 1. \tag{2.4}$$

We will use some of these schedulability conditions in Section 2.4.

#### 2.2.3 Problem Definition

Given an initially infeasible set  $\Gamma$  of N real-time tasks where the period  $T_i$ of task  $\tau_i$  must lie somewhere between  $[T_{i_{min}}, T_{i_{max}}]$ , and the deadline  $D_i$  of  $\tau_i$  is some piecewise first-order differentiable function of its period, determine a perioddeadline combination  $(T_i, D_i)$ ,  $i = 1, \ldots, N$ , such that the task set  $\Gamma$  becomes schedulable. In other words, we wish to find  $(T_i, D_i)$ ,  $i = 1, \ldots, N$ , such that

$$\sum_{i=1}^{N} \left( \left\lfloor \frac{L - D_i}{T_i} \right\rfloor + 1 \right) C_i \le L$$

(2.5)

$$T_i \ge T_{i_{min}} \quad \text{for } i = 1, 2, \cdots, N \tag{2.6}$$

$$T_i \le T_{i_{max}} \quad \text{for } i = 1, 2, \cdots, N, \tag{2.7}$$

where L is defined as in Theorem 2.1,  $C_i$  is the worst-case execution time of  $\tau_i$ , and both  $T_{i_{min}}$  and  $T_{i_{max}}$  are specified by the applications under consideration.

The constraint in (2.5) ensures the schedulability of the task set. The constraints in (2.6) and (2.7) bound the period of  $\tau_i$ , i = 1, ..., N, to ensure performance.

#### 2.3 Motivations

In control systems, an advantage in using the traditional periodic task model where task deadlines are fixed is that these systems can be treated as discrete-time systems for which there exists a variety of mature controller synthesis methods. However, when the periodic task model is used, task periods and deadlines are often chosen conservatively to guarantee stability. This leads to wasted resources and system over-provisioning. For these reasons, there has been a recent movement in the control system community to investigate alternative approaches to the periodic task model.

The work in [108] is such an example. Each task determines its next release time based on the current system state as sampled by the current job. This type of control systems is known as state-based self-triggering systems. Self-triggering can be viewed as a closed-loop form of releasing tasks for execution, whereas the traditional periodic task model is considered open-loop. Since each control task is aware of its system state, it can adjust its period and deadline in such a way that only the required system resource is requested. More precisely, with a small period, a task is executed relatively often and the system is thus more tolerant to delays, permitting the task deadline to be relatively larger (e.g., perhaps almost as large as the task period itself). On the other hand, when the task period is large, the system is more susceptible to disturbances, requiring that the task deadline be relatively smaller (compared to the task period) to reduce jitters.

To understand how the deadline as a function of the period affects schedulability, let us consider a simple task set, which consists of two identical tasks whose attributes are shown in Table 2.1. The deadline of each task can be computed as shown in the last column of Table 2.1 (all units are in milliseconds). Figure 2.1 plots the task deadlines as a function of task periods where the vertical dotted lines limit the acceptable period range for the example tasks. Initially, the task set is not schedulable with  $T_1 = T_2 = 0.5$  ms, since the initial deadlines  $D_1 = D_2 =$ 0.303 ms and the aggregate execution time required is 0.36 ms. If we simply set  $T_1 = T_2 = 3.5$  ms, which is the maximum allowable periods, then the corresponding deadlines will be  $D_1 = D_2 = 0.106$  ms. The task set is, again, not schedulable and one may wrongly conclude that the task set cannot be made feasible. However, there exists many feasible period-deadline combinations. For example, when  $T_1 = T_2 = 1$  ms and  $D_1 = D_2 = 0.368$  ms, the task set is schedulable.

### TABLE 2.1

# TASK SET FOR MOTIVATING EXAMPLE ILLUSTRATING THE IMPORTANCE OF THE PERIOD AND DEADLINE SELECTION PROBLEM

| Task    | $C_i$ | $T_{i_{min}}$ | $T_{i_{max}}$ | $D_i$                              |

|---------|-------|---------------|---------------|------------------------------------|

| $	au_1$ | 0.18  | 0.5           | 3.5           | $T_1 e^{-T_1}, T_1 \in [0.5, 3.5]$ |

| $	au_2$ | 0.18  | 0.5           | 3.5           | $T_2 e^{-T_2}, T_2 \in [0.5, 3.5]$ |

In the traditional periodic task model, since task deadlines are considered fixed, system designers must use the smallest possible deadlines to ensure that, given a specific range of task periods, the system will always meet the minimum

Figure 2.1. Task deadlines in milliseconds as a function of task periods, also in milliseconds. The area inside the vertical dotted lines denotes the acceptable period ranges for the task set in Table 2.1.

performance requirements. For the above example, the smallest deadline for both tasks is 0.106 ms, which means that the task set can never be made schedulable using existing techniques. It is not difficult to see in this example that the task deadlines can be set to 0.36 ms for the task set to be feasible, regardless of the resultant periods. In general, however, both task periods and task deadlines must be considered simultaneously, since different tasks may have different timing requirements.

#### 2.4 Period and Deadline Selection Heuristic

As shown in the previous section, since a task deadline is a function of its period, adjusting the period affects both the corresponding deadline and the schedulability of the entire task set. Due to the condition in (2.5), the problem defined in Section 2.2.3 is nonlinear, non-convex, and non-continuous because of the variable L. Solving the above problem directly using a nonlinear solver is inefficient and the solver cannot guarantee that a solution will be found, even if one exists. (Non-linear solvers usually employ interior-point methods [39] or branch-and-bound techniques [13, 30] to solve the problem.) For these reasons, we propose using an efficient heuristic to find a solution. In a nutshell, the heuristic starts by performing some simple schedulability tests to determine a feasible period-deadline combination. Such tests also serve to eliminate some infeasible period and deadline values should they fail to identify a feasible task set. The heuristic then uses this knowledge to conduct an efficient search process.

### 2.4.1 Identifying Infeasible Regions Using Simple Tests

We now describe our idea of using the simple tests in more detail. We first determine the minimum and maximum deadlines,  $D_{i_{min}}$  and  $D_{i_{max}}$ , respectively, for each task  $\tau_i$ , i = 1, ..., N. The maximum deadline of  $\tau_i$ ,  $D_{i_{max}}$  can directly be solved by finding the maximum of  $D_i$ . (Recall that the maximum of a function can be obtained by taking its derivative and subsequently finding the root(s) of said derivative.) The corresponding period value is denoted  $T_i^{Dmax}$ , i = 1, ..., N.

To determine the lower bound on the deadline of a task  $\tau_i$ , i = 1, ..., N, we would ideally use Lemma 2.1. However, Lemma 2.1 requires that tasks be sorted in a non-decreasing order of deadlines. Since a task deadline is a variable

to be determined, we cannot directly use Lemma 2.1 to compute the minimum deadline. Instead, let  $\widetilde{D}_i$  be the smallest deadline of task  $\tau_i$ , i.e.,  $\widetilde{D}_i \leq D(T_i)$ ,  $T_i \in [T_{i_{min}}, T_{i_{max}}], i = 1, \ldots, N$ . We say that task  $\tau_i$  dominates task  $\tau_j$  (denoted by  $\tau_i \succeq \tau_j$ ) if  $\widetilde{D}_i > D_{j_{max}}$ . Otherwise, we say that  $\tau_i$  and  $\tau_j$  are non-comparable. Using the above dominance definition, a partial order can be built for a given set of tasks. It is easy to see that Lemma 2.1 holds true for tasks with deadlines as variables if we sort the tasks using the partial order established above. For example, consider a simple task set consisting of task  $\tau_j$  and  $\tau_k$ . If  $\tau_j \succeq \tau_k$  then  $D_{k_{min}} = C_k$  and  $D_{j_{min}} = C_k + C_j$ . In general, for a task  $\tau_i$ ,  $D_{i_{min}} = \max{\{\mathbf{DS}\}} + C_i$ , where **DS** is the set of deadlines of tasks that are dominated by  $\tau_i$ . Since  $D_{i_{min}}$  set in this way is a lower bound on the minimum task deadline for task  $\tau_i$ ,  $i = 1, \ldots, N$ , we can eliminate some infeasible period-deadline combinations (shown by the rightslanted pattern in Figure 2.2). The task period that corresponds to when the task deadline is  $D_{i_{min}}$  is referred to as  $T_i^{Dmin}$ ,  $i = 1, \ldots, N$ . Clearly, if  $D_{i_{min}}$ ,  $i = 1, \ldots, N$ , satisfy the condition in Lemma 2.1, but if  $D_{i_{max}} < D_{i_{min}}$  for some  $i = 1, \ldots, N$ , then the task set cannot be made schedulable.

Once we have found the minimum and maximum deadlines for each task in the task set, we can apply a series of efficient schedulability tests to avoid searching for a solution, if possible. We start with the sufficient condition from Theorem 2.3 using  $D_{i_{max}}$ , i = 1, ..., N, as the task deadlines. The following lemma helps to explain why only  $D_{i_{max}}$ , i = 1, ..., N, need to be considered when applying Theorem 2.3 on the current task set.

**Lemma 2.2** Consider a set  $\Gamma$  of N tasks. Let  $C_i$  and  $D_i$  be the execution time and deadline of task  $\tau_i$ , i = 1, ..., N, respectively. If the schedulability condition from Theorem 2.3 is not satisfied for  $D_{i_{max}}$ , i = 1, ..., N, then it is not satisfied

Figure 2.2. Task deadline in milliseconds as a function of task periods, also in milliseconds. The left-slanted and right-slanted areas denote infeasible period and deadline combinations. The unpatterned region represents possibly feasible period and deadline combinations and is where the search process is conducted.

for any  $D_i < D_{i_{max}}, i = 1, ..., N$ .

**Proof:** If the task set  $\Gamma$  fails the schedulability test in Theorem 2.3, then