# Digital Integrated Circuits – EECS 312

http://robertdick.org/eecs312/

Robert Dick 2417-E EECS dickrp@umich.edu 734–763–3329 847–530–1824

| GSI:    | Shengshou Lu   |

|---------|----------------|

| Office: | 2725 BBB       |

| Email:  | luss@umich.edu |

# Writing, drop box

### Writing

- 1 Organization.

- 2 Get to the point.

- Show, don't tell.

- 4 Keep it relatively formal.

This is awesome: William Strunk Jr. and E. B. White. The Elements of Style.

Macmillan Publishing Co., Inc., 2000.

In–out box EECS 2417, in the jungle to the back-right of the room.

# Homework 1 tips

- Problem 1: Use equations in textbook or lecture notes packet 4.

- Problem 2: See lecture notes packet 2 and use reasoning. Can explain/justify assumptions you make, e.g., frequency is closely related to number of operations per second. Can also use other sources, but cite them.

- Problem 4: Use cited equation in lecture notes packet 2.

- Problems 5 and 6: Learned these in lecture and lab assignment 1.

- Problems 7 and 8: Learned these in lecture.

- Problem 10: This is an extension from lab assignment 1 and what we learned about PMOSFETs in lectures 2 and 3.

- Problems 11 and 12: We learned these in lecture 4.

### Midterm exam time

- Our original midterm exam time conflicted with many classes.

- Now shifted to 7:00-8:30 on 8 October in 1670 BBB.

# Special topics talks

- I read all of your areas of interest and boiled this down to general topics you might give special topics talks on.

- Shengshuo posted a Google document, which you used to select topics.

- I added dates to all topics.

- Talks will be given in the middle of lecture: 5-7 minutes.

- First one is 24 Sep on fabrication. It might be good to talk with or exchange email with me about the details on this.

- If your talk topic looks similar to something in the course overview document, it is best to send me an outline of your talk a week or two ahead of time so I can warn you if we might be covering the same material.

- If you will use slides, send me a PDF by midnight of the previous day at the latest. I will project using my laptop, and will post the slides to the website.

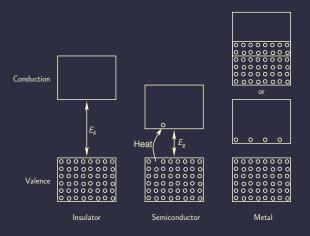

# Review of semiconductor basics and diodes

- Electrons and holes.

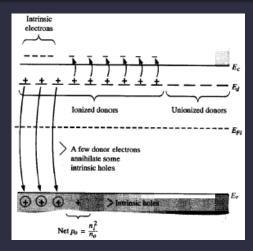

- Intrinsic charge carriers and doping.

- Diffusion and drift.

- Built-in potential.

- I–V curve for diodes.

- Avalanche breakdown.

### Material properties

### Dopant influence on energy band diagram

### From Sameh Rehan.

Robert Dick Digital Integrated Circuits

# Lecture plan

- 1. MOSFET threshold voltage

- 2. MOSFET operating regions

- 3. MOSFET short channel effects

- 4. Homework

#### MOSFET threshold voltage

MOSFET operating regions MOSFET short channel effects Homework

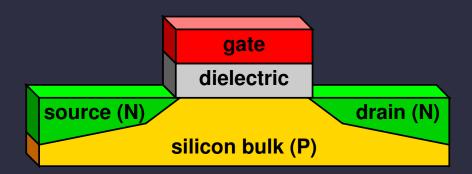

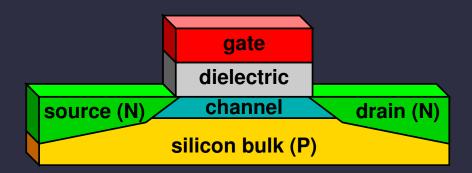

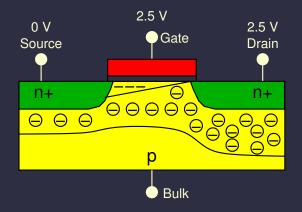

# NMOSFET

#### MOSFET threshold voltage

MOSFET operating regions MOSFET short channel effects Homework

# NMOSFET

# **MOSFET** properties

- 1 Voltage-controlled current.

- <sup>2</sup> Very little steady-state  $I_{GS}$  and  $I_{GD}$ .

- When on, channel sandwiched between insulator and depletion region.

- 4 Bulk bias can be changed.

- Generally made minimal-length: Why?

MOSFET threshold voltage

MOSFET operating regions MOSFET short channel effects Homework

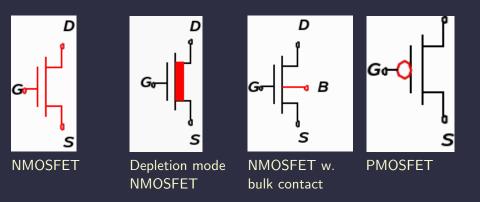

# MOSFET symbols

Physics-based threshold voltage expression

$$V_{T} = \Phi_{ms} - 2\Phi_{F} - \left(\frac{Q_{B}}{C_{ox}} + \frac{Q_{SS}}{C_{ox}} + \frac{Q_{I}}{C_{ox}}\right)$$

•  $\Phi_{ms} = \Phi_m - \overline{\Phi_s}$ : Gate work function, point at which charge transfer due to differing work functions stops.

•  $\Phi_F = \Phi_T \ln \left( \frac{N_A}{n_i} \right)$ : Fermi potential.

•

$$\Phi_T = \frac{kT}{q}$$

- $\frac{Q_B}{C_{\alpha \gamma}}$ : Voltage due to depletion layer charge.

- $\frac{Q_{SS}}{C_{cv}}$ : Voltage due to surface charge.

- $\frac{Q_l}{C_{\text{ex}}}$ : Voltage due to implants.

$$Q_B = \sqrt{2qN_A\epsilon_{Si}\left(\left|-2\Phi_F+V_{SB}

ight|

ight)}$$

Precisely determining these parameters is challenging.

### Empirical threshold voltage expression

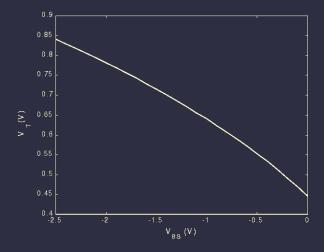

$$V_{T} = V_{T0} + \gamma \left( \sqrt{|-2\Phi_{F} + V_{SB}|} - \sqrt{|2\Phi_{F}|} \right)$$

$$V_{T0} = \Phi_{ms} - 2\Phi_{F} - \left( \frac{Q_{B0}}{C_{ox}} + \frac{Q_{SS}}{C_{ox}} + \frac{Q_{I}}{C_{ox}} \right)$$

$$\gamma = \frac{\sqrt{2q\epsilon_{SI}N_{A}}}{C_{ox}}$$

•  $V_{T0}$ :  $V_T$  at  $V_{SB} = 0$ . Usually measured directly.

•  $Q_{B0}$ : Depletion layer charge when  $V_{SB} = 0$ .

•  $\gamma$ : Body-effect coefficient expressing impact of  $\Delta V_{SB}$ .

# Lecture plan

- 1. MOSFET threshold voltage

- 2. MOSFET operating regions

- 3. MOSFET short channel effects

- 4. Homework

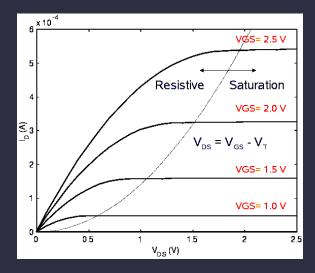

# I–V relationship

Robert Dick Digital Integrated Circuits

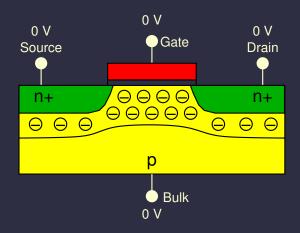

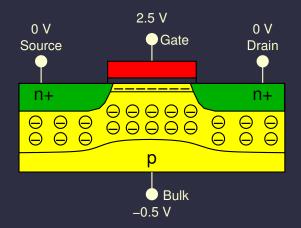

# Unbiased

Depletion regions at P–N junctions.

# $V_{GS}$ high

Inversion in thin channel under gate.

# Body bias: $V_{BS}$ low

- Depletion region widens.

- Carriers in channel repelled to source.

# Body effect as a function of $V_{BS}$

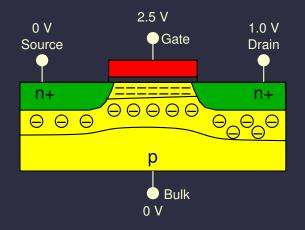

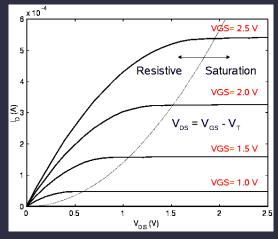

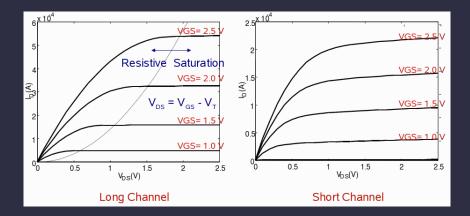

# Linear region: $V_{GS}$ high and $V_{DS}$ moderately high

Slight deformation of channel due to widening depletion region around reverse-biased P–N junction.

# Linear mode current-voltage relationship for long-channel device

Given:

$$V_{DS} \leq V_{GS} - V_T$$

$I_D = k'_n \frac{W}{L} \left( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right)$

$k'_n = \mu_n C_{ox} = \frac{\mu_n \epsilon_{ox}}{t_{ox}}$

- $k'_n$ : Process transconductance.

- C<sub>ox</sub>: Oxide capacitance.

- $\mu$ : Carrier mobility.

- W: Transistor width.

- L: Transistor length.

- $\epsilon_{Si}$ : Permittivity.

- *t<sub>ox</sub>*: Oxide thickness.

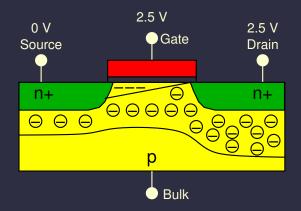

# Saturation: $V_{GS}$ high and $V_{DS}$ very high

Pinch-off due to widening depletion region around reverse-biased P–N junction.

# Saturation mode current-voltage relationship for long-channel device

$$egin{array}{lll} {

m Given:} & V_{DS} \geq V_{GS} - V_{\mathcal{T}} \ & I_D = rac{k_n'}{2} rac{W}{L} \left(V_{GS} - V_{\mathcal{T}}

ight)^2 \end{array}$$

# Saturation: $V_{GS}$ high and $V_{DS}$ very high

- Pinch-off due to widening depletion region around reverse-biased P–N junction.

- Decreased channel length → some increase in current.

Saturation mode current-voltage relationship for long-channel device considering channel length modulation

> Given:  $V_{DS} \ge V_{GS} - V_T$   $I_D = \frac{k'_n}{2} \frac{W}{L} (V_{GS} - V_T)^2$  $I_D = \frac{k'_n}{2} \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$

- Channel length decreases with high  $V_{DS}$  due to expanding depletion region.

- $\lambda$ : Empirical constant inversely related to channel length.

# Lecture plan

- 1. MOSFET threshold voltage

- 2. MOSFET operating regions

- 3. MOSFET short channel effects

- 4. Homework

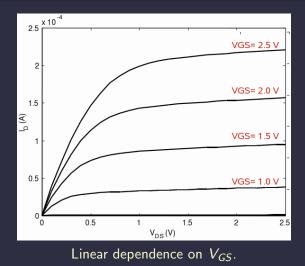

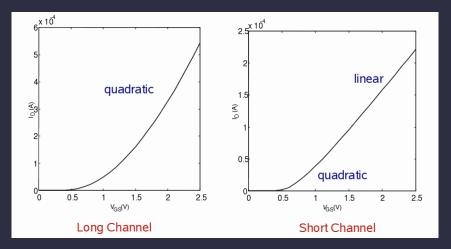

# Current-voltage relationship for long-channel devices

Quadratic dependence on  $V_{GS}$ .

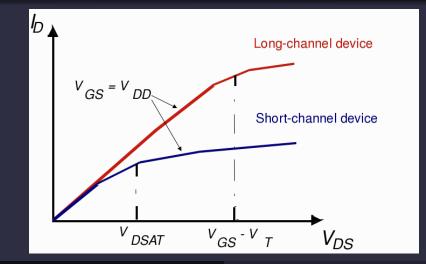

### Current-voltage relationship for short-channel devices

Robert Dick Digital Integrated Circuits

# Current-voltage relationship for long- and short-channel devices

Robert Dick Di

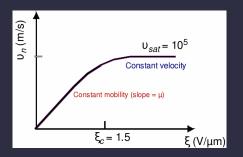

### Velocity saturation

- Charge carriers move randomly, with a net drift velocity.

- What happens when drift velocity approaches particle velocity?

### $V_{GS}$ dependence for long- and short-channel devices

## $V_{DS}$ dependence for long- and short-channel devices

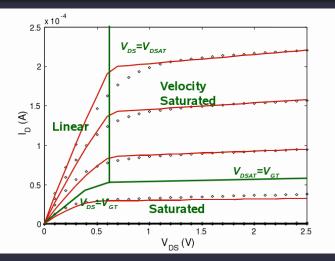

# Unified model

$$\begin{split} I_D &= \begin{cases} 0 & \text{if } V_{GT} \leq 0 \text{ and} \\ k' \frac{W}{L} \left( V_{GT} V_{min} - \frac{V_{min}^2}{2} \right) (1 + \lambda V_{DS}) & \text{if } V_{GT} \geq 0. \end{cases} \\ V_{min} &= \min \left( V_{GT}, V_{DS}, V_{DSAT} \right) \\ V_{GT} &= V_{GS} - V_T \\ V_T &= V_{T0} + \gamma \left( \sqrt{|-2\Phi_F + V_{SB}|} - \sqrt{|2\Phi_F|} \right) \end{split}$$

# Quality of unified model

Dots are from detailed simulation, line is for unified model.

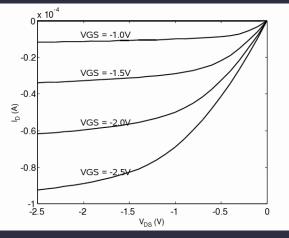

# Generalization for PMOSFETs

Negate all variables.

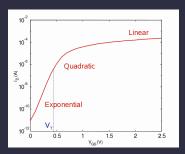

### Near-threshold and subthreshold operation

$$I_D = I_S e^{rac{V_{GS}}{nkT/q}} \left(1-e^{-rac{V_{DS}}{kT/q}}

ight) \left(1+\lambda V_{DS}

ight)$$

- *I<sub>S</sub>*: Empirical current normalization parameter.

- $n \ (\approx 1.5)$ : Empirical temperature dependence parameter.

# Subthreshold slope

- $I_D$  clearly depends exponentially on  $V_{GS}$ .

- Define the slope factor, S, as the change in  $V_{GS}$  for  $I_D$  to change by  $10 \times .$

- From the subthreshold current expression, can solve for S.

$$S = n\left(\frac{kT}{q}\right)\ln\left(10\right)$$

# Simplified resistance-based model

- Sometimes, static behavior is sufficient.

- Can model on device as resistor.

- Off devices with  $\infty$  resistance.

# MOSFET operating regions summary

- Sub-threshold

- Weak inversion.

- $V_{GS} \leq V_T$ .

- $I_D$  exponential in  $V_{GS}$ .

- $I_D$  linear in  $V_{DS}$ .

- Linear or resistive: Strong inversion.

- $V_{GS} \geq V_T$ .

- $V_{DS} \leq V_{DSAT}$ .

- Saturated: Strong inversion but pinch-off or velocity saturation.

- $V_{GS} \geq V_T$ .

- $V_{DS} \ge V_{DSAT}$ .

- Approximately constant current.

# Summary

- Physics allows understanding of MOSFET channel inversion and other behaviors.

- 2 Some physical parameters can be difficult to directly measure, so empirical model often used.

- Threshold voltage is important, and can be statically and dynamically varied.

- 4 MOSFETs have regions of operation decided by  $V_{DS}$ .

- <sup>5</sup> Behaviors vary from long-channel to short-channel devices.

- 6 For manual analysis, a region-based model can be used.

- Subthreshold operation can enable very low power consumption, at cost of low performance.

# Upcoming topics

- Fabrication.

- Transistor dynamic behavior.

- Interconnect.

# Announcement: ECE Faculty Candidate Seminar

- Professor Leung Tsang, Department of Electrical Engineering, University of Washington

- Electromagnetic Simulations of Signal Integrity in Interconnects: Effects of Multiple Vias and Surface Roughness

- Wednesday, September 18, 2013

- 9:30–10:30

- Johnson Rooms 3rd floor Lurie

# Lecture plan

- 1. MOSFET threshold voltage

- 2. MOSFET operating regions

- 3. MOSFET short channel effects

- 4. Homework

# Homework assignment

• 24 September: Read Section 2.1, 2.2, and 1.3.1 in J. Rabaey,

A. Chandrakasan, and B. Nikolic. *Digital Integrated Circuits: A Design Perspective*.

Prentice-Hall, second edition, 2003. Really! You will be confused

- on Tuesday, otherwise.

- 24 September: Homework 1.