# Pass-Transistor Logic and Dynamic Logic

1

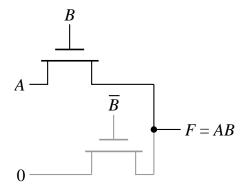

## PTL AND Gate

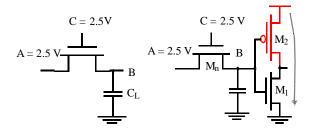

## **NMOS-only Switch**

V<sub>B</sub> does not pull up to 2.5V, but 2.5V - V<sub>T</sub>

Threshold voltage loss causes static power consumption

NMOS has higher threshold than PMOS (body effect)

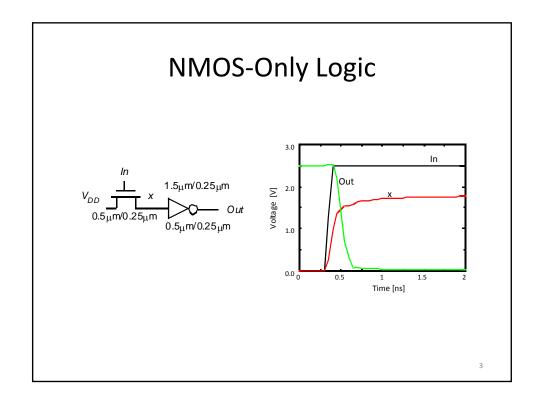

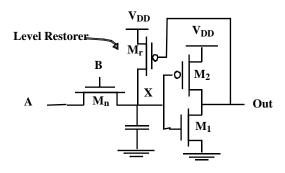

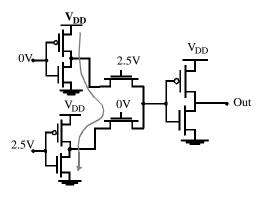

#### NMOS Only Logic: Level Restoring Transistor

- Advantage: Full Swing

- Restorer adds capacitance, takes away pull down current at X

- Ratio problem

5

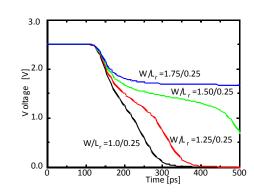

## **Restorer Sizing**

- Upper limit on restorer size

- Pass-transistor pull-down can have several transistors in stack

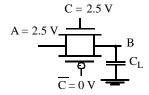

### Solution 2: Single Transistor Pass Gate with $V_T=0$

WATCH OUT FOR LEAKAGE CURRENTS

-

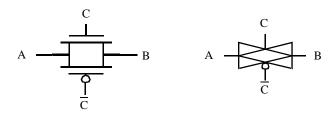

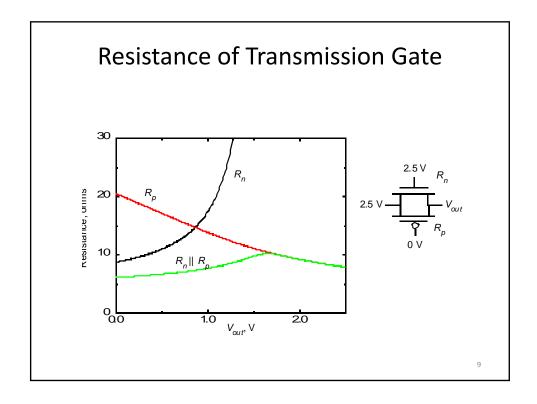

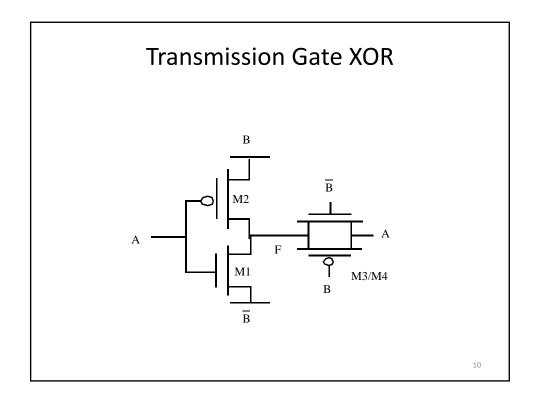

#### Solution 3: Transmission Gate

#### **Dynamic CMOS**

- In static circuits at every point in time (except when switching) the output is connected to either GND or V<sub>DD</sub> via a low resistance path.

- fan-in of n requires 2n (n N-type + n P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires on n + 2 (n+1 N-type + 1 P-type) transistors

11

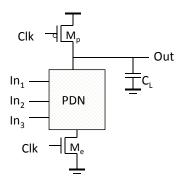

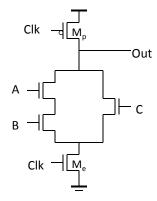

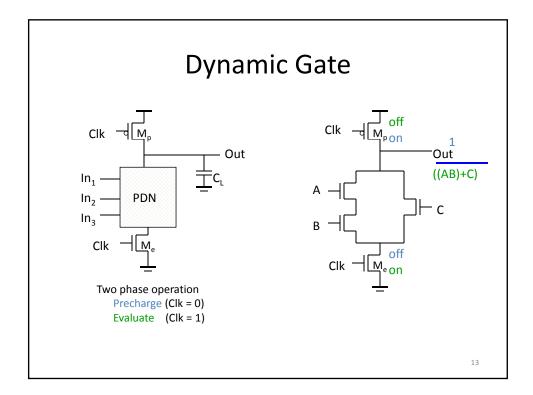

#### **Dynamic Gate**

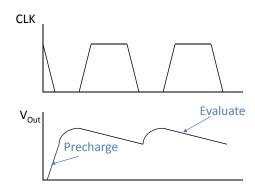

Two phase operation

Precharge (CLK = 0)

Evaluate (CLK = 1)

### **Conditions on Output**

- Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation.

- Inputs to the gate can make at most one transition during evaluation.

- Output can be in the high impedance state during and after evaluation (PDN off), state is stored on C<sub>1</sub>

#### **Properties of Dynamic Gates**

- Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- Full swing outputs (V<sub>OL</sub> = GND and V<sub>OH</sub> = V<sub>DD</sub>)

- Non-ratioed sizing of the devices does not affect the logic levels

- Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no  $I_{\text{sc}\prime}$  so all the current provided by PDN goes into discharging  $C_L$

15

#### **Properties of Dynamic Gates**

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between  $\rm V_{DD}$  and GND (including  $\rm P_{sc})$

- no glitching

- higher transition probabilities

- extra load on Clk

- PDN starts to work as soon as the input signals exceed

V<sub>Tn</sub>, so V<sub>M</sub>, V<sub>IH</sub> and V<sub>II</sub> equal to V<sub>Tn</sub>

- low noise margin (NM<sub>1</sub>)

- Needs a precharge/evaluate clock

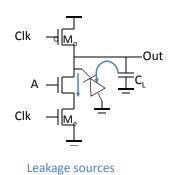

# Issues in Dynamic Design 1: Charge Leakage

Dominant component is subthreshold current

17

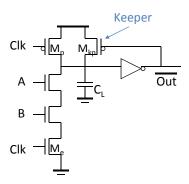

## Solution to Charge Leakage

Same approach as level restorer for pass-transistor logic