#### Advanced Digital Logic Design - EECS 303

Robert Dick Teacher: Office: L477 Tech

Email: dickrp@northwestern.edu

Phone 847-467-2298

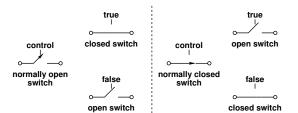

Switch-based definitions

### Constraints on network output

Under all possible combinations of input values

- Each output must be connected to an input value

- No output may be connected to conflicting input values

Relationship with CMOS

- Metal Oxide Semiconductor

- Positive and negative carriers

- Complimentary MOS

- PMOS gates are like normally closed switches that are good at transmitting only true (high) signals

- NMOS gates are like normally open switches that are good at transmitting only false (low) signals

Switch-based design representation

- A switch shorts or opens two points dependant on a control signal

- Used as models for digital transistors

- Why is using normally open and normally closed particularly useful for CMOS?

- NMOS and PMOS transistors easy to model

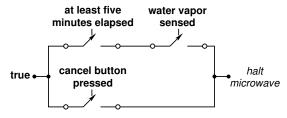

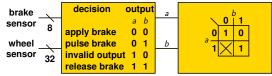

Microwave control example

- What happens if the cancel button is not pressed and five minutes haven't yet passed?

- The output value is undefined.

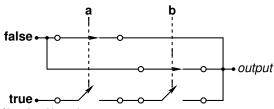

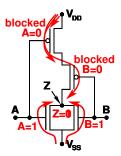

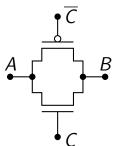

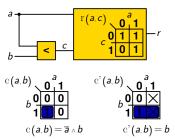

Switch-based AND

Note that this requires

- Normally closed switches that transmit false signals well

- Normally open switches that transmit true signals well

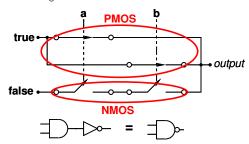

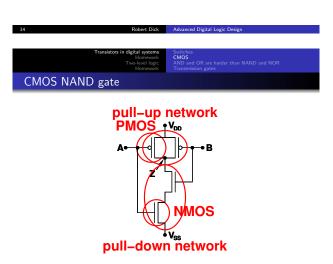

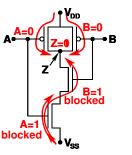

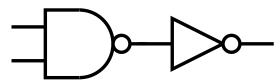

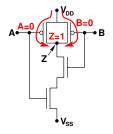

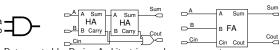

NAND gate

Therefore,  $\it NAND$  and  $\it NOR$  gates are used in CMOS design instead of AND and OR gates

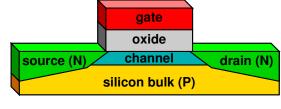

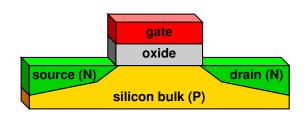

• Basic device in NMOS and PMOS (CMOS) technologies

• Can be used to construct any logic gate

gate oxide channe source (N) drain (N)

- Metal, oxide, semiconductor (MOS)

- Then it was polysilicon, oxide, semiconductor

- Now it is metal, hafnium-based low-k dielectric, semiconductor

- P-type bulk silicon doped with positively charged ions

- N-type diffusion regions doped with negatively charged ions

- Gate can be used to pull a few electrons near the oxide

- Forms channel region, conduction from source to drain starts

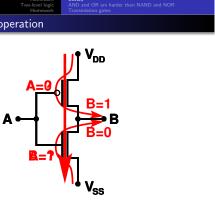

- **CMOS**

- NMOS turns on when the gate is high

- PMOS just like NMOS, with N and P regions swapped

- PMOS turns on when the gate is low

- NMOS good at conducting low (0s)

- PMOS good at conducting high (1s)

- Use NMOS and PMOS transistors together to build circuits

- Complementary metal oxide silicon (CMOS)

20 Robert Dick Advanced Digital Logic Design

Transistors in digital systems

Homerock

Two level logic

Logic Design

Switches

CMOS

AND and OR are harder than NAND and NOR

Transistors nations actions and the second of the second

ullet  $V_T$ , or threshold voltage, is commonly 0.7 V

Non-ideality of NMOS/PMOS transistors

- $\bullet$  NMOS conducts when  $\textit{V}_\textit{GS} > \textit{V}_\textit{T}$

- $\bullet$  PMOS conducts when  $\textit{V}_\textit{GS} < -\textit{V}_\textit{T}$

- What happens if an NMOS transistor's source is high?

- Or a PMOS transistor's source is low?

- Alternatively, if one states that  $V_{TN}=0.7~{

m V}$  and  $V_{TP}=-0.7~{

m V}$  then NMOS conducts when  $V_{GS}>V_{TN}$  and PMOS conducts when  $V_{GS}< V_{TP}$

Transistors in digital systems

Homework

Two-level logic

Homework

Two-level logic

Homework

Two-level logic

Transistors

Non-ideality of NMOS/PMOS transistors

- If an NMOS transistor's input were  $V_{DD}$  (high), for  $V_{GS}>V_{TN}$ , the gate would require a higher voltage than  $V_{DD}$

- If an PMOS transistor's input were  $V_{SS}$  (low), for  $V_{GS} < V_{TP}$ , the gate would require a lower voltage than  $V_{SS}$

$\ensuremath{\mathsf{AND}}/\ensuremath{\mathsf{OR}}$  requires more area, power, time

Transistors in digital systems

Solutions

Transistors Non-ideality of NMOS/PMOS transistors

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

Solutions

S

- Recall that NMOS transmits low values easily...

- ... transmits high values poorly

- PMOS transmits high values easily...

- . . . transmits low values poorly

Transistors in digital systems

Homework

Tvo-level logic

Homework

Tvo-Stransistor

NMOS transistor

Robert Dick

Advanced Digital Logic Design

Switches

CMOS

AMD and OR are harder than NAND and NOR

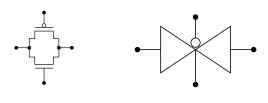

Transmission gates

Transistors in digital systems

Homework

Two-level logic

Homework

Two-level logic

Homework

Two-level logic

Homework

Transmission gates

Transmission gates

Transmission gates

$\ensuremath{\mathsf{NAND/NOR}}$  easy to build in CMOS

Transistors in digital systems

Homework

Two-level ligit CMOS

CMOS transmission gates (switches)

Advanced Digital Logic Design

Switches

CMOS

Advanced Digital Logic Design

Switches

CMOS

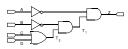

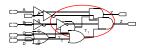

Transmission gates (switches)

- NMOS is good at transmitting 0s

Bad at transmitting 1s

- PMOS is good at transmitting 1sBad at transmitting 0s

- To build a switch, use both: CMOS

Robert Dick Advanced Distrial Logic Design 29 Robert Dick Advanced

# Two-level logic MAND and OR are harder than NAND and NOR Transmission gates CMOS transmission gate (TG)

Transistors in digital systems

Two-level togic

What can we build with TGS?

Advanced Digital Logic Design

Switches

CMOS

ATVANCED TO A TRANSISSION BASES

CMOS

Transmission gates

• Anything...try some examples.

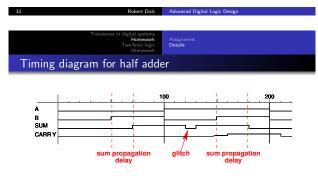

- Delay between input and output changes

- Delay is sensitive to circuit path

- Outputs may temporarily be incorrect before stabilizing

- Glitches caused by hazards

- The Mentor Graphics CAD system has many components

- You will use a portion of the tools in this course

- Falcon Design Framework

- Design Architect for entering logic designs

- Quicksim for simulating the designs

- $\bullet$  QuickHDL for entering and simulating the VHDL designs

- You will soon be working on lab 1, a Mentor Graphics tutorial

Transistors in digital systems

Homeourk

Two-level logic

Homeourk

Two-level logic

Homeourk

Transmission gates

Switches

CMOS

AND and OR are harder than NAND and NOR

Transmission gates

- Walks you through the design and simulation of an exclusive-or (XOR) gate

- Due on 2 October

- Start early, especially if you are not familiar with Unix

- This lab requires a lot of tasks that are extremely easy the second time you do them, but slow and error-prone the first time through

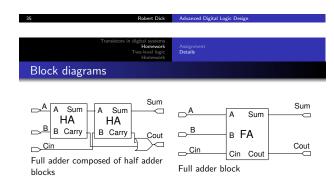

- Structural organization of the design

- Hierarchical functional black boxes with input/output connections

- Concentrates on how the components are organized by wiring

- $\bullet$  Typing "source /vol/ece303/mgc.env" in the ECE filesystem will set up environment for ECE 303 labs

- Typing "dmgr" for Design Manager will open a window allowing several other Mentor Graphics to be run

- Mentor Graphics is not a single tool tool but a series of design tools that uses object oriented data representation to simplify the design process

dvanced Digital Logic Design

40 Robert Dick Advanced Digital Logic Design

#### Mentor Graphics introduction

- Data created in one tool (e.g., Design Architect) can be exported to another tool (e.g., Quicksim) for simulation

- A schematic is a diagram of a circuit

- Warning: Don't use OS commands to move directories or files

- Design Manager needs to update other files when things are moved

41 Robert Dick

Transistors in digital systems

Two-level logic

Homework

Viewpoint definition

Advanced Digital Logic Design

Assignment

Details

Details

- A viewpoint is a set of rules specifying a design's configuration

- Specifies the subset of data to use as input for a specific tool

- Allows a block to be described in different ways within different viewpoints

- One can evaluate the impact of a low-level design decision on high-level design

- For now, one viewpoint per design should be sufficient

Transistors in digital systems

Homeours

Two-level logic

Homeours

DeMorgan's laws

$$\overline{(a+b)} = \overline{a} \ \overline{b}$$

$$\overline{ab} = \overline{a} + \overline{b}$$

$$\overline{f(x_1, x_2, \dots, x_n, \cdot, +)} = f(\overline{x_1}, \overline{x_2}, \dots, \overline{x_n}, +, \cdot)$$

- Those xs could be functions

- Apply in stages

- Top-down

## Component definition

Data created by Design Architect is saved as components

- Models describing functional and graphical aspects

- Component data is composed of a schematic and a symbol

- A symbol is a graphical model with input and output pins

- A schematic is a functional model describing the relationship between output and input values

- Set of elements, B

- $\bullet$  Binary operators,  $\{$  [ AND,  $\land$  , \*,  $\cdot$  ], [ OR,  $\lor$  , + ]  $\}$

- We'll prefer · and +

- · frequently omitted

- $\bullet$  Unary operator, [ NOT, ',  $\overline{o}$  ]

| 46 Robert Dick                                                               | Advanced Digital Logic Design |

|------------------------------------------------------------------------------|-------------------------------|

|                                                                              |                               |

| Transistors in digital system<br>Homewor<br><b>Two-level logi</b><br>Homewor | Simplification                |

| Axioms of Boolean algebra                                                    |                               |

$$\exists x,y \in B \text{ s.t. } x \neq y$$

distributive laws

$$\forall x,y,z \in B \quad x + (yz) = (x+y)(x+z)$$

$$x(y+z) = xy + xz$$

compliment

$$x \in B \qquad x\overline{x} = 0$$

$$x + \overline{x} = 1$$

| 48 Robert Dick                                                                    | Advanced Digital Logic Design                      |

|-----------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                   |                                                    |

| Transistors in digital systems<br>Homework<br><b>Two-level logi</b> c<br>Homework | Boolean algebra<br>Simplification<br>Karnaugh maps |

| DeMorgan's laws example                                                           |                                                    |

$$\overline{a + bc}$$

$$\overline{a} \cdot \overline{(bc)}$$

$$\overline{a} \cdot (\overline{b} + \overline{c})$$

$\bullet$  Expression using only  $\cdot,\ +,\ \text{and}\ '$

- AND

- a

b

a b

0

0

0

0

1

0

1

0

0

1

1

1

$\mathsf{a}\; \mathit{AND}\; \mathsf{b} = \mathsf{a}\; \mathsf{b}$ Will show Karnaugh map later

|  |  | Robert | Di |

|--|--|--------|----|

|  |  |        |    |

Truth table

Symbolic • Karnaugh map

• More useful as visualization and optimization tool

OR

51

| ransistors in digital systems<br>Homework<br><b>Two-level logic</b><br>Homework | Boolean algebra<br>Simplification<br>Karnaugh maps |  |

|---------------------------------------------------------------------------------|----------------------------------------------------|--|

|                                                                                 |                                                    |  |

$$\begin{array}{c|c|c|c|c} a & b & a+b \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \end{array}$$

$$\mathsf{a}\,\,\mathit{OR}\,\,\mathsf{b}=\mathsf{a}+\mathsf{b}$$

NOT

$$\begin{array}{c|c} a & \overline{a} \\ \hline 0 & 1 \\ 1 & 0 \end{array}$$

$$NOT a = \overline{a}$$

Different representations possible

$$Z = ((C + D) \overline{B}) \overline{A}$$

$$Z = (C + D) \overline{A} \overline{B}$$

Simplifying logic functions

- Minimize literal count (related to gate count, delay)

- Minimize gate count

- Minimize levels (delay)

- Trade off delay for area

- Sometimes no real cost

Proving theorems = simplification

Prove  $XY + X\overline{Y} = X$

$XY + X\overline{Y} = X(Y + \overline{Y})$  $X(Y + \overline{Y}) = X(1)$

X(1) = X

distributive law complementary law

identity law

Prove X + XY = X

X + XY = X1 + XYX1 + XY = X(1 + Y)

Proving theorems = simplification

identity law distributive law

X(1+Y)=X1

identity law

X1 = X

identity law

- Literals

- Each appearance of a variable (complement) in expression

- Fewer literals usually implies simpler to implement

- E.g.,  $Z = A\overline{B}C + \overline{A}B + \overline{A}B\overline{C} + \overline{B}C$

- Three variables, ten literals

NANDs and NORs

- Can be implemented in CMOS

- More on this later

- $X \text{ NAND } Y = \overline{XY}$

- X NOR  $Y = \overline{X + Y}$

- Do we need inverters?

Transistors in digital systems

Homeovik

Two-level logic

Homeovik

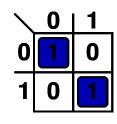

Karnaugh maps (K-maps)

Advanced Digital Logic Design

Boolean algebra

Simplification

Karnaugh maps

- Fundamental attribute is adjacency

- Useful for logic synthesis

- Helps logic function visualization

63 Robert Dick Advanced Digital Logic Design

Transistors in digital systems Homeoork Two-level logic Design

Transistors in digital systems Homeoork Two-level logic School algebra Simplification Company of Co

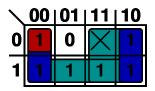

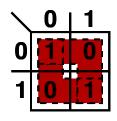

$(\overline{a} \ \overline{b}) + (a \ b)$

Transistors in digital systems

Homework

Two level logic

Homework

K-map example

Robert Dick

Advanced Digital Logic Design

Bookean algebra

Simplification

Karnaugh maps

- Minimize  $f(a, b, c, d) = \sum (1, 3, 8, 9, 10, 11, 13)$

- $f(a, b, c, d) = a \overline{b} + \overline{b} d + a \overline{c} d$

Transistors in digital systems

Homework

Too-level logic

Homework

Karnaugh maps

Advanced Digital Logic Design

Roolean algebra

Simplification

Kamaugh maps

Transistors in digital systems

Liberton Montesork

Two level logic

Hontework

Implicants

Advanced Digital Logic Design

Advanced Digital Logic Design

Boolean algebra

Simplification

Karnaugh maps

#### esseptialnepiliqalitapticant

Prime implicants are not covered by other implicants Essential prime implicants uniquely cover minterms

66 Robert Dick Advanced Digital Logic Design

Transistors in digital systems

Homework

Two-level logic

Homework

Two-level logic

K-map simplification technique

#### For all minterms

- Find maximal groupings of 1's and X's adjacent to that minterm.

- Remember to consider top/bottom row, left/right column, and corner adjacencies.

- These are the prime implicants.

Robert Dick Adv

Advanced Digital Logic Design

Robert Dic

Advanced Digital Logic Design

K-map simplification technique

### K-map simplification technique

- Revisit the 1's elements in the K-map.

- If covered by single prime implicant, the prime is essential, and participates in final cover.

- The 1's it covers do not need to be revisited.

- If there remain 1's not covered by essential prime implicants,

- Then select the smallest number of prime implicants that cover the remaining 1's.

- This can be difficult for complicated functions.

- Will present an algorithm for this in a future lecture.

$$(\overline{a} + b) \cdot (a + \overline{b})$$

POS K-map techniques

• Direct reading by covering zeros and inverting variables

- Invert function

- Do SOP

- Invert again

- Apply DeMorgan's laws

POS K-map example

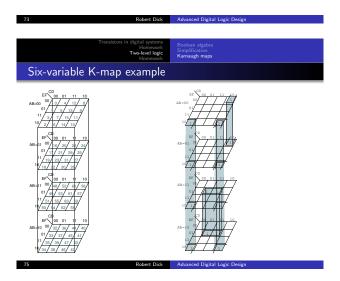

Six-variable K-map example

• Minimize  $f(a, b, c) = \prod (2, 4, 5, 6)$

•  $f(a,b,c) = (\overline{b} + c)(\overline{a} + b)$

$z(a, b, c, d, e, f) = \sum (2, 8, 10, 18, 24, 26, 34, 37, 42, 45, 50, 53, 58, 61)$

Six-variable K-map example

$z(a,b,c,d,e,f) = \overline{d} \ e \ \overline{f} + ad \ \overline{e} \ f + \overline{a} \ C \ \overline{d} \ \overline{f}$

#### DON'T CARE logic

- All specified Boolean values are 0 or 1

- However, during design some values may be unspecified

- Don't care values  $(\times)$

- At ×s allow circuit optimization

- Incompletely specified functions allow optimization

- Input can never occur

- This can happen within a circuit

- Some modules will not be capable of producing certain outputs

- Minimize  $f(a, b, c, d) = \sum (1, 3, 8, 9, 10, 11, 13) + d(5, 7, 15)$

- $f(a, b, c, d) = a \overline{b} + d$

- Michael R. Garey and David S. Johnson. Computers and Intractability: A Guide to the Theory of NP-Completeness. W. H. Freeman & Company, NY, 1979

- Chapter 1, Sections 1-5

- Introduces the concept of intractable problems

- Many problems in digital design are intractable

- Too hard to solve optimally in a reasonable amount of time

- Use heuristics

Instead, leave these values undefined  $(\times)$

- Also called DON'T CARE values

- Allows any function implementing the specified values to be used

Output will be ignored for certain inputs

- Refer to M. Morris Mano and Charles R. Kime. Logic and Computer Design Fundamentals. Prentice-Hall, NJ, fourth edition, 2008

- http://www.writphotec.com/mano/

- CMOS supplement

- Optimization supplement

- qm.py at http://ziyang.eecs.northwestern.edu/~dickrp/tools.html

Computer Geek Culture

Python and perl