The Race Towards Future Computing Solutions

#### RRAM fabric for neuromorphic and in-memory computing applications

Mohammed Zidan and Wei Lu

**University of Michigan Electrical Engineering and Computer Science**

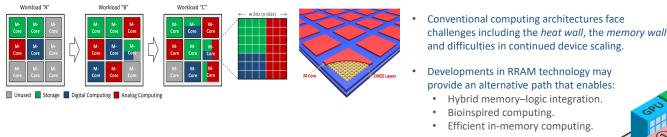

- Conventional computing architectures face challenges including the heat wall, the memory wall and difficulties in continued device scaling.

- Developments in RRAM technology may provide an alternative path that enables:

- Hybrid memory–logic integration. •

- Bioinspired computing.

- . Efficient in-memory computing.

Moore's Lav

Memory Wall Heat Wall

M. A. Zidan, J. P. Strachan, and W. D. Lu, Nature Electronics 1: 22-29 (2018)

Lu Group U. Michigan

Ľ

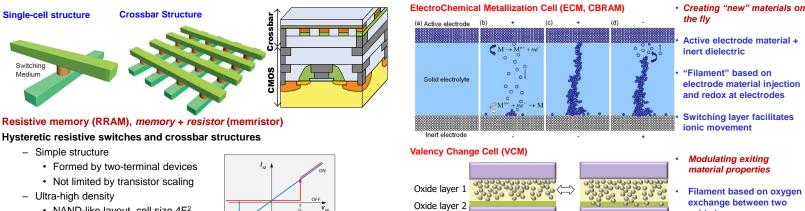

# **Two-Terminal Memory Devices and Crossbar Arrays**

#

## Physically reconfigurable materials and devices: Resistive Memory

*"0"*

- NAND-like layout, cell size 4F<sup>2</sup>

- · Terabit potential

- Large connectivity

- Memory, logic/neuromorphic applications

Electrode plays minor role

Lu Group Yuchao Yang and Wei Lu, Nanoscale, 5, 10076 (2013) U. Michigan

**``1**^

oxide layers

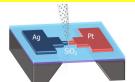

#### **Visualization of Filament**

#### **Driving lons with Electric Field**

•Ag/SiO<sub>2</sub>/Pt structure, sputtered SiO<sub>2</sub> film •The filament grows from the IE backwards toward the AE •Branched structures were observed with wider branches pointing to the AE

Partially formed filaments

Lu Group Y. Yang, Gao, Chang, Gaba, Pan, and W. Lu, Nature Communications, 3, 732, 2012. 5 <sup>Lu</sup> المستقدمة ال

Jo, Kim, Lu Nano Lett. 9, 496-500 (2009).

Filament formation is a thermally activated process. Activation energy reduced by applied bias. •Speed is a ca. exponential function of voltage

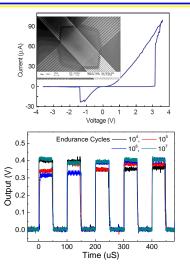

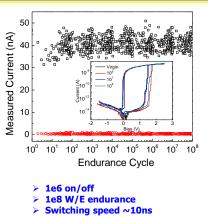

#### **Resistance Switching Characteristics**

Jo, Kim, W. Lu, Nano Lett., 8, 392 (2008)

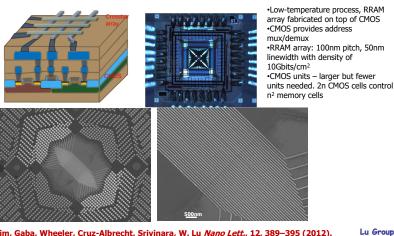

Integrated RRAM Crossbar/CMOS System

Kim, Jo, W. Lu, *Appl. Phys. Lett.* 96, 053106 (2010) Lu Group Kim, Gaba, Wheeler, Cruz-Albrecht, Srivinara, W. Lu *Nano Lett.*, 12, 389–395 (2012).

U. Michigan

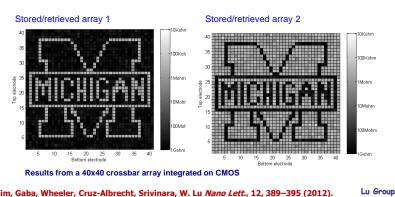

#### Integrated Crossbar Array/CMOS System

- Crossbar array operation, array written followed by read

- Programming and reading through integrated CMOS address decoders

- Each bit written with a single pulse

Kim, Gaba, Wheeler, Cruz-Albrecht, Srivinara, W. Lu Nano Lett., 12, 389–395 (2012).

## From Lab to Fab - Crossbar RRAM Technology

- CMOS Compatible

- 3D Stackable, Scalable Architecture Low thermal budget process

- · Architectures proven include multiple Via schemes and Subtractive etching

- Crossbar Inc founded in 2010, \$100M VC funding to date

- Commercial Products offered in 2016 based on 40nm CMOS

**Cr**essbar

Lu Group U. Michigan

#### Hybrid Integration of Memory with Logic 1T1R and 1TnR 3D stackable memory arrays

U. Michigan

| Embedded memory with            | SCM with 1T1R or <b>1TnR</b> | Mass storage     | FPGC configurable logic, |

|---------------------------------|------------------------------|------------------|--------------------------|

| 1T1R                            |                              | with <b>1TnR</b> | CPU with <b>1T1R</b>     |

| Code/Config/<br>NVRAM<br>Memory | SCM/Mass Sto                 |                  | M2<br>M2<br>Periphery    |

- Monolithic logic/memory integration

- Different memory components integrated on the same chip

- Flexibility of speed/density/cost

### Improving Computing Efficiency using RRAM Arrays

- Bring memory as close to logic as possible, still largely based on conventional architecture

- · Neuromorphic computing in artificial neural networks

- More bio-inspired, taking advantage of the internal ionic dynamics at different time scales

- Other compute applications based on vector-matrix multiplications

Towards a general in-memory computing fabric based on a common physical substrate

> Lu Group U. Michigan

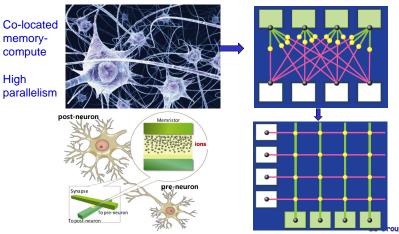

### **RRAM Based Neural Network Hardware**

## **Neuromorphic Computing with RRAM Arrays**

Synapse - reconfigurable two-terminal resistive switches

U. Michigan S. H. Jo, T. Chang, I. Ebong, B. Bhavitavya, P. Mazumder, W. Lu, Nano Lett. 10, 1297 (2010).

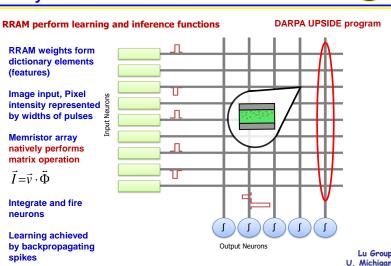

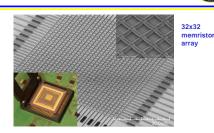

#### **Hardware Implementation**

- **Checkerboard pattern**

- 32 x 32 array •

- **Direct storage and read out**

- No read-verify or re-programming

- Sheridan et al., Nature Nanotechnology 12, 784–789 (2017)

Lu Group U. Michigan Training images

Training

Sheridan et al., Nature Nanotechnology 12, 784 -789 (2017) 9 Training Images 128x128px 4x4 patches Trained in random order

> Lu Group U. Michigan 18

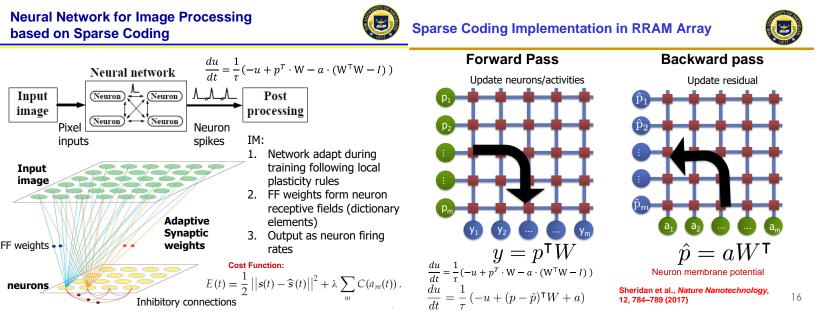

Image Reconstruction with RRAM Crossbar

# Arrays

Improving Computing Efficiency using RRAM

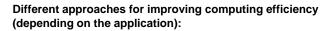

Different approaches for improving computing efficiency (depending on the application):

- Bring memory as close to logic as possible, still largely based on conventional architecture

- · Neuromorphic computing in artificial neural networks

- More bio-inspired, taking advantage of the internal ionic . dynamics at different time scales

- · Other compute applications based on vector-matrix multiplications

Towards a general in-memory computing fabric based on a common physical substrate

> Lu Group U. Michigan

Sheridan et al., Nature Nanotechnology 12, 784–789 (2017)

Lu Group U. Michigan

# Arithmetic Applications: Numerical Simulation

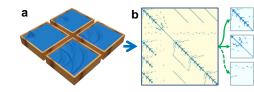

# Hardware Prototyping

» Hardware Test bench

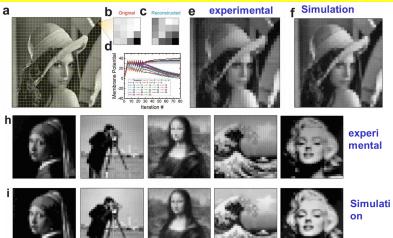

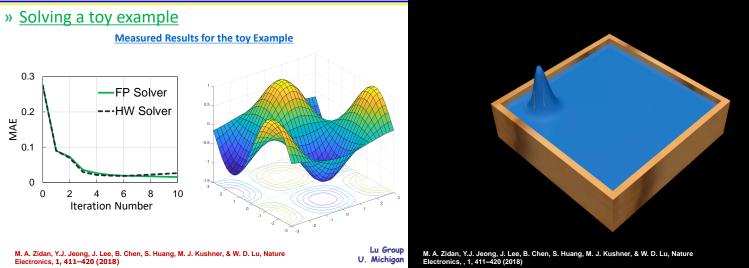

#### Solving partial-differential equations (PDEs)

Solving an A<sup>·</sup>x=b problem in matrix form

• A second order Poisson equation as a toy example,

$$\nabla^2 u = -2 \cdot \sin(x) \cdot \cos(y)$$

• The problem is solved using finite difference (FD), where matrix can be sliced into a set of few similar slices.

• The test board consists of: (i) RRAM crossbar, (ii) DACs to control the input signals, (iii) sense amplifiers and ADCs to sample the output current, (iv) MUXs to route the signals, and (v) FPGA to enables the software interface and control.

M. A. Zidan, Y.J. Jeong, J. Lee, B. Chen, S. Huang, M. J. Kushner, & W. D. Lu, Nature Electronics, 1, 411–420 (2018)

Lu Group U. Michigan

## **Hardware Prototyping**

Lu Group

U. Michigan

## » Results Reconstructed as a 3D Animation

# $(\mathbf{E})$

## **General In-Memory Computing Fabric**

# The Race Towards Future Computing Solutions

#### Memory-Computing Unit (MPU)

- "General" purpose by design: the same hardware supports different tasks low precision or high precision. Not just an neuromorphic accelerator

- Dense local connection, sparse global connection

- Run-time, dynamically reconfigurable. Function defined by software.

M. Zidan, Y. Jeong, J. H. Shin, C. Du, Z. Zhang, and W. D. Lu, IEEE Trans Multi-Scale Comp Sys, DOI 10.1109/TMSCS.2017.2721160 (2017)

M. A. Zidan, J. P. Strachan, and W. D. Lu, Nature Electronics 1: 22–29 (2018)

Lu Group U. Michigan M. A. Zidan, J. P. Strachan, and W. D. Lu, Nature Electronics 1: 22–29 (2018) M. Zidan, Y. Jeong, J. H. Shin, C. Du, Z. Zhang, and W. D. Lu, IEEE Trans Multi-Scale Comp Sys, DOI 10.1109/TMSCS.2017.2721160 (2017)

Lu Group U. Michigan

1 Better Memory/Storage

×,

Moore's La

② Bio-Inspired Computing

③ In-Memory Computing

Memory Wall Heat Wall

# Summary

Different approaches for improving computing efficiency (depending on the application):

- Bring memory as close to logic as possible, still largely based on conventional architecture

- · Neuromorphic computing in artificial neural networks

- More bio-inspired, taking advantage of the internal ionic dynamics at different time scales

- Other tasks based on vector-matrix multiplications

Towards a general in-memory computing fabric based on a common physical substrate

Lu Group U. Michigan