## Embedded System Design and Synthesis

Robert Dick

http://robertdick.org/esds/ Office: EECS 2417-E Department of Electrical Engineering and Computer Science University of Michigan

# Transition

Discuss Joseph Polastre, Robert Szewczyk, Alan Mainwaring, David Culler, and John Anderson. Analysis of wireless sensor networks for habitat monitoring. In C. S. Raghavendra, Krishna M. Sivalingam, and Taieb Znati, editors, *Wireless Sensor Networks*, chapter 18, pages 399–423. Springer US, 2004.

Embedded System Design and Synth-

- Practice exam.

- Impact of technology trends.

| Evolution of computation                              | Evolution of computation                                                                                                                                                                                                           |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Carbon nanotubes                                      | Carbon nanotubes                                                                                                                                                                                                                   |

| Single-electron tunneling transistors                 | Single-electron tunneling transistors                                                                                                                                                                                              |

| Homework                                              | Homework                                                                                                                                                                                                                           |

| Two major sources of changing problems                | Evolution of computation                                                                                                                                                                                                           |

| New implementation technologies.<br>New applications. | <ul> <li>1800s: Mechanical</li> <li>Late 1800s-early 1900s: Electro-mechanical</li> <li>Early 1900s-mid 1900s: Vacuum tube electronic</li> <li>Mid 1900s-late 1900s: Bipolar (TTL)</li> <li>Late 1900s-early 2000s: MOS</li> </ul> |

| Impact      | Single-elect                                                       | Evolution of computation<br>Carbon nanotubes<br>tron tunneling transistors<br>Homework<br>g on delay |                              |                  |   |

|-------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------|------------------|---|

| Delay (Sec) | 1.E+01<br>1.E-01<br>1.E-03<br>1.E-05<br>1.E-07<br>1.E-09<br>1.E-11 | vacur<br>• ↓<br>• ↓<br>• ↓<br>• ↓                                                                    | um tube<br>Transistor<br>IMO | S<br>СМО<br>2000 | 5 |

Carbon nanotubes

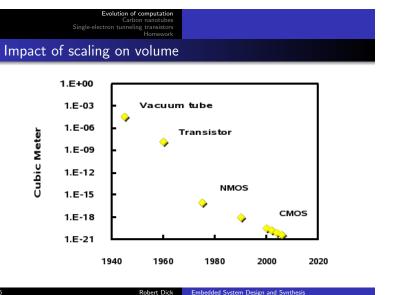

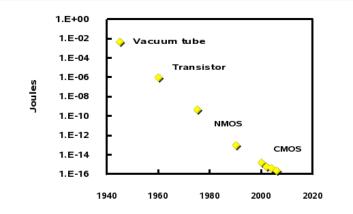

### Impact of scaling on energy consumption

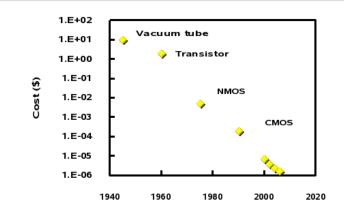

# Impact of scaling on price

### Carbon nanotubes Single-electron tunneling transistors Homework

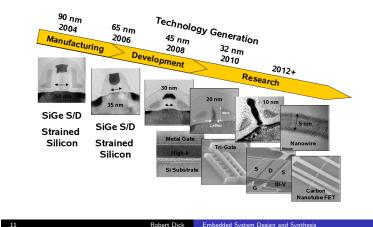

| Scaling trends |

|----------------|

|----------------|

| High Volume<br>Manufacturing | 2004   | 2006    | 2008   | 2010                          | 2012           | 2014      | 2016     | 2018   |

|------------------------------|--------|---------|--------|-------------------------------|----------------|-----------|----------|--------|

| Technology Node<br>(nm)      | 90     | 65      | 45     | 32                            | 22             | 16        | 11       | 8      |

| Integration<br>Capacity (BT) | 2      | 4       | 8      | 16                            | 32             | 64        | 128      | 256    |

| Delay = CV/l<br>scaling      | 0.7    | ~0.7    | >0.7   | De                            | lay sca        | ling will | slow do  | wn     |

| Energy/Logic Op<br>scaling   | >0.35  | >0.5    | >0.5   | Energy scaling will slow down |                |           | own      |        |

| Bulk Planar CMOS             | Hig    | h Proba | bility |                               |                | Low       | Probab   | oility |

| Alternate, 3D etc            | Low    | v Proba | bility |                               |                | High      | Probab   | oility |

| Variability                  | Medium |         |        | Hig                           | High Very High |           |          |        |

| Inter-Ir dielectric k        | ~3     | <3      |        | Redu                          | uce slov       | vly towa  | ırds 2-2 | .5     |

| RC Delay                     | 1      | 1       | 1      | 1                             | 1              | 1         | 1        | 1      |

| Metal Layers                 | 6-7    | 7-8     | 8-9    | 0.5                           | to 1 la        | yer per   | generat  | ion    |

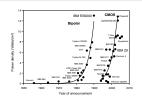

### Evolution of computation Carbon nanotubes Single-electron tunneling transistors Homework Device trends

### Carbon nanotub Single-electron tunneling transisto

Advantages of CMOS relative to prior technologies

Robert Dick Embedded System Design and Synth

Robert Dick

- Performance

- Gain, low noise

- Area

- Massive integration

- Power

- Reliability

- Fabrication difficulty & cost

# • 32 nm

• Power, thermal problems severe

Current status for CMOS

- Fabrication cost per design high

- Potential reliability problems in future

- Soft errors

- Electromigration, dielectric breakdown, etc.

- Process variation

- Soon: Discrete dopant problems

Evolution of a

Com

### Computing trends applications

### Advantages of alternative nanotechnologies

- Increased market volume and size for portable and embedded systems compared to general-purpose computers.

- Instructor's opinion: Embedded will grow in importance in the future.

- High-performance general-purpose computing will still matter.

Robert Dick Embedded System Design and Synt

• Much of the general-purpose computation will move to data centers.

May allow continued process scaling after CMOS scaling impractical.

Robert Dick Embedded System Design and Synt

- Candidates

- Carbon nanotube

- Nanowire Single electron tunneling transistors

Carbon nanotube

| n of                                   | f nar                     | losc              | ale t                                                                                      | techi                         | nolog                                                    | ies                                                        |                                        |                                           |

|----------------------------------------|---------------------------|-------------------|--------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------|------------------------------------------------------------|----------------------------------------|-------------------------------------------|

|                                        |                           |                   |                                                                                            |                               | 0                                                        |                                                            |                                        |                                           |

|                                        | Table :                   | 9 Emergi          | ng Research I                                                                              | ogic Devices-                 | Demonstrated                                             | Projected Par                                              | ameters                                |                                           |

| D                                      | Verice                    | 4                 | -                                                                                          | <u>چ</u>                      | -D+D-                                                    | ٢                                                          | $\bigcirc$                             | -9                                        |

|                                        |                           | FET (8)           | 1D structures                                                                              | Resonant<br>Tunneling Devices | SET                                                      | Molecular                                                  | Ferromagnetic<br>logic                 | Spin transist                             |

| τ                                      | )per                      | Si CMOS           | CNT FET<br>NW FET<br>NW hetero-<br>structures<br>Crosshar<br>nanostructure                 | RTD-FET<br>RTT                | SET                                                      | Crossbar latch<br>Molecular<br>transistor<br>Molecular QCA | Moring domain<br>wall<br>M: QCA        | Spin transie                              |

| Supported                              | Architectures             | Conventional      | Conventional<br>and Cross-her                                                              | Correctional<br>and CNN       | CNN                                                      | Cross-bar and<br>QCA                                       | CNN<br>Reconfigure<br>logic and<br>QCA | Convention                                |

| Cell Size                              | Projected                 | 100 nm            | 100 nm [C]                                                                                 | 100 nm [C]                    | 40 nm [L]                                                | 10 nm [Q]                                                  | 140 nm [U]                             | 100 nm [C                                 |

| (spatial pitch)                        | Demonstrated              | 590 nm            | ~1.5 µm [D]                                                                                | 3µm (H)                       | ~700 nm [M]                                              | ~2µm [R]                                                   | 250 nm [V, W]                          | 100 µm [X                                 |

| Density                                | Projected                 | 1E10              | 4.5E9                                                                                      | 4.5E9                         | 6E10                                                     | 1E12                                                       | 5E9                                    | 4.5E9                                     |

| (device/cm <sup>2</sup> )              | Demonstrated              | 2.8E8             | 467                                                                                        | 1E7                           | 2E8                                                      | 2E7                                                        | 1.6E9                                  | 1E4                                       |

| Switch Speed                           | Projected                 | 12 THz            | 6.3 THz [E]                                                                                | 16 THz [I]                    | 10 THz [M]                                               | 1 THz [S]                                                  | 1 GHz [U]                              | 40 GHz [Y                                 |

|                                        | Demonstrated              | 1 THz             | 200 MHz [F]                                                                                | 700 GHz [J]                   | 2 THz [N]                                                | 100 Hz [R]                                                 | 30 Hz [V, W]                           | Not known                                 |

| Circuit Speed                          | Projected<br>Demonstrated | 61 GHz<br>5.6 GHz | 61 GHz [C]<br>220 Hz [G]                                                                   | 61 GHz [C]<br>10 GHz [Z]      | 1 GHz [L]<br>1 MHz [F]                                   | 1 GHz [Q]<br>100 Hz [R]                                    | 10 MHz [U]<br>30 Hz [V]                | Not know<br>Not know                      |

| Switching                              | Projected                 | 3E-18             | 3E-18                                                                                      | >3E-18                        | 1×10 <sup>-18</sup> [L]<br>[>1.5×10 <sup>-17</sup> ] [O] | 5E-17 (T)                                                  | -1E-17 [V]                             | 3E-18                                     |

| Evergy, J                              | Demonstrated              | 1E-16             | 1E-11 [G]                                                                                  | 1E-13 [K]                     | 8×10 <sup>-17</sup> [P]<br>[>1.3×10 <sup>-14</sup> ][O]  | 3E-7 (R)                                                   | 6E-18 [W]                              | Not know                                  |

| Binary                                 | Projected                 | 238               | 238 [C]                                                                                    | 238 [C]                       | 10                                                       | 1000                                                       | 5E-2                                   | Not know                                  |

| Throughput,<br>GBitins/cw <sup>2</sup> | Demonstrated              | 1.6               | 1E-8                                                                                       | 0.1                           | 2E-4                                                     | 2E-9                                                       | 5E-8                                   | Not know                                  |

| Operations                             | al Temperature            | RT                | RT                                                                                         | 4.2 - 300 K                   | 20 K [L]                                                 | RT                                                         | RT                                     | RT                                        |

| Materi                                 | ials System               | Si                | CNT,<br>Si, Ge, III-V,<br>In <sub>2</sub> O <sub>2</sub> , ZnO,<br>TIO <sub>2</sub> , SIC, | III-V<br>Si-Ge                | III-V<br>Si                                              | Organic<br>molecules                                       | Ferromagnetic<br>alloys                | Si, III-V,<br>complex<br>metals<br>oxides |

| Research acti                          | vite (A)                  |                   | 171                                                                                        | 88                            | 65                                                       | 204                                                        | 25                                     | 102                                       |

Credit to ITRS'05 report on Emerging Research Devices.

Robert Dick Embedded System Design and Sy

Robert Dick Embedded S

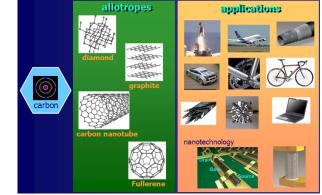

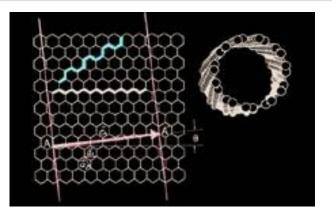

### Evolution of computation Carbon nanotubes Single-electron tunneling transistors Homework CNT classes

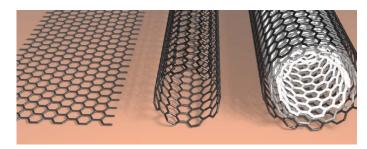

Graphene

Single-walled CNT

Multi-walled CNT

## Carbon n

## Chirality

# Carbon nanotubes

## Metallic and semiconducting CNTs

| Zigzag (semi-conducting) | Armchair (  | metallic)                              |  |

|--------------------------|-------------|----------------------------------------|--|

| Zigzag (semi-conducting) |             |                                        |  |

| Zigzag (semi-conducting) |             |                                        |  |

| Zigzag (semi-conducting) |             | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |  |

|                          |             |                                        |  |

|                          | Zigzag (sei | ni-conducting)                         |  |

|                          | Zigzag (ser | ni-conducting)                         |  |

Embedded System Design and Sy

| Homework                                                  |  | CNTs compared with Cu                                                      |

|-----------------------------------------------------------|--|----------------------------------------------------------------------------|

| n of computation<br>arbon nanotubes<br>neling transistors |  | Evolution of computa<br>Carbon nanoto<br>Single-electron tunneling transis |

- Metallic or semiconducting.

- Diameter: 0.4–100 nm.

- Length: up to millimeters.

- Ballistic transport.

CNT properties

- Excellent thermal conductivity.

- Very high current density.

- High chemical stability.

- Robust to environment.

- Tensile strength: 45 TPa.

- Steel is 2 TPa.

- Temperature stability

- 2,800°C in vacuum.

- 700°C in air.

| Property                         | CNT                                | Cu             |

|----------------------------------|------------------------------------|----------------|

| Max I dens. (A/cm <sup>2</sup> ) | $>1	imes10^9$ (Wei et al., APL'01) | $1 	imes 10^7$ |

| Thermal cond. (W/mK)             | 5,800 (Hone et al., Phy Rev B'99)  | 385            |

| Mean free path (nm)              | > 1.000 (McEuen et al. T Nano'02)  | 40             |

Carbon nanotub

| Carbon nanotubes<br>Single-electron tunneling transistors<br>Homework |                                          |           |

|-----------------------------------------------------------------------|------------------------------------------|-----------|

| IRAM                                                                  |                                          |           |

| carbon nanotube ribbons                                               | supports<br>Oxide layer<br>silicon wafer | Off state |

- Uses Van der Waals forces.

- Non-volatile.

- SRAM-like speed.

- DRAM-like density.

- Ready for market in 2007 (and 2008, and 2009, and 2010, and 2011).

Robert Dick Embedded Sys

• IEEE Spectrum loser of the year. Why?

### Single-electro

## Power challenges

High-performance applications: energy cost, temperature, reliability Portable embedded systems: battery lifetime

#### Evolution of computation Carbon nanotubes

### What does history teach us about power consumption?

### Device innovations have been the most effective method

- Vacuum tube to semiconductor device in the 1960s

- Bipolar device to CMOS transistor in the 1990s

Based on diagram by C. Johnson, IBM Server and Technology Group

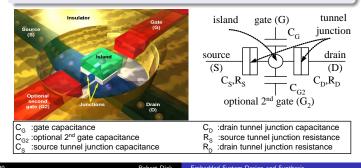

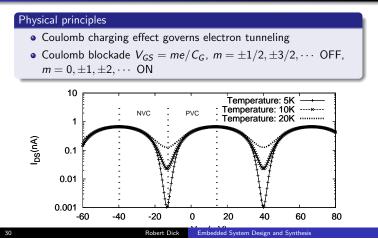

# Single electron tunneling transistor structure

### Device structure

- Island, terminals (source, drain, gate)

- Electron tunneling through tunneling junctions

Carbon nanotubes Single-electron tunneling transistors

Single electron tunneling transistor behavior

#### Carbon nanotubes Single-electron tunneling transistors

### SET properties and challenges

| Jltra | low | power |  |

|-------|-----|-------|--|

|-------|-----|-------|--|

• Projected energy per switching event  $(1 \times 10^{-18} \text{ J})$

### Room temperature and fabrication challenge

Electrostatic charging energy must be greater than thermal energy

•

$$e^2/C_{\Sigma} > k_B T$$

• Requires  $e^2/C_{\sum} > 10k_BT$  or even  $e^2/C_{\sum} > 40k_BT$

### Carbon nanotubes Single-electron tunneling transistors

### SET properties and challenges

### Performance challenge

- Electrons must be confined in the island

- $R_S, R_D > h/e^2, \ h/e^2 = 25.8 \, \mathrm{k}\Omega$

- High resistance, low driving strength

### Reliability concerns

- Tunneling between charge traps cause run-time errors

- Unknown before fabrication

- Device technology: Improved by silicon islands

- Reliable design: Post-fabrication adaptation

- Run-time error correction

|                 | Carbon    | Hallot |

|-----------------|-----------|--------|

| Single-electron | tunneling | transi |

|                 |           |        |

|                 |           |        |

### Summary

- CMOS will be mainstream for years to come, but not forever.

- The meaning of integrated circuits will change in the future.

- Circuit and logic design fundamentals will still apply.

- Some rules, e.g., difficulty of implementing non linearly separable functions, may change.

- You will each need to adapt as the rules governing device behavior change, but this will be much faster now that you have a foundation.

### Homework

- Due 20 October: Mini-project report.

- Due 20 October: Joseph Polastre, Robert Szewczyk, Alan Mainwaring, David Culler, and John Anderson. Analysis of wireless sensor networks for habitat monitoring. In C. S. Raghavendra, Krishna M. Sivalingam, and Taieb Znati, editors, *Wireless Sensor Networks*, chapter 18, pages 399–423. Springer US, 2004.

- Due 25 October: Main project proposal.

- Due 25 October: Email me one paper that you have read when working on your project that you think might be of interest to the entire class.

- Due 25 October: Ben W. Cook, Steven Lanzisera, and Kristofer S. J. Pister. SoC issues for RF smart dust. *Proc. IEEE*, 94(6), June 2006.

Robert Dick Embedded System Design and Synthesis