### Digital Integrated Circuits – EECS 312

http://robertdick.org/eecs312/

Teacher: Robert Dick Office: 2417-E EECS Email: dickrp@umich.edu Phone:

Cellphone:

734-763-3329 847-530-1824 GSI: Shengshou Lu Office: 2725 BBB luss@umich.edu Email:

### Review II

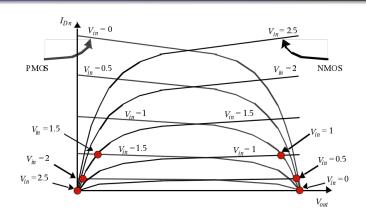

- How can the transfer curve for an inverter be derived from the I-V curves of the MOSFETs comprising it?

- What useful property relevant to the inverter load curve diagram holds in steady state but not when transients are considered?

- Is the inverter load curve diagram useful for analyzing dynamic systems?

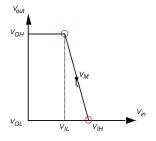

### $V_{IH}$ and $V_{IL}$

$$V_{IH} - V_{IL} = -\frac{V_{OH} - V_{OL}}{g} = \frac{-V_{DD}}{g}$$

(1)

$$V_{IH} = V_M - \frac{V_M}{g}$$

(2)

$$V_{IL} = V_M + \frac{V_{DD} - V_M}{g}$$

(3)

$$V_{IL} = V_M + \frac{V_{DD} - V_M}{g} \tag{3}$$

$$NM_H = V_{DD} - V_{IH} \tag{4}$$

$$NM_L = V_{IL} \tag{5}$$

### Review I

### Midterm exam

- May cover anything up to and including 3 October.

- Make sure you did the assigned reading.

- Look though all the on-line slides for anything surprising.

- Review lab and homework assignments.

- If you want to study with other students, please use mailing list to find partners.

- Posted old exams to website.

- No class on Tuesday.

### Inverter gain

Can find gain by taking  $\sigma V_{out}/\sigma V_{in}$  at  $V_{M}$ .

$$g = -\frac{1}{I_D(V_M)} \frac{k_n V_{DSAT_n} + k_p V_{DSAT_p}}{\lambda_n - \lambda_p}$$

$g pprox rac{1+r}{\left(V_M - V_{Tn} - rac{V_{DSATn}}{2}\right)\left(\lambda_n - \lambda_p\right)}$

#### Inverter noise margins Inverter dynamic behavior Midterm review

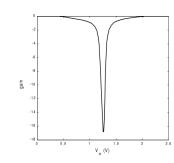

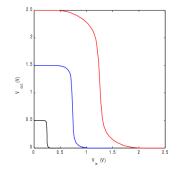

### Change in transfer curve (and gain) with $V_{DD}$

Robert Dick

Digital Integrated Circuits

### Higher gain.

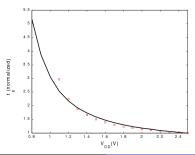

Subthreshold operation

- Lower current.

- Increased sensitivity to intrinsic noise.

- Increased sensitivity to fixed external noise.

Robert Di

Digital Integrated Circuits

overter dynamic behavior Midterm review

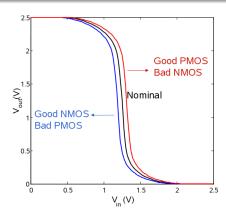

### Impact of process variation on inverter transfer function

Robert Dic

Digital Integrated Circuits

Inverter noise margi Inverter dynamic behavi Midterm revie Homewo

### Inverter performance

- Recall inverter propagation delay expression:  $t_p = 0.69RC$ .

- Either decrease R or decrease C.

- Effective R depends on  $V_{DD}$ .

Robert D

Digital Integrated Circuit

Inverter noise margins Inverter dynamic behavior Midterm review Homework

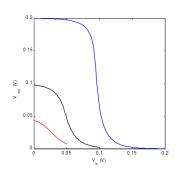

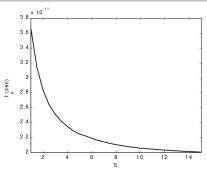

## Dependence of inverter delay on $\mathit{V}_{DD}$ I

$$\begin{split} t_{pHL} &= 0.69 \frac{3}{4} \frac{C_L V_{DD}}{I_{DSATn}} \\ t_{pHL} &= 0.52 \frac{L_n}{W_n} \frac{C_L V_{DD}}{k'_n V_{DSATn} (V_{DD} - V_{Tn} - V_{DSATn}/2)} \\ \text{If } V_{DD} \gg V_{Tn} + V_{DSATn}/2 \\ t_{pHL} &\approx 0.52 \frac{L_n}{W_n} \frac{C_L}{k'_n V_{DSATn}}. \end{split}$$

Why?

$$R_{eq} = \frac{1}{V_{DD}/2} \int_{V_{DD}/2}^{V_{DD}} \frac{V}{I_{DSAT}(1+\lambda V)} dV \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left(1 - \frac{7}{9} \lambda V_{DD}\right)$$

Inverter noise margin: Inverter dynamic behavio Midterm reviev Homeworl

### Dependence of inverter delay on $V_{DD}$ II

where

$$I_{DSAT} = k' \frac{W}{L} \left( (V_{DD} - V_T) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right).$$

Ignore channel length modulation factor  $\boldsymbol{\lambda}.$

- Fix  $R_L C_L$  and vary W.

- Eventually, self-loading dominates.

Robert Dick Digital Integrated Circ

• What is  $V_M$ ?

• What influence does an asymmetric change in inverter MOSFET resistance have on the  $V_{out} - V_{in}$  curve?

• Define noise margin and explain why it is a useful concept.

- What is inverter gain and how does it depend on  $V_{DD}$ ?

- What happens to inverter delay with decreasing  $V_{DD}$ ?

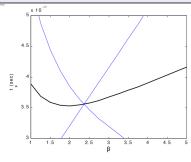

# Impact of $W_p/W_n$ ratio

Warning: Broken concept, especially for short-chain analysis.

- $\beta = W_p/W_n$ .

- $=\frac{t_{pLH}+t_{pHL}}{2}$

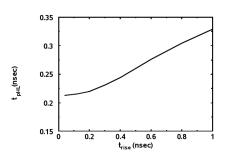

### Impact of rise time on delay

### Modeling rise time effects in inverter chains

$t_p^i = t_{step}^i + \eta t_{step}^{i-1}$

- $t_{step}^i$ : Delay of gate i in response to step input function.

- $\eta$ : Technology-dependent constant, generally near 0.25.

#### Midterm exam I

- Uses of digital systems.

- History of digital computing devices. Impact of technology improvements on performance, power consumption, size, and reliability. Bipolar to CMOS move.

- Power consumption equation and components of total power consumption. Check Slide 19 in lecture notes packet 2.

- Requirements for devices to permit use in digital system. Regeneration/restoration.

- MOSFET structure and layout.

- Schematic capture, e.g., using Cadence software.

- Resistance basics, and their application to MOSFET channels and metal wires.

Inverter noise margins nverter dynamic behavior Midterm review

### Midterm exam II

- Basic logic gate and transmission gate structures.

- MMOS, PMOS, and CMOS inverters.

- Diode structure and operation. Drift and diffusion. Difference between charge carriers and stationary ions. Doping.

- **4** MOSFET operation. Change in conditions (especially  $I_D$ ) with changing  $V_{GS}$ ,  $V_{DS}$ , and  $V_{SB}$ . MOSFET models. Cutoff, pinch-off, and velocity saturation.

- Subthreshold leakage and subthreshold operation.

- Process variation definition and influence on circuit behavior.

- High-level understanding of FinFET structure and reason for improved k.

- Steps in fabrication process. Dual damascene process.

- Understanding what design rules are.

Digital Integrated Circuit

Inverter noise margins overter dynamic behavior Midterm review

### **Upcoming topics**

- Inverter chains for driving large loads.

- Complex behavior in logic gate.

Inverter noise margin: Inverter dynamic behavio Midterm reviev

### Midterm exam III

- Packaging, MCMs, and board-level design. Implications of packaging and interconnect for performance.

- ${\color{red} @}$  Gate leakage. High- $\kappa$  dielectric. See assigned article.

- Transient diode and MOSFET behavior. Computing capacitances based on MOSFET structure and operating region.

- Derivation from inverter transfer curve from MOSFET I–V curves. Impact of inverter asymmetry on  $V_M$ .

- 4 Noise margin definitions and purpose. Gain definition.

Digital Integrated Circuits

Inverter noise margin Inverter dynamic behavic Midterm revies Homewor

### Homework assignment

• 3 October: Read sections 5.3, 5.4.1, and 5.4.2 in J. Rabaey,

A. Chandrakasan, and B. Nikolic. *Digital Integrated Circuits: A Design Perspective*.

Prentice-Hall, second edition, 2003.

- 3 October: Lab 2.

- 10 October: Homework 2 (which will help in your preparation for the midterm exam).

- 10 October: Read sections 5.4, 5.5, 5.6, and 3.5 in J. Rabaey,

A. Chandrakasan, and B. Nikolic. *Digital Integrated Circuits: A Design Perspective*.

Prentice-Hall, second edition, 2003.

Robert

Digital Integrated Circuits

Robert Dick

Digital Integrated Circuit