# Digital Integrated Circuits – EECS 312

# http://robertdick.org/eecs312/

| Teacher:<br>Office:<br>Email:<br>Phone:<br>Cellphone: | Robert Dick<br>2417-E EECS<br>dickrp@umich.edu<br>734–763–3329<br>847–530–1824 | GSI:<br>Office:<br>Email: | Shengshou Lu<br>2725 BBB<br>Iuss@umich.edu |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|--------------------------------------------|--|

|                                                       |                                                                                |                           |                                            |  |

|                                                       |                                                                                | 4D                        |                                            |  |

# Inverter transfer curves and parameter optimization Homework Announcement

- I will be in Montreal on Tuesday presenting a research paper at Embedded Systems Week.

- **②** I will lecture at the Friday discussion time and location.

- Mr. Lu will hold discussion at the Tuesday lecture time slot and location.

Robert Dick Digital Integrated Circuit

| Transistor dynamic behavior                         | Transistor dynamic behavior                         |

|-----------------------------------------------------|-----------------------------------------------------|

| Inverter switch model                               | Inverter switch model                               |

| Inverter transfer curves and parameter optimization | Inverter transfer curves and parameter optimization |

| Homework                                            | Homework                                            |

| Review                                              | Example low-k dielectric materials                  |

I How many metal layers are there in modern processes?

Robert Dick

Digital In

- What is the problem with isotropic etching?

- Sexplain a method of anisotropic etching.

- Why Cu?

- Why damascene?

- What is CMP?

- What is DRC?

- Still active area.

- Porous SiO<sub>2</sub>.

- Carbon-doped SiO<sub>2</sub>.

- Polymer.

Inverter transfer curves and parameter optimizati

# Synchronous integrated circuit organization

- Combinational networks separated by memory elements.

- When memory elements clocked, changed signals race through next stage.

- Clock frequency must be low enough to allow signal to propagate along worst-case combinational path in circuit.

Derive and explain.

Robert Dick Digital Integrated Cir

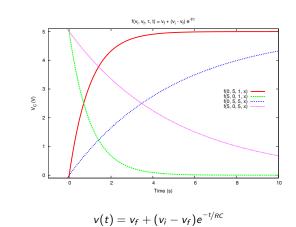

# RC curves

Robert Dick

Digital Integr

# Diode dynamic behavior

Robert Dick

Digital Integrated C

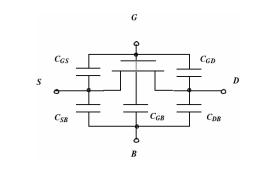

# **MOSFET** capacitances

Robert Dick Digital Integrated Circuit

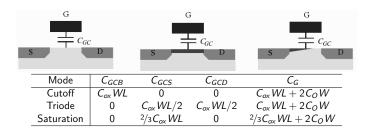

# Gate capacitance Polysilicon/metal gate Source Drain $n^+$ $n^+$ ∱Gate-bulk overlap Top view Ģate oxide n L Cross section

obert Dick Digital Integr

# Gate capacitance schematic

$C_O$  is the overlap capacitance.

Digital Ir

Robert Dick

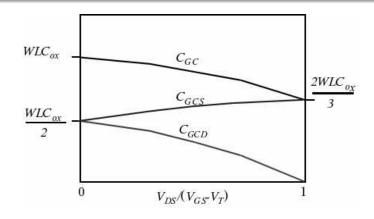

# Gate capacitance variation with $V_{GS}$ $C_{GC}$ WLC<sub>ox</sub> $C_{GCS} = C_{GCD}$ WLC<sub>ox</sub>

$C_{GCB}$

2

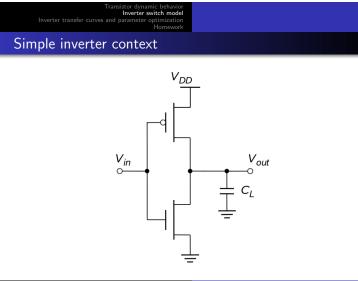

# Inverter Inverter transfer curves and parameter

# Gate capacitance variation with saturation

$V_{GS}$

### Inverter switch model

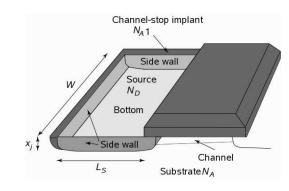

# Diffusion capacitance diagram

# Diffusion capacitance expression

$$C_{diff} = C_{bot} + C_{sw}$$

$$C_{diff} = C_j A + C_{jsw} P$$

$$C_{diff} = C_i L_S W + C_{isw} (2L_S + W)$$

- *C<sub>bot</sub>*: Bottom capacitance to substrate.

- $C_{sw}$ : Side-wall capacitances for three non-channel sides.

- $C_j$ : Junction capacitance constant in F/m<sup>2</sup> (base units).

- A: Diffusion area.

- C<sub>jsw</sub>: Junction side-wall capacitance constant in F/m.

Robert Dick Digital Integrated Cir

- P: Perimeter for three non-channel sides.

- $L_S$ : Length of diffusion region.

- W: Width of diffusion region (and transistor).

| Inverter switch model<br>Inverter transfer curves and parameter optimization<br>Homework |  |

|------------------------------------------------------------------------------------------|--|

| Junction capacitance                                                                     |  |

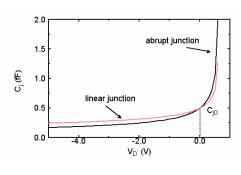

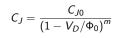

- $C_{jsw}$  is actually the diode capacitance we considered before.

- What happens as reverse bias increases?

- Can use worst-case approximation.

## Inverter switch m

# Capacitance linearization I

- Can approximate variable capacitance as fixed capacitance.

- Uses fitting.

$$egin{aligned} \mathcal{L}_{eq} &= rac{\Delta Q_j}{\Delta V_D} \ \mathcal{L}_{eq} &= rac{Q_j\left(V_{high}

ight) - Q_j\left(V_{low}

ight)}{V_{high} - V_{low}} \ \mathcal{L}_{eq} &= \mathcal{K}_{eq} \mathcal{L}_{j0} \end{aligned}$$

$$K_{eq} = \frac{-\phi_0^m}{(V_{high} - V_{low})(1-m)} \left( (\phi_0 - V_{high})^{1-m} - (\phi_0 - V_{low})^{1-m} \right)$$

# Inverter transfer curves and parameter optimization Inverter transfer curves and parameter optimization Homework

- $C_{i0}$ : Capacitance when voltage bias of diode is 0 V.

- *m*: Grading coefficient used to model effects of sharp (0.5) or linear (0.33) junction transition (see Page 82 in textbook).

- φ<sub>0</sub> = φ<sub>T</sub> ln (<u>N<sub>A</sub>N<sub>D</sub></u>): Built-in potential, i.e., voltage across junction due to diffusion at drift−diffusion equalibrium.

#### Inverter switch model Inverter transfer curves and parameter optimization

Capacitance parameters for default 0.25 µm process technology

|      |      | _               |                  |                  |                  |

|------|------|-----------------|------------------|------------------|------------------|

|      | (    | C <sub>OX</sub> | Co               | C                | -<br>·j          |

|      | (fF  | $/\mu m^2)$     | $(fF/\mu m)$     | (fF/µ            | um²)             |

| NMOS | 5    | 6               | 0.31             | 2                | 2                |

| PMOS | ,    | 6               | 0.27             | 1.               | 9                |

|      |      |                 |                  |                  |                  |

|      | mj   | $\phi_{b}$      | C <sub>jsw</sub> | m <sub>jsw</sub> | $\phi_{\it bsw}$ |

|      |      | (V)             | (fF/µm)          |                  | (V)              |

| NMOS | 0.5  | 0.9             | 0.28             | 0.44             | 0.9              |

| PMOS | 0.48 | 0.9             | 0.22             | 0.32             | 09               |

Properties of bottom and sidewall.

| Transistor dynamic behavior<br>Inverter switch model<br>Inverter transfer curves and parameter optimization<br>Homework | Transistor dynamic behavior<br>Inverter switch model<br>Inverter transfer curves and parameter optimization<br>Homework |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Upcoming topics                                                                                                         | Review                                                                                                                  |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         | a What are the first most important to model approxitement for                                                          |

| <ul> <li>MOSFET dynamic behavior.</li> </ul>                                                                            | <ul> <li>What are the five most important to model capacitances for<br/>MOSFETs?</li> </ul>                             |

| • Wires.                                                                                                                | • Explain their locations/sources.                                                                                      |

| • CMOS inverters.                                                                                                       | • How do they depend on operating region?                                                                               |

|                                                                                                                         | • How are drain and source capacitances calculated?                                                                     |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         |                                                                                                                         |

|                                                                                                                         |                                                                                                                         |

# Review: diode capacitance

Robert Dick

Digital Integrated Circuits

m = 0.5 for abrupt junctions, m = 0.33 for linear junctions

# A change to gate insulation

Robert Dick

Digital Integrated Circui

- Mark T. Bohr, Robert S. Chau, Tahir Ghani, and Kaizad Mistry.

- The High-k Solution. *IEEE Spectrum*, October 2007.

- What was the problem?

- What was its cause?

- What was the solution?

- Key concepts: gate leakage, tunneling, high- $\kappa$  dielectric, charge traps, single atomic layer deposition, and threshold voltage control.

Robert Dick Digital Integr

#### Transistor dynamic behavior Inverter switch model Inverter transfer curves and parameter optimization Homework

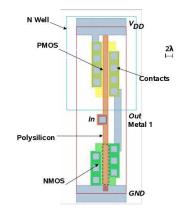

# Inverter layout

#### I ransistor dynamic behavior Inverter switch model Inverter transfer curves and parameter optimization

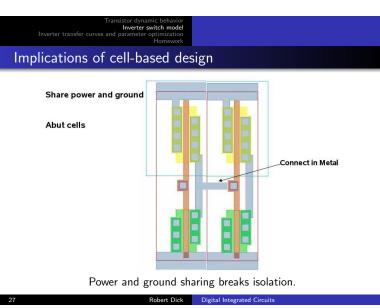

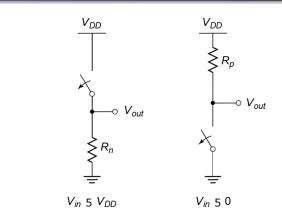

# Simplest switch model of inverter

| Transistor dynamic behavior<br>Inverter switch model<br>Inverter transfer curves and parameter optimization<br>Homework    |                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

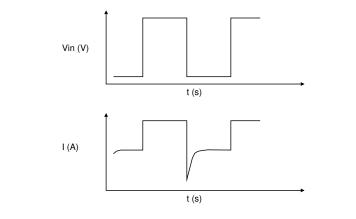

| Switch model transient beha                                                                                                | vior                                                                                                                  |

| $ \begin{array}{c} V_{DD} \\ R_{p} \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                        | $ \begin{array}{c} V_{DD} \\ \hline \\ R_n \\ \hline \\ \\ \hline \\ \\ V_{in} 5 V_{DD} \end{array}^{\circ V_{out}} $ |

| <ul> <li>Repeatedly charging/dischargi</li> <li>t<sub>pHL</sub> = f(R<sub>on</sub>C<sub>L</sub>).</li> <li>Why?</li> </ul> | ng load C.                                                                                                            |

Digital Integr

Robert Dick

| Transistor dynamic behavior                         |  |

|-----------------------------------------------------|--|

| Inverter switch model                               |  |

| Inverter transfer curves and parameter optimization |  |

|                                                     |  |

# Inverter switch model $t_{pHL}$ derivation

Both  $t_{pHL}$  and  $t_{pLH}$  defined as time from  $0.5 V_{DD}$  input crossing to  $0.5 V_{DD}$  output crossing. Assume step function on input.  $V_{C} = V_{DD} e^{-t/RC}$  (1)

Robert Dick

Solve for

$$V_C = V_{DD}/2$$

.

rt Dick Digital Integ

$V_{DD}/2 = V_{DD} e^{-t/RC}$ <sup>(2)</sup>

Digital Integ

$1/2 = e^{-t/RC}$  (3)

$\ln (1/2) = -t/RC$ (4)  $t = -RC \cdot -0.69$ (5)

$$t = -RC + -0.09$$

(3)

$t = 0.69RC = 0.69\tau$  (6)

Inverter transfer curves and parameter optimization

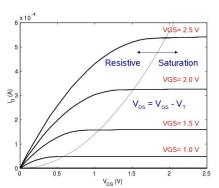

# NMOSFET I–V characteristics

Review: Is this a velocity-saturated short-channel device? How can you tell?

# Inverter switch model Inverter transfer curves and parameter optimization Homework

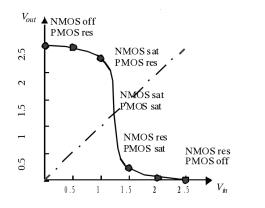

# Inverter load characteristics

# CMOS inverter transfer curve

Inverter transfer curves and paran

Robert Dick Digital Integrated Cir

## Inverter transfer curves and parameter optimization Homework Switching threshold derivation I

Find voltage for which  $V_{in} = V_{out}$ . Known: Both NMOSFET and PMOSFET saturated at this point. Recall that

$$I_{DSAT} = \mu C_{ox} \frac{W}{L} \left( (V_{GS} - V_T) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$$

(1)

Robert Dick Digital Integrated Circuit

## Inverter transfer curves and parameter optimization Homework Switching threshold derivation II

Working to find  $V_M$ . Find  $V_{GS}$  at which NMOSFET and PMOSFET  $I_D$  values equal.

Robert Dick

$$= kV_{DSAT} \left( V_{GS} - V_T \right) - \frac{V_{DSAT}}{2}$$

(2)

$$0 = k_n V_{DSATn} \left( V_M - V_{Tn} - \frac{V_{DSATn}}{2} \right) + k_p V_{DSATp} \left( V_M - V_{Tp} - \frac{V_{DSATp}}{2} \right)$$

(3)

Digital In

#### Inverter switch model Inverter transfer curves and parameter optimization

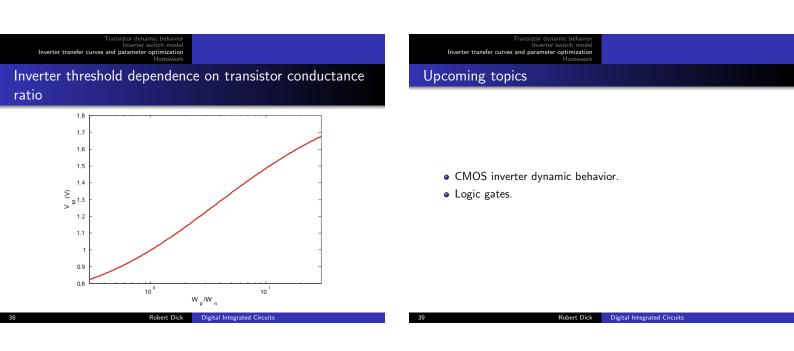

# Switching threshold derivation III

Solve for  $V_M$ .

$$V_{M} = \frac{\left(V_{T_{n}} + \frac{V_{DSAT_{n}}}{2}\right) + r\left(V_{DD} + V_{T_{p}} + \frac{V_{DSAT_{p}}}{2}\right)}{1 + r}.$$

(4)

$$=\frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}}=\frac{\nu_{satp}W_{p}}{\nu_{satn}W_{n}}$$

(5)

$$\nu = \frac{\mu\xi}{1 + \xi/\xi_c} \tag{6}$$

- $\nu$ : Charge carrier speed.

- $\xi$ : Field strength.

r

•  $\xi_c$ : Field strength at which scattering limits further increase in carrier speed.

Robert Dick Digital Integrated O

# Homework assignment

• 1 October: Read sections 3.3.3, 5.1, 5.2, 1.3.2, and 1.3.3 in

J. Rabaey, A. Chandrakasan, and B. Nikolic. *Digital Integrated Circuits: A Design Perspective*. Prentice-Hall, second edition, 2003. Read as much as you can by 27 September.

- 26 October: Extended Homework 1 due date due to difficulty getting help during office hours.

- 3 October: Lab 2.

41

Robert Dick Digital Integrated Circuits