## Digital Integrated Circuits - EECS 312

http://robertdick.org/eecs312/

Teacher: Robert Dick Office: 2417-E EECS dickrp@umich.edu Email: Phone:

Cellphone:

Email: 734-763-3329 847-530-1824

GSI: Shengshou Lu Office: 2725 BBB luss@umich.edu

#### Process variation

Given our current knowledge of transistor operation, what impact will variation in

- dopant concentrations,

- oxide thickness,

- transistor width, and

- interconnect width

have?

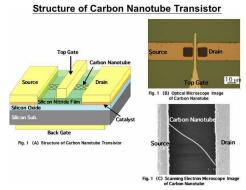

# Carbon nanotubes and nanowires

From AIST.

Robert Dick Digital Integrated Circuits

Layout Packaging and board

#### Review

- Explain each transistor operating region.

- What is pinch-off?

- Mow does body bias work?

- What is velocity saturation?

- What is sub-threshold operation?

#### **FinFETs**

From Freescale.

Robert Dick Digital Integrated Circu

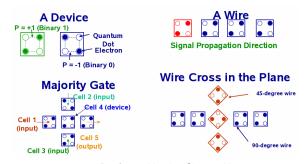

#### Quantum cellular automata

- Binary information encoded in device configuration.

- Signals are propagated through nearest neighbor interaction.

From Professor Xiaobo Sharon Hu.

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

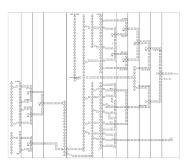

# Quantum cellular automata arithmetic-logic unit

From Professor Xiaobo Sharon Hu.

Robert Dick

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

ging and board-level integration

#### Common problems

- Difficult to get high-quality devices where they are needed.

- High susceptibility to thermal noise.

- High susceptibility to charge trap offsets.

- Low gain.

Robert Di

Digital Integrated Circuits

Device trends Fabrication Layout and design rules Packaging and board-level integration

#### Review

- List a few different alternatives to CMOS for use in digital systems.

- Indicate their advantages and disadvantages relative to CMOS.

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

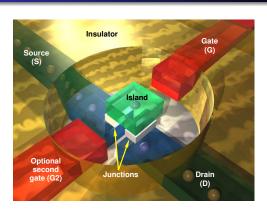

## Single-electron tunneling transistors

Robert Dick

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

#### What does the future hold

- CMOS for another decade or so, until devices consist of a small integer number of atoms.

- Nobody knows what comes next.

- Nothing? New device technology?

- Implications for information technology?

Robert

Digital Integrated Circuits

Fal Layout and des Packaging and board-level int Ho

## NMOSFET

Robert Dick

Digital Integrated Circuits

Robert Die

Digital Integrated Circuits

# Insulator properties

- $\bullet$  Low- $\kappa:$  reduced capacitance, useful for isolating wires.

- High- $\kappa$ : increased capacitance, useful for maintaining k despite increased gate thickness.

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

#### High-level fabrication process overview

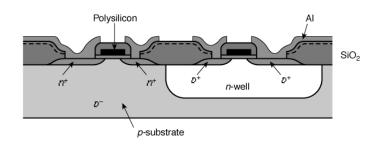

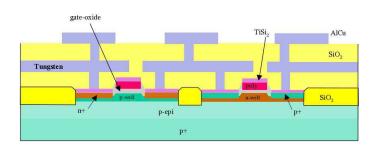

**Dual-Well Trench-Isolated CMOS Process**

Robert Dick

Digital Integrated Circuits

16

Digital Integrated Circuit

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

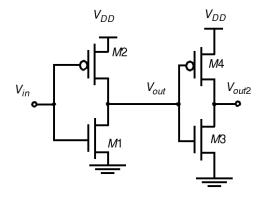

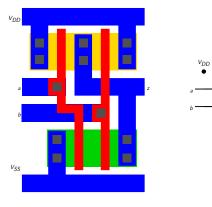

#### Schematic of circuit to fabricate

Robert Dick

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

## Layout of circuit to fabricate

Robert Dick

Digital Integrated Circuits

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

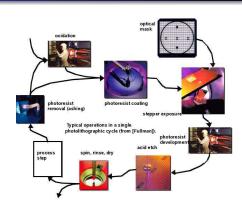

# Overview of fabrication process

#### Fabrication process details

From Richard C. Jaeger. *Introduction to Microelectronic Fabrication*. Addison-Wesley, 1993.

Device trends

Fabrication

Packaging and board-level integration

Homework

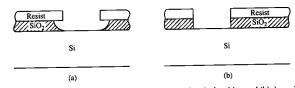

SiO<sub>2</sub> patterning

Chemical or plasma etch

(a) Silicon base material

(b) After oxidation and deposition of negative photoresist

(b) After oxidation and deposition of negative photoresist

(c) Stepper exposure

(c) Stepper exposure

Device trends

Fabrication

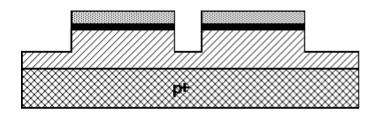

Paterned

Optical mask

(d) After development and etching of resist, chemical or plasma etch of SiO<sub>2</sub>

(e) After etching

Optical mask

(f) Final result after removal of resist

(f) Final result after removal of resist

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

# Summary of processing steps

- Define active areas.

- 2 Etch and fill trenches.

- Implant well regions.

- Deposit and pattern polysilicon/metal gate layer.

- Implant source and drain regions, and substrate contacts.

- Oreate contacts and via windows.

- Deposit and pattern metal layers.

Robert Dick Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

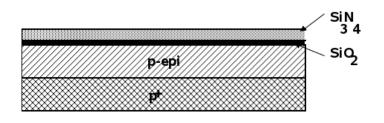

Step 2: gate oxide and sacrificial nitride layer deposition

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

#### **Etching**

Fig. 2.5 Etching profiles obtained with (a) isotropic wet chemical etching and (b) dry anisotropic etching in a plasma or reactive-ion etching system.

From Richard C. Jaeger. *Introduction to Microelectronic Fabrication*. Addison-Wesley, 1993.

22 Robert Dick Digital Integrated Circuits

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

## Step 1: epitaxial layer

24 Robert Dick Digital Integrated Circuits

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

Step 3: plasma etching

25 Robert Dick Digital Integrated Circuits 26

Robert Dick

igital Integrated Circuits

Device trends

Layout and delegy rules

Packaging and board-fore Dick

Step 4: trench filling, CMP, etching, SiO<sub>2</sub> deposition

SiO<sub>2</sub>

SiO<sub>2</sub>

Therefore Trends

Fabrication

Layout and delegy rules

Packaging and board-fore of Education

Step 6: p-well and V<sub>Tp</sub> adjustment implants

Step 5: n-well and  $V_{Tn}$  adjustment implants

28 Robert Dick Digital Integrated Circuits

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

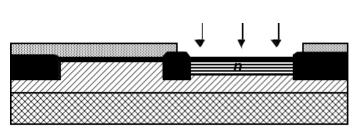

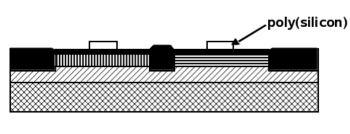

Step 7: polysilicon/metal deposition and etch

30 Robert Dick Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

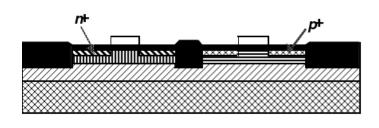

Step 8: n<sup>+</sup> and p<sup>+</sup> source, drain, and poly implantation

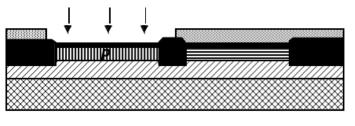

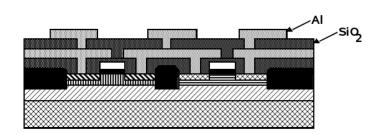

Step 9: SiO<sub>2</sub> deposition and contact etch

siq

1 Robert Dick Digital Integrated Circuits 32 Robert Dick Digital Integrated Circuits

Step 10: deposit and pattern first interconnect layer

Step 11: deposit SiO<sub>2</sub>, etch contacts, deposit and pattern second interconnect layer

## Interconnect layers

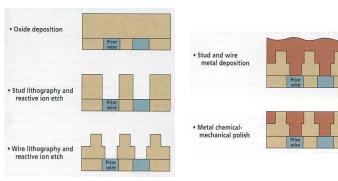

Al vs. Cu

- For Al, can deposit and etch metal layers.

- Cu alloys with Si.

- Cannot safely deposit Cu directly on Si.

- Cu difficult to controllably etch.

- Instead, build SiO<sub>2</sub> shield and etch contact regions.

## Damascene process

From IBM.

## Interconnect layers

Robert Dick Digital Integrated Ci

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

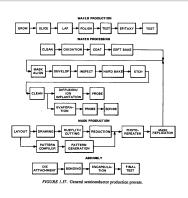

### Layout production

- Must define 2-D structure for each mask/layer.

- Initial topology planning often done.

- Can be partially or fully automated.

- Must adhere to design rules.

Robert

Digital Integrated Circuits

V<sub>DD</sub> 3

In Out

Stick diagram of inverter

Stick diagrams

Robert Dick

**GND**

Digital Integrated Circuits

Device trends

Pabrication

Layout and design rules

Packaging and board-level integration

Homework

#### Faults and variation

- Clearly cannot have two wires crossing each other.

- Variation imposes further constraints.

Robert Dick

Digital Integrated Circuits

Device trends Fabrication **Layout and design rules** Packaging and board-level integration Homework

#### Possible faults

Robert Dic

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

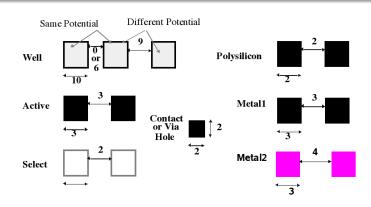

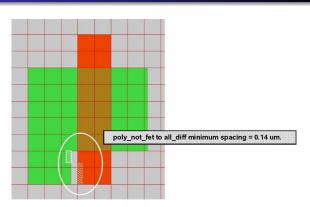

#### Design rules

#### Summary

- Automatically-checked layout rules.

- Reduce fault probabilities.

- Generally regarded as necessary.

#### Caveats

- Recent studies show many rules are not beneficial.

- ullet Interaction range is increasing relative to  $\lambda.$

- Complicates design rules, making manual comprehension difficult.

- Design rule checking can be slow.

Device trends Fabrication Layout and design rules Packaging and board-level integration Homework

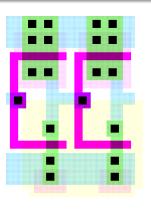

# Meanings of colors in layouts

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | £              |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

|                      |         |                |

Robert

Digital Integrated Circuit

Robert Dick

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

## Layout layers

Robert D

Digital Integrated Circuits

Fabricati Layout and design rul Packaging and board-level integratic Homewo

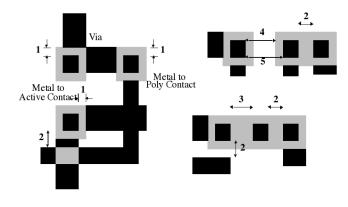

## Intra-layer design rules

Rober

Digital Integrated Circuits

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

## Via design rules

Robert Dick

Digital Integrated Circuits

Device trends Fabrication **Layout and design rules** Packaging and board-level integration Homework

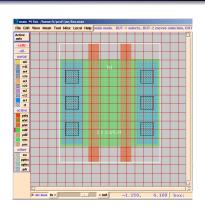

#### Layout editor

Ro

Digital Integrated Circuits

Device trends Fabrication **Layout and design rules** Packaging and board-level integration Homework

# Design rule checker

Packaging and board-level integrat

Homew

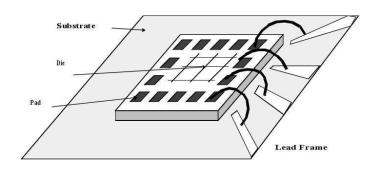

# Packaging requirements

- Electrical: Good insulators and conductors.

- Mechanical: Reliable, doesn't stress IC.

- Thermal: Low thermal resistance to ambient. In some cases, consistency more important.

- Cost.

50 Robert Dick Digital Integrated Circuits 52 Robert Dick Digital Integrated Circuits

Layout and design rules

Packaging and board-level integration

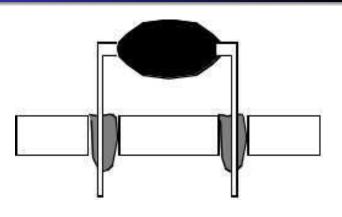

# Wire bonding

Layout and design rule Packaging and board-level integration

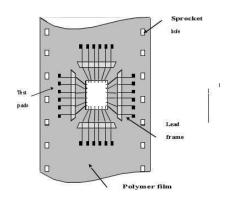

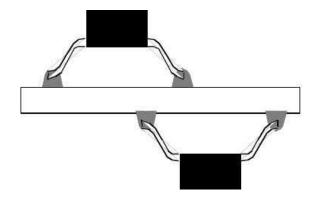

## Tape automated bonding

Layout and design rules Packaging and board-level integration

# Tape automated bonding die attachment

Substrate

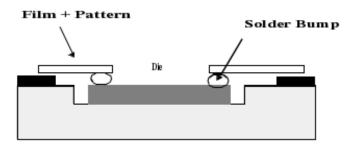

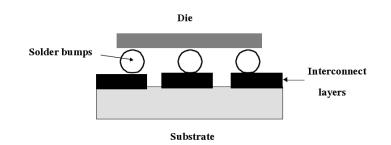

# Flip-chip bonding

Layout and design rules Packaging and board-level integration

# Through-hole PCB mounting

Layout and desig Packaging and board-level inte

# Surface mount

Layout and design rules Packaging and board-level integration

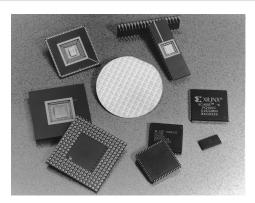

#### Example package types

Layout and design Packaging and board-level integral

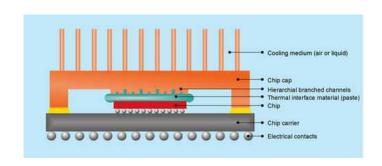

### Chip cap

Layout and design rules Packaging and board-level integration

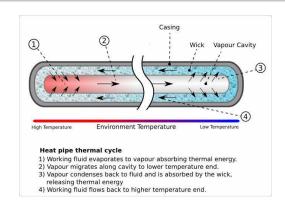

## Heat pipe

Layout and design rul Packaging and board-level integration

## Heat pipe details

Layout and design rules Packaging and board-level integration

## Example of variation in package parameters

| Type               | C (pF) | L (nH) |

|--------------------|--------|--------|

| 68-pin plastic DIP | 4      | 35     |

| 68-pin ceramic DIP | 7      | 20     |

| 256-pin PGA        | 5      | 15     |

| Wire bond          | 1      | 1      |

| Solder bump        | 0.5    | 0.1    |

Layout and design ru Packaging and board-level integrat

## System-on-chip

- Instead of integrating more ICs, put more on an IC.

- Advantages: Lower cost per device, compact.

- Disadvantages: Requires integration of devices fabricated with different processes.

#### Move from lead solder

- Tin-lead solder was commonly used.

- Lead is toxic, accumulates in the body, and is difficult to dispose

of.

- Pure tin works in the short term.

- May be acceptable as solder in the long term.

- Problems with plating.

Digital Integrated Circuits

Device trends Fabrication Layout and design rules kaging and board-level integration

#### Multi-chip modules

- Better *C* than board-level integration.

- Integrate multiple processes.

- Somewhat compact.

- Expensive.

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

#### Tin whiskers

Figure 1-1 – Tin plated connector pins after 10 years (courtesy of NASA GSFC)

Screw dislocations, primarily caused by plating.

Robert D

Robert Dick Digital Integrated Circuits

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

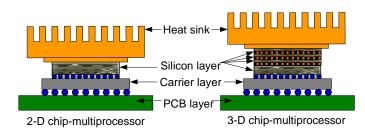

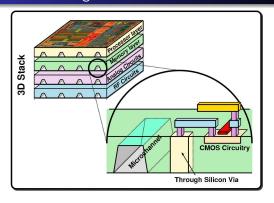

# Multiple active layer 3-D integration

Potential for thermal problems.

Robert Dick

Digital Integrated Circuits

Robert Dick

Digital Integrated Circuits

Device trends Fabrication Layout and design rules Packaging and board-level integration

# Heterogeneous system 3-D integration

#### Integrate

- Logic.

- Memory.

- Analog.

- Research on discrete components (with soldering).

Fabrication Layout and design rules Packaging and board-level integration Homework

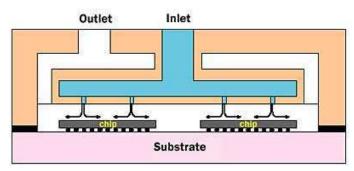

# Microchannel cooling

Credit to David Atienza at EPFL.

Re

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

## Vapor-phase cooling

Credit to Michael J. Ellsworth, Jr. and Robert E. Simons at IBM.

71

Robert Dick

Digital Integrated Circuit

Device trends

Fabrication

Layout and design rules

ackaging and board-level integration

Homework

## **Upcoming topics**

- MOSFET dynamic behavior.

- Wires.

- CMOS inverters.

Device trends

Fabrication

Layout and design rules

Packaging and board-level integration

Homework

## Summary

- CMOS is the most economical way to build digital logic now, but potential alternatives being developed.

- Fabrication process is essentially repeated deposition, masking, etching, and polishing steps to dope and build material layers.

- $\bullet \ \, AI{\rightarrow} Cu.$

- ${\sf SiO}_2 o {\sf High-}\kappa$  and  ${\sf Low-}\kappa.$

- Cu interconnects use damascene process.

- $\bullet \ \, \mathsf{Poly}\text{-}\mathsf{Si} {\to} \mathsf{metal}.$

72

Robert Dick

gital Integrated Circuits

Pabrication

Layout and design rule

Packaging and board-level integration

Homewor

## Homework assignment

24 September: Read Mark T. Bohr, Robert S. Chau, Tahir Ghani, and Kaizad Mistry. The High-k Solution. IEEE Spectrum, October 2007.

• 24 September: Homework 1.

• 3 October: Lab 2.

Robert

Digital Integrated Circuits

Robert Dick

Digital Integrated Circuit