#### EECS 312 Discussion 3

09/20

Shengshuo Lu

(luss@umich.edu)

#### Overview

Reminder

- HW 1: Due Sep 24

• Diode

Transistors

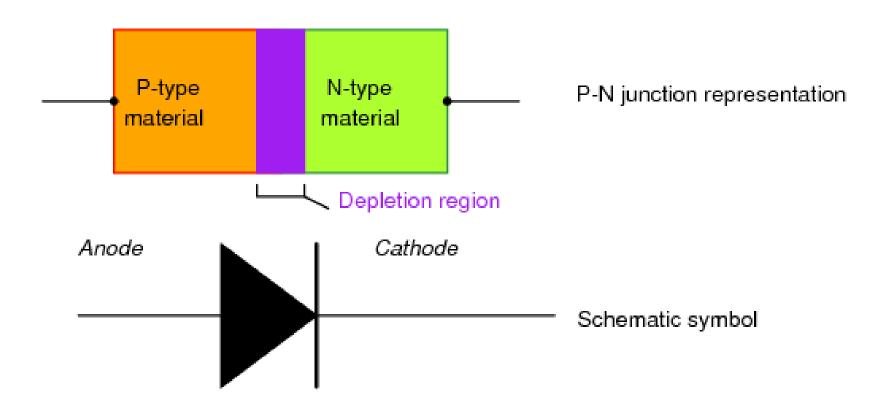

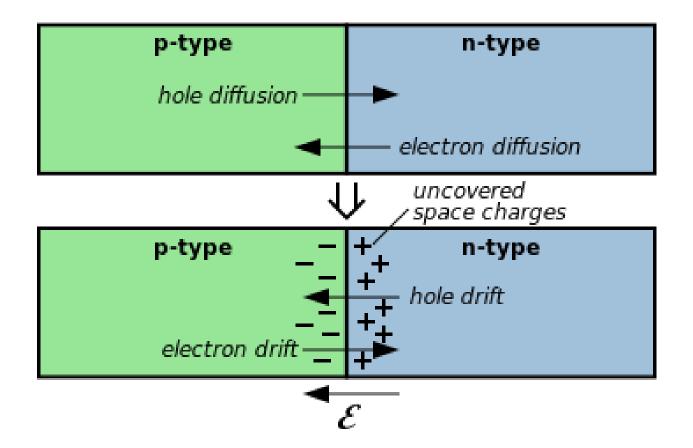

#### Diode

#### Diode

#### Diode

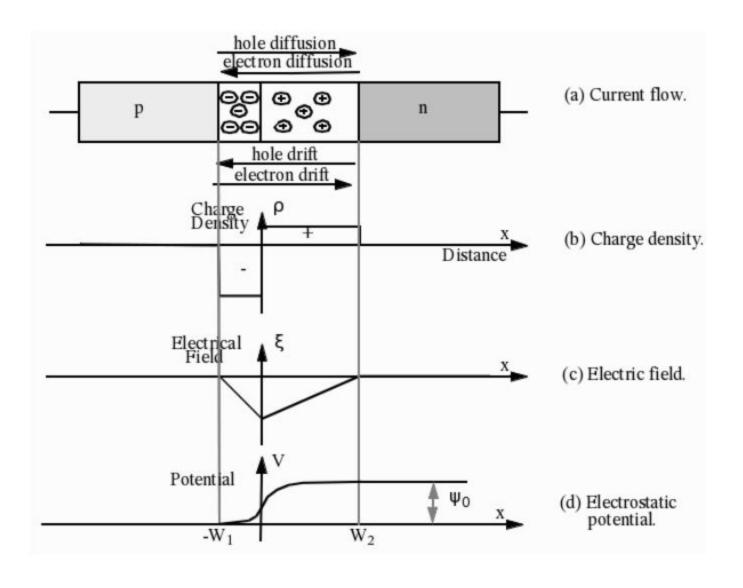

# Built-in Potential Depletion Region Width

$$\Phi_{0} = \Phi_{T} \ln \left[ \frac{N_{A} N_{D}}{n_{i}^{2}} \right]$$

$$\Phi_{T} = \frac{kT}{q}$$

$$W \approx \left[ \frac{2\epsilon_{r} \epsilon_{0}}{q} \left( \frac{N_{A} + N_{D}}{N_{A} N_{D}} \right) \Phi_{0} \right]^{\frac{1}{2}}$$

- n<sub>i</sub>: intrinsic charge carrier concentration.

- N<sub>x</sub>: acceptor and donor concentrations.

- k: Boltzmann constant

- T: temperature

- q: elementary charge

#### **Diode Current**

$$I_D = I_S \left( e^{\frac{V_D}{\phi_T}} - 1 \right)$$

- I<sub>D</sub>: diode current

- $V_D$ : diode voltage

- I<sub>S</sub>: saturation current constant

- $\phi_T = \frac{kT}{q}$ : thermal voltage

- k: Boltzmann constant

- T: temperature

- q: elementary charge

### Diffusion capacitance

$$C_{J0} = A_D \sqrt{\frac{\epsilon_{Si} q}{2} \frac{N_A N_D}{N_A + N_D} \frac{1}{\phi_0}}$$

- A<sub>D</sub>: area of diode

- $\epsilon_{Si}$ : permittivity of silicon

- N<sub>X</sub>: carrier density

- $\phi_0 = \phi_T \ln \frac{N_A N_D}{n^2}$

- $\phi_T = \frac{kT}{q}$   $n_i$ : intrinsic carrier concentration

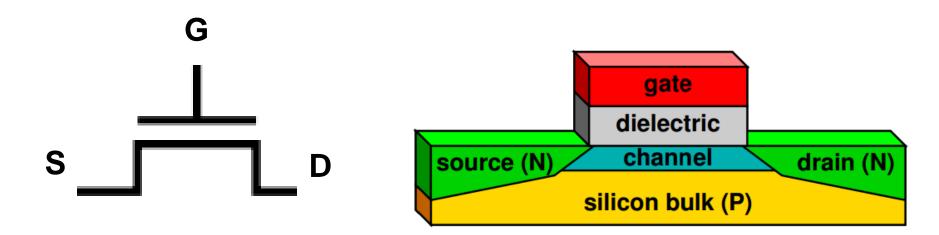

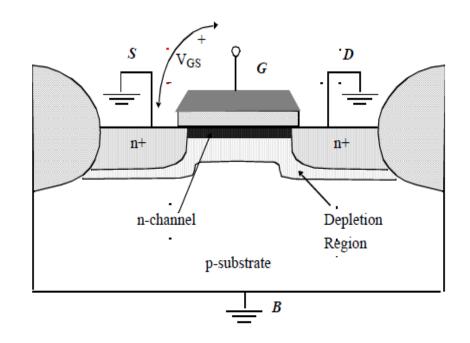

#### **NMOS**

#### Threshold Voltage

- $0 < V_{GS} < V_{T}$

- Repel mobile holes and accumulation of electron beneath the gate oxide

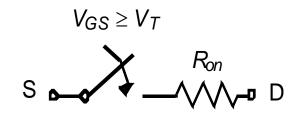

- $V_{GS} > V_{T}$

- Surface is as strongly n-type as the substrate is p-type

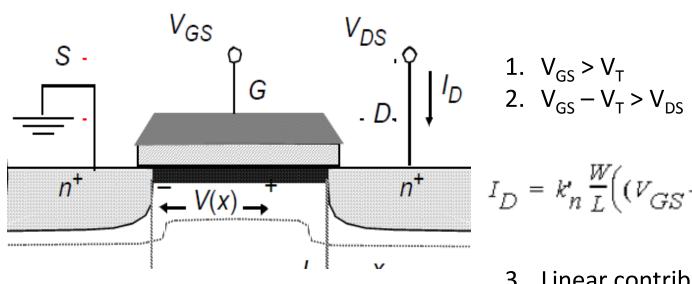

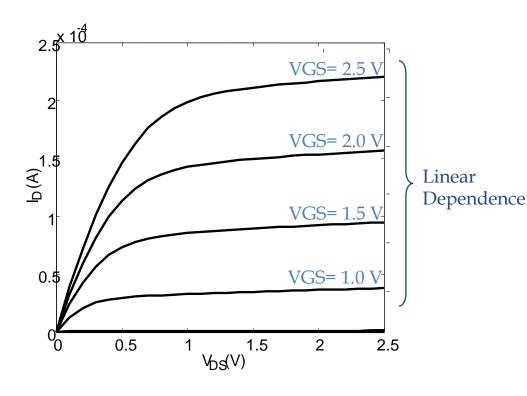

## Operation Regions – Linear (lab 2)

1.

$$V_{GS} > V_{T}$$

2.

$$V_{GS} - V_{T} > V_{DS}$$

$$I_D = k_n \frac{W}{L} \Big( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \Big)$$

3. Linear contribution of  $V_{GT}$  to  $I_{D}$

4.

$$k_n = \mu_n C_{ox}$$

In case of a P-type MOSFET, the inequalities used above should be directed opposite

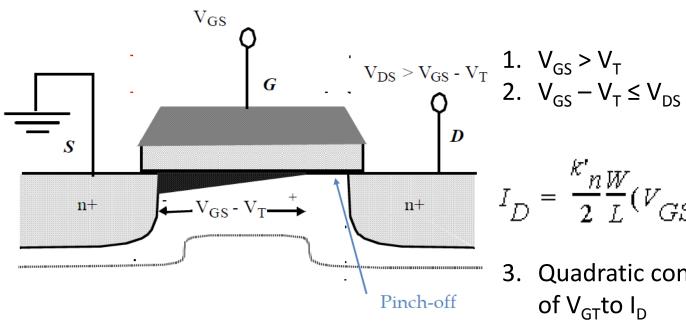

## Operation Regions – Saturation (lab 2)

$$I_D = \frac{k'_n \underline{W}}{2} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

- 3. Quadratic contribution of  $V_{GT}$ to  $I_D$

- λ channel-length modulation parameter

In case of a P-type MOSFET, the inequalities used above should be directed opposite

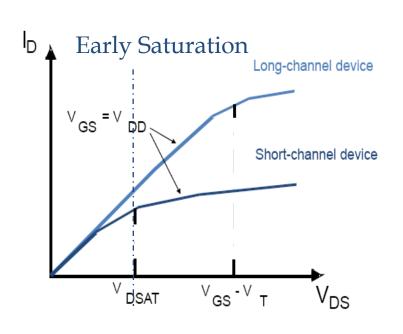

#### Operation Regions – Velocity Saturated

#### **Short Channel Effects**

Strong electric field causes carrier mobility degradation : Compared to feature scaling, voltage scaling is lagging behind

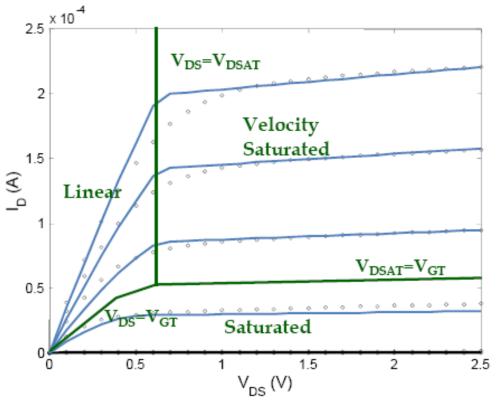

#### A unified model

$$\begin{split} I_D &= 0 \ \text{ for } \ V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \Big( V_{GT} V_{min} - \frac{V_{min}^2}{2} \Big) (1 + \lambda V_{DS}) \ \text{for } V_{GT} \geq 0 \\ \text{with } \ V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}), \\ V_{GT} &= V_{GS} - V_T, \\ \text{and } \ V_T &= V_{T0} + \gamma (\sqrt{|-2\phi_F|} + V_{SB}| - \sqrt{|-2\phi_F|}) \end{split}$$

- If V<sub>DS</sub> is minimum:

Linear region

- 2. If V<sub>GT</sub> is minimum: **Saturation Region**

- 3. If V<sub>DSAT</sub> is minimum : **Velocity saturated region**