#### Advanced Digital Logic Design - EECS 303

http://ziyang.eecs.northwestern.edu/eecs303/

Teacher: Robert Dick Office:

L477 Tech dickrp@northwestern.edu Email: Phone: 847-467-2298

#### Introduction to testing

- Determining the best way to test large circuits requires automation

- Building large circuits that are easy to test also requires automation

- Testing it spans all design, from system to physical level

- Today, I'll introduce some classical ideas at the logic level

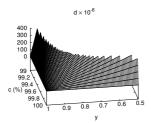

Defect level

- $\bullet$  Example acceptable defect level:  $\sim 0.0002$

- Either yield must be very high or fault coverage must be very high

#### Functional testing

- No assumptions about types of fault

- No assumptions about structure or properties of Circuit Under Test (CUT)

- $\bullet\,$  The CUT is a black box that is checked to determine whether it responds to all (or most) input (sequences) as specified

- However, ignoring structural information makes testing unnecessarily slow

#### Introduction to testing

- After fabrication, some circuits don't work correctly

- Determining which circuits contain faults requires testing

- Testing some types of circuits is easy, testing others is difficult

- One can use automation to help solve this problem

Yield

- Yield, y, is the fraction of fault-free products

- Test fault coverage, c, is the fraction of faults that the set of applied tests detects

- · Low-yield is expensive because fabrication capacity is wasted

- Defect level, d, is the fraction of parts containing undetected faults

- $d = 1 y^{1-c}$

- · A high defect level is extremely expensive because it means circuits make their way into products, or worse, to consumers, before faults are discovered

Faults and failures

- A fault is a physical defect in a circuit

- A failure is the deviation of a circuit from its specified behavior

- Faults can cause failures but they don't always cause failures

Structural testing

- Use information about the specific CUT

- Types of faults that are likely to occur

- Structure of circuit

Combinational testing

Sequential testing

Single stuck-at faults

Advanced digital copic design

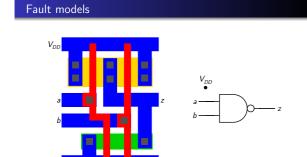

Fault models

Combinational test generation

Consider a NAND3 gate

| Inputs |    | fault |   |      |   | 2 | Z |   |   |   |   |          |

|--------|----|-------|---|------|---|---|---|---|---|---|---|----------|

|        | Α" | В     | C | free | a | 3 | ŀ | ) | ( | 2 | 7 | <u>.</u> |

|        | А  | D     | C | iree | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1        |

| -      | 0  | 0     | 0 | 1    | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1        |

|        | 0  | 0     | 1 | 1    | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1        |

|        | 0  | 1     | 0 | 1    | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1        |

|        | 0  | 1     | 1 | 1    | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1        |

|        | 1  | 0     | 0 | 1    | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1        |

|        | 1  | 0     | 1 | 1    | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1        |

|        | 1  | 1     | 0 | 1    | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1        |

|        | 1  | 1     | 1 | 0    | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1        |

Too expensive to use  $2^n$  inputs ( $2^3 = 8$  in this case) Unate covering again

Combinational testing

Sequential testing

Fault equivalence

Advanced Digital Logic Design

Yield

Fault models

Combinational test generation

- The function of the circuit is identical in the presence of either fault

- $\bullet$  E.g., any input of a NAND gate being s-a-0 or the output being s-a-1  $\rightarrow$  output of 1

- In general, identifying equivalent faults, or fault collapsing is difficult

- However, can use knowledge about gates, and connectivities, to find most equivalent faults

16 Robert Dick Advanced Digital Logic Design

Combinational testing Sequential testing Sequential testing Other fault models

Other fault models

- $\bullet~\sim 2/3$  CMOS faults are not stuck-at faults

- Luckily, stuck-at fault tests often detect them

- More advanced faults models

- Allow higher theoretical coverage

- Are more complicated

- In this lecture, we only have time to cover stuck-at-faults

Combinational testing Sequential testing Sequential testing Fault models Combinational test generation

- One of the simplest and most common fault models

- S-a-0: Stuck-at 0

- S-a-1: Stuck-at 1

- Relies on digital reinforcement

- ullet 0.8  $\cdot$   $V_{DD}$  is 1  $\cdot$   $V_{DD}$  one logic stage later

- $\bullet \ \, \text{S-a-0.8} \approx \text{s-a-1}$

- For two-level logic, exhaustive test set for single stuck-at faults will detect all multiple stuck-at faults, too

- Doesn't hold for multi-level logic

- A test of all possible inputs for a NANDn gate will require 2<sup>n</sup> tests

- Applying all possible tests (or sequences of tests) for complex circuits isn't practical

- However, for all NANDn gates, all single stuck-at faults (and implicitly multiple stuck-at faults) can be tested using only n+1

## Consider a NAND3 gate

| Inputs fault |     |   |    |      |   | 2    | z   |     |   |   |     |   |

|--------------|-----|---|----|------|---|------|-----|-----|---|---|-----|---|

|              | Α'' | D | ٠, | free | á | а    | ŀ   | )   |   | 2 | - 2 | Z |

|              | А   | D | C  | iree | 0 | 1    | 0   | 1   | 0 | 1 | 0   | 1 |

|              | 0   | 0 | 0  | 1    | 1 | 1    | 1   | 1   | 1 | 1 | 0   | 1 |

|              | 0   | 0 | 1  | 1    | 1 | 1    | 1   | 1   | 1 | 1 | 0   | 1 |

|              | 0   | 1 | 0  | 1    | 1 | 1    | 1   | 1   | 1 | 1 | 0   | 1 |

|              | 0   | 1 | 1  | 1    | 1 | 0    | 1   | 1   | 1 | 1 | 0   | 1 |

|              | 1   | 0 | 0  | 1    | 1 | 1    | 1   | 1   | 1 | 1 | 0   | 1 |

|              | 1   | 0 | 1  | 1    | 1 | 1    | 1   | 0   | 1 | 1 | 0   | 1 |

|              | 1   | 1 | 0  | 1    | 1 | 1    | 1   | 1   | 1 | 0 | 0   | 1 |

|              | 1   | 1 | 1  | 0    | 1 | 0    | 1   | 0   | 1 | 0 | 0   | 1 |

| Eqi          |     |   |    |      |   | lent | fau | lts |   |   |     |   |

| 17              | Robert Dick                                 | Advanced Digital Logic Design                          |

|-----------------|---------------------------------------------|--------------------------------------------------------|

|                 |                                             |                                                        |

|                 | Combinational testing<br>Sequential testing | Yield<br>Fault models<br>Combinational test generation |

| Test generation |                                             |                                                        |

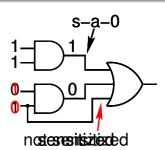

- Can use algorithms to automatically generate a test for a specific fault

- ullet Problem: Identify some test, t, such that the output of the circuit will deviate from its specified value if a particular fault, f, is present

- Excitation: Need to propagate a value to stuck-at fault that is contrary to the fault value

- $\bullet$  Sensitization: Need to propagate the faulty value to an output of the circuit

Robert Dick Advanced Digital Logic Design 20 Robert Dick Advanced Digital Logic Design

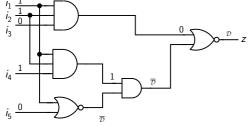

Excitation and sensitization

sexsitiztadion

Automatic Test Pattern Generation (ATPG)

- Can automatically determine test for a particular fault

- Boolean difference

- Generally considered too slow for use on large circuits

- Easy to understand

- ullet Excitation/sensitization based methods ( $\mathcal{D}$ -algorithm)

Boolean difference

- If the resulting function is 0, the fault can not be identified

- If the resulting function is 1, the fault can be identified

- $\bullet\,$  Use a test that satisfies (sets to 1) the function

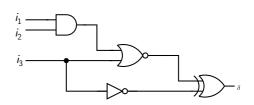

$\mathcal{D}$ -algorithm

- We have seen that, in order to test for a particular fault, we must

- Excite the fault

- Sensitize a path from the fault to the output

- $\bullet$  The  $\mathcal{D}\text{-algorithm}$  is an automated method of finding a test that excites a fault and sensitizes a path to the circuit output

- J.P. Roth, IBM, 1966

Backtracking

Boolean difference

In the presence of the fault, function is  $\overline{\emph{i}_{3}}$ XOR faulty and specified functions

Boolean difference

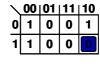

| \ | 00 | 01 | 11 | 10 |

|---|----|----|----|----|

| 0 | 0  | 0  | 0  | 0  |

| 1 | 0  | 0  | 0  | 1  |

| \ | 00 | 01 | 11 | 10 |

|---|----|----|----|----|

| 0 | 1  | 0  | 0  | 1  |

| 1 | 1  | 0  | 0  | 1  |

Roth's extension to Boolean algebra

- - $\alpha$  is the fault-free value  $\beta$  is the value in the presence of the fault

- 0/0 = 0

- 1/1 = 1

- $1/0 = \mathcal{D}$

- $\bullet \ 0/1 = \overline{\mathcal{D}}$

- X/X = X

Combinational testing

Yield Fault models

### (N)AND $\mathcal{D}$ -cubes of failure

|      | detection |     | $\mathcal{D}	ext{-cube}$ of failure |   |   |                          |

|------|-----------|-----|-------------------------------------|---|---|--------------------------|

| gate | ir        | put | z                                   |   |   |                          |

|      | a         | b   |                                     | а | b | z                        |

| AND  | 1         | 1   | s-a-0                               | 1 | 1 | $\mathcal{D}$            |

|      | 0         | Χ   | s-a-1                               | 0 | Χ | $\overline{\mathcal{D}}$ |

|      | Х         | 0   | s-a-1                               | Х | 0 | $\overline{\mathcal{D}}$ |

| NAND | 1         | 1   | s-a-1                               | 1 | 1 | $\overline{\mathcal{D}}$ |

|      | 0         | X   | s-a-0                               | 0 | X | $\mathcal{D}$            |

|      | X         | 0   | s-a-0                               | Х | 0 | $\mathcal{D}$            |

| 29 | Robert Dick | Advanced Digital Logic Design |

|----|-------------|-------------------------------|

|    |             |                               |

Sequential testing

Fault models Combinational test generation

# (N)AND $\mathcal{D}$ -cubes of propagation

| inp                      | out                      | AND                      | NAND                     |

|--------------------------|--------------------------|--------------------------|--------------------------|

| а                        | b                        | z                        | Z                        |

| 1                        | $\mathcal{D}$            | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| 1                        | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

| $\mathcal{D}$            | 1                        | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| $\overline{\mathcal{D}}$ | 1                        | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

| $\mathcal{D}$            | $\mathcal{D}$            | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

# 31 Robert Dick Advanced Digital Logic Design Combinational testing Sequential testing Se

#### $\mathcal{D}$ -algorithm

- ${\color{red} \bullet}$  Initially, all the lines in the circuit are X (Don't Care)

- Left blank in example

- ${\bf 0}$  A gate with an input of  ${\cal D}$  or  $\overline{\cal D}$  and an output of X belongs to the frontier

- An element whose assigned inputs do not imply the output is unjustified

- ${\color{red} \bullet}$  We want to drive the frontier to a circuit output (sensitize). . .

- 5 ... and justify the gate inputs (excite)

Robert Dick Advanced Digital Logic Design

#### $\mathcal{D}$ -algorithm

A test has been found

Select a *D*-cube of failure to excite the fault

while frontier has not yet reached an output do

Perform the implications of the most recent assignment

if the frontier is empty then

BACKTRACK

end if

Choose a signal, s, s.t. s can't reached from the fault

Assign s to a value in order to propagate the fault forward

end while

for each unjustified line, / do

if / can be justified then

Justify /

else

BACKTRACK

end if

Combinational testin Sequential testin

Fault models

Combinational test generation

### (N)OR $\mathcal{D}$ -cubes of failure

|   |      | dete | ection | $\mathcal{D}	ext{-cube}$ of failure |   |   |                          |  |

|---|------|------|--------|-------------------------------------|---|---|--------------------------|--|

|   | gate | in   | put    | z                                   |   |   |                          |  |

|   |      | а    | b      |                                     | a | b | z                        |  |

|   | OR   | 0    | 0      | s-a-1                               | 0 | 0 | $\overline{\mathcal{D}}$ |  |

|   |      | 1    | X      | s-a-0                               | 1 | X | $\mathcal{D}$            |  |

|   |      | Х    | 1      | s-a-0                               | Х | 1 | $\mathcal{D}$            |  |

| _ | NOR  | 0    | 0      | s-a-0                               | 0 | 0 | $\mathcal{D}$            |  |

|   |      | 1    | Χ      | s-a-1                               | 1 | X | $\overline{\mathcal{D}}$ |  |

|   |      | Х    | 1      | s-a-1                               | Х | 1 | $\overline{\mathcal{D}}$ |  |

Combinational testing Sequential testing Sequential testing (N)OR D-cubes of propagation

| in                       | out                      | OR                       | NOR                      |

|--------------------------|--------------------------|--------------------------|--------------------------|

| а                        | b                        | z                        | z                        |

| 0                        | $\mathcal{D}$            | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| 0                        | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

| $\mathcal{D}$            | 0                        | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| $\overline{\mathcal{D}}$ | 0                        | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

| $\mathcal{D}$            | $\mathcal{D}$            | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |

| $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |

Robert Dick Advanced Digital Logic Design

Combinational testing Sequential testing

Combinational test generation

$\mathcal{D}$ -algorithm notes

There are a few details not explained in the pseudocode

- $\bullet$  Signals should be selected in order to drive the frontier forward

- Backtracking is the action of backing up and taking the closest previously unexplored branch in the decision tree

AND  $\mathcal{D}$ -cubes of propagation

| inp                      | out                      | AND                      |

|--------------------------|--------------------------|--------------------------|

| а                        | b                        | z                        |

| 1                        | $\mathcal{D}$            | $\mathcal{D}$            |

| 1                        | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ |

| $\mathcal{D}$            | 1                        | $\mathcal{D}$            |

| $\overline{\mathcal{D}}$ | 1                        | $\overline{\mathcal{D}}$ |

| $\mathcal{D}$            | $\mathcal{D}$            | $\mathcal{D}$            |

| $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ |

NOR  $\mathcal{D}$ -cubes of failure

|      | detection $\mid \mathcal{D}$ -cube of failur |     |                |   | failure |                          |

|------|----------------------------------------------|-----|----------------|---|---------|--------------------------|

| gate | ir                                           | put | z              |   |         |                          |

|      | a                                            | b   |                | a | b       | z                        |

| NOR  | 0                                            | 0   | s-a-0          | 0 | 0       | $\mathcal{D}$            |

|      | 0                                            | 1   | s-a-0<br>s-a-1 | 0 | 1       | $\overline{\mathcal{D}}$ |

|      | 1                                            | 0   | s-a-1          | 1 | 0       | $\overline{\mathcal{D}}$ |

|      | 1                                            | 1   | s-a-1          | 1 | 1       | $\overline{D}$           |

Caveats

- This lecture has only introduced some topics in testing

- $\bullet\,$  If you intend to do research in this area, take a few courses on testing

- Single stuck-at fault model is becoming obsolete

NOR  $\mathcal{D}$ -cubes of failure

|      |       |   | $\mathcal{D}	ext{-cube}$ of failure |   |   |                          |

|------|-------|---|-------------------------------------|---|---|--------------------------|

| gate | input |   | Z                                   |   |   |                          |

|      | а     | b |                                     | а | b | z                        |

| NOR  | 0     | 0 | s-a-0                               | 0 | 0 | $\mathcal{D}$            |

|      | 0     | 1 | s-a-1                               | 0 | 1 | $\overline{\mathcal{D}}$ |

|      | 1     | 0 | s-a-1                               | 1 | 0 | $\overline{\mathcal{D}}$ |

|      | 1     | 1 | s-a-1                               | 1 | 1 | $\overline{\mathcal{D}}$ |

NOR  $\mathcal{D}$ -cubes of propagation

| inp                      | out                      | NOR                      |  |  |

|--------------------------|--------------------------|--------------------------|--|--|

| а                        | b                        | z                        |  |  |

| 0                        | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |  |  |

| 0                        | $\overline{\mathcal{D}}$ | $\mathcal D$             |  |  |

| $\mathcal{D}$            | 0                        | $\overline{\mathcal{D}}$ |  |  |

| $\overline{\mathcal{D}}$ | 0                        | $\mathcal{D}$            |  |  |

| $\mathcal{D}$            | $\mathcal{D}$            | $\overline{\mathcal{D}}$ |  |  |

| $\overline{\mathcal{D}}$ | $\overline{\mathcal{D}}$ | $\mathcal{D}$            |  |  |

$\mathcal{D}$ -algorithm summary

- If a test for a fault exists, guaranteed to generate it

- Full backtracking

- However, much faster than Boolean difference

Caveats

- $\bullet$   $\,\mathcal{D}\text{-algorithm}$  is actually more complicated

- Avoiding backtracking is important for performance

- Implications

Heuristics to make best decisions first

- $\bullet$  Should understand derivation of  $\mathcal{D}\text{-cubes}$  for arbitrary fault models

#### $\mathcal{D}$ -algorithm reference

Stanley Hurst. VLSI Testing: Digital and Mixed Analogue/Digital Techniques. Institution of Electrical Engineers, U.K., 1998

- This is one of the better references in the library

- $\bullet$  Beware: The  $\mathcal{D}\text{-algorithm}$  examples contain small errors

- $\bullet$  Given a fault, the  $\mathcal{D}\text{-algorithm}$  will generate a test for that fault

- $\bullet$  Selects a  $\mathcal{D}\text{-cube}$  of failure to excite the fault

- ullet Propagates a  ${\mathcal D}$  value to the circuit outputs be selection  ${\mathcal D}$ -cubes of propagation for gates

- Justifies gate inputs

- $\bullet$  Uses full backtracking on  $\mathcal{D}\text{-cubes}$  of failure and gate justification

The  $\mathcal{D}\text{-algorithm}$  gives us a way to generate a test for a given fault However, we need a sequence of tests for all (or most) faults

Determine all stuck-at faults for the circuit Eliminate equivalent faults while untested faults remain do

Pick a fault and use an ATPG to generate a test Append the test to a list

Use a fault simulator to determine all faults the test detects Eliminate detected faults

end while

Test sequence generation

while fault coverage is less than 90% do

Generate a random pattern – extremely fast

Use a fault simulator to determine if new faults are detected if so then

Append pattern to a list

Eliminate detected faults

end if

end while

while fault coverage is less than 99.5% do

Pick a fault and use an ATPG to generate a test

Append the test to a list

Use a fault simulator to determine all faults the test detects Eliminate detected faults

end while

### CAD survey reference

Melvin A. Breuer, Majid Sarrafzadeh, and Fabio Somenzi. Fundamental CAD algorithms. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, 18(12):1449–1475, December 2000

- Recommended by a student

- Introduces a number of important logic-level and physical-level CAD algorithms

- A useful supplement to the material in Hachtel and Somenzi's, and Sherwani's books

- ullet Introduces the  $\mathcal{D}$ -algorithm

- Fault simulation is the process of determining which faults a test

- Test generation is complicated and time-consuming

- Fault simulation is quick

- However, this approach can still be too expensive

- Recall

- Fault simulation is fast

- ATPG is slow

- Take advantage of fault simulator

Redundancies

- Sometimes a s-at-0 fault can't be detected

- Implication: Given any set of inputs to the circuit, that node can be set to 0 and the output will match the specifications

- Converse for s-a-1 faults

- Even if a portion of the circuit is not able the switch, the same function is realized

- The presence of an undetectable fault implies redundancy

- ullet How can the  ${\mathcal D}$ -algorithm can be used to simplify logic?

Redundancies

Logic terminating in the location of the stuck-at fault can be removed from the circuit and the same function will be realized

- Conventional wisdom suggests removal

- Simplify logic

- Make circuit more fully testable

ATPG for logic simplification

Can use ATPG algorithm to simplify logic

- Find a fault that is untestable due to redundancy

- Remove the redundant logic

- Repeat

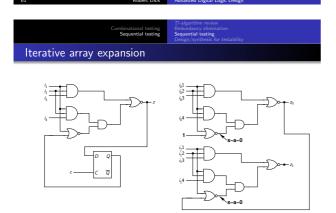

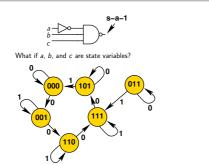

Sequential testing

- Can convert to a version of combinational testing

- Iterative array expansion

- Simulation-based

Redundancy example

Excite:  $a \neq b$ Sensitize: a = b = 0Can't excite and propegate faulty value to z!Replace s-a-0 logic with 0 Eliminate unused logic Simplify logic

Redundancy removal not always safe

- Logical equivalence may not imply true equivalence

- What happens if redundancy is intentional?

- To reduce power consumption

To ensure signal stability for use in asynchronous circuits

- Removal can

- Increase power

- Introduce races

Iterative array expansion

- Make a copy of the combinational logic for each time step

- However, now the problem converts ATPG for multiple faults

- Iterative array expansion increases the size of the combinational problem

- More importantly, changes the required fault model

- Requires ATPG for multiple faults

Modified  $\mathcal{D}$ -algorithm for iterative array

- ullet Propagate  $\mathcal{D} ext{-frontier}$  forward

- Generate new time frames as necessary

- Propagate gate justification backward

- · Generate new time frames as necessary

- However, this algorithm is not certain to find a test if one exists

- Roth's algebra not suited to sequential circuits

#### Muth's 9-valued logic

- $\bullet$   $\mathcal{D}\text{-algorithm}$  can't adequately model the possible states in sequential circuits

- Repeated effect of fault can't be modeled

- Roth's values

- 0/0, 0/1 ( $\overline{D}$ ), 1/0 (D), 1/1, X/X

- Muth's values

- 0/0, 0/1, 0/X, 1/0, 1/1, 1/X, X/0, X/1, X/X

• Generate a vector

Simulation-based sequential testing

- Determine whether that vector brought the circuit state nearer to or farther from fault excitation and sensitization

- If the state moved near to detection, append the pattern to a list

- Many of the probabilistic optimization algorithms in the third lecture can be applied for simulation-based testing

- Sequential test generation intractable for large circuits

- Some continue to work on improving test generation

- Others modify circuit structure to make test generation easier. . .

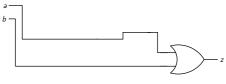

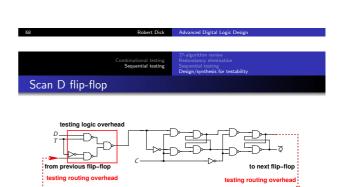

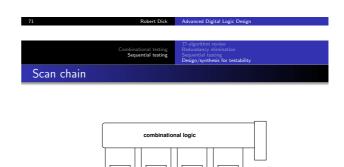

Scan-based design for test (DFT)

- If testability is considered during design or synthesis, can be made easy

- Instead of forcing ATPG to deal with synchronous testing, insert a scan chain

- Chain together (all) flip-flops and scan through an input if and only if a testing input is activated  $% \left\{ \left( 1\right) \right\} =\left\{ \left( 1\right) \right\} =\left\{$

- Greatly simplifies testing

- Converts sequential testing to combinational testing

- Testing can be slow if I/O pins limited

- Significantly increases chip area and price

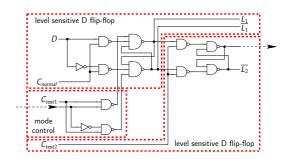

- More complicated flip-flops

- More complicated routing

I/O requirements, especially if speed required

000

- Less delay than scan-path during normal operation

- Used commercially, especially within IBM

- Pre-processing step replaces all latches with LSSD latches

- Other companies have related testing approaches

- Scan path NEC

- Scan/set Sperry Univac

- Random access scan Fujitsu

- Increased area

- 5%-15%

- Increased delay

- · Depends on critical path average combinational logic depth

- Slow when implemented serially

- Need to serially clock through every register in IC

- High pin requirements to speed up

- Testing core-based systems-on-chip (SoC)

- Related to board-level boundary-scan

- Fault injection

- Reliability evaluation

- Insert fault into system and determine reaction

- RTL synthesis for testability

- Software fault modeling and testing

- Extremely difficult problem

- Companies don't want increased complexity

- Researchers want to see their ideas used

- Therefore, reduction in interest in testing among researchers

- Therefore, reduction in interest in testing among companies

- However, companies still have huge testing problems

- Therefore, high demand for MS and Ph.D. graduates with testing experience

One option: target a research problems involving testing and another area, e.g., synthesis

LSSD

Partial scan

- Instead of scanning all latches, scan a subset

- Need to carefully select scanned latches based on

- Test coverage effects

- Testing speed

- Despite continued research on advanced testing techniques, industry continues to use full-scan

- In order for industry to accept a more complicated testing technique, the advantages must be tremendous

Companies don't like complexity

- Testing is a fairly mature field

- Some people in academia have shifted their interest away from

- It remains a huge practical problem for industry

- Low defect rate requires high test coverage

- Functional testing requires too many patterns

- Use structural testing based on a fault model, e.g., single stuck-at

- Can use fault equivalence to reduce patterns

- Can automatically generate a test for a specific fault

- Combine ATPG with fault simulator to generate a set of tests with high coverage

### Testing summary

- Can use ATPG for logic simplification redundancy

- Sequential testing difficult for large circuits

- Use DFT to make testing easier

- Use design automation to make DFT easier

# Sequential testing references

- Sujit Dey, Anand Raghunathan, and Rabindra K. Roy. Considering testability during high-level design. In *Proc. Asia & South Pacific Design Automation Conf.*, February 1998

- Survey on high-level design/synthesis for test techniques

- Kwang-Ting Cheng. Gate-level test generation for sequential circuits. ACM Trans. Design Automation Electronic Systems, 1(4):405-442, October 1996

- Survey on sequential test generation

Robert Dick Advanced Digital Logic Design

Robert Dick Advanced Digital Logic Design