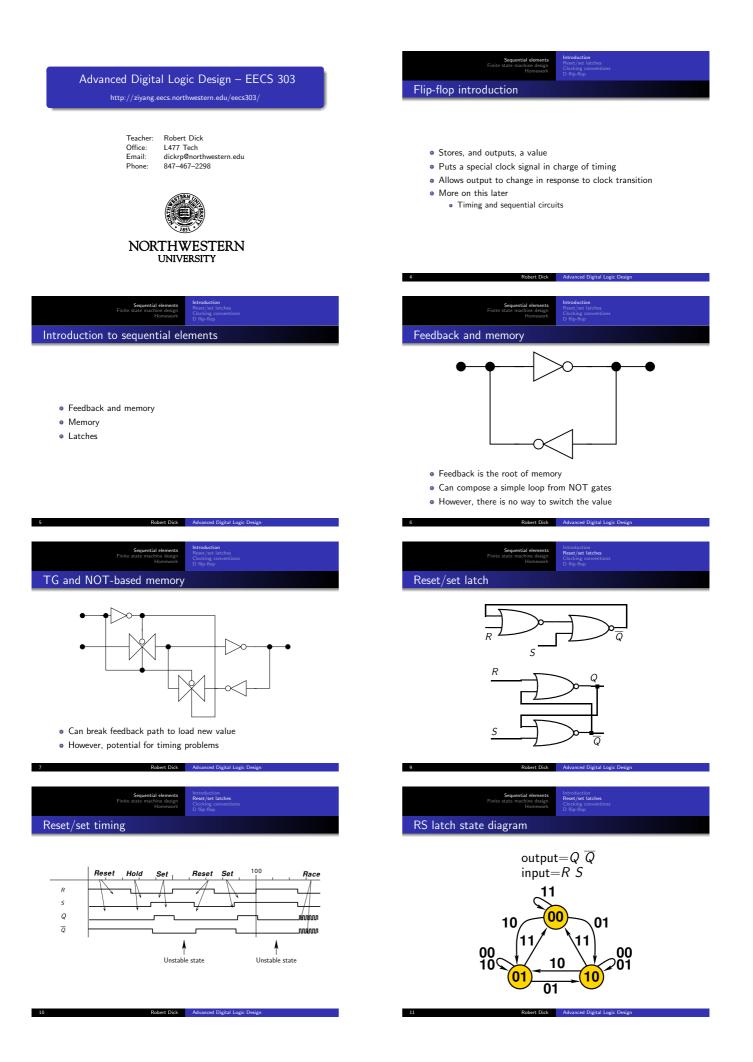

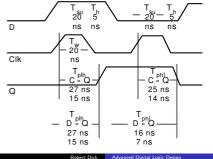

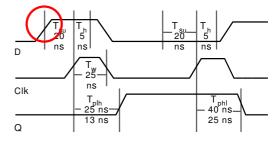

- $\bullet\,$  Setup time: Minimum time before clocking event by which input must be stable (  $T_{SU})$

- $\bullet\,$  Hold time: Minimum time after clocking event for which input must remain stable  $(T_H)$

- Window: From setup time to hold time

- Minimum clock width, T<sub>W</sub>

Usually period / 2

- Low to high propegation delay, P<sub>LH</sub>

- High to low propegation delay,  $P_{HL}$

Robert Dick Advanced Digital L

• Worst-case and typical

19

#### Sequential elements Finite state machine design Homework D flip-flop

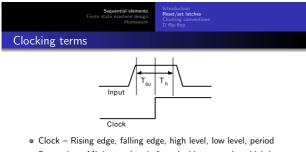

### Gated RS latch

#### Sequential elements Finite state machine design Homework

## Memory element properties

| Туре                     | Inputs sampled                                                                   | Outputs valid          |

|--------------------------|----------------------------------------------------------------------------------|------------------------|

| Unclocked latch          | Always                                                                           | LFT                    |

| Level-sensitive latch    | Clock high $(T_{SU} \text{ to } T_H)$ around falling clock edge                  | LFT                    |

| Edge-triggered flip-flop | Clock low-to-high transition $(T_{SU} \text{ to } T_H)$ around rising clock edge | Delay from rising edge |

Sequential elements Finite state machine design Homework Difference Sectors

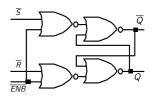

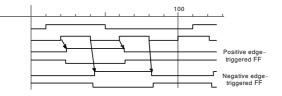

Timing for edge and level-sensitive latches

Sequential elements Finite state machine design Homework

## Latch timing specifications

Example, negative (falling) edge-triggered flip-flop timing diagram

| <b>Sequential elements</b><br>Finite state machine design<br>Homework              | Introduction<br>Reset/set latches<br>Clocking conventions<br>D flip-flop |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| FF timing specifications                                                           |                                                                          |

|                                                                                    |                                                                          |

|                                                                                    |                                                                          |

|                                                                                    |                                                                          |

| <ul> <li>Minimum clock width, T<sub>W</sub></li> <li>Usually period / 2</li> </ul> |                                                                          |

| <ul> <li>Low to high propagation delay</li> </ul>                                  | , P <sub>LH</sub>                                                        |

| <ul> <li>High to low propagation delay,</li> </ul>                                 | P <sub>HL</sub>                                                          |

| Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br><b>Clocking conventions</b><br>D flip-flop |

|----------------------------------------------------------------|---------------------------------------------------------------------------------|

| FF timing specifications                                       |                                                                                 |

### Example, positive (rising) edge-triggered flip-flop timing diagram

| Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br><b>Clocking conventions</b><br>D flip-flop |

|----------------------------------------------------------------|---------------------------------------------------------------------------------|

| RS latch states                                                |                                                                                 |

Robert Dick Adv

| S | R | $Q^+$ | $\overline{Q}^{+}$ | Notes    |

|---|---|-------|--------------------|----------|

| 0 | 0 | Q     | Q                  |          |

| 0 | 1 | 0     | 1                  |          |

| 1 | 0 | 1     | 0                  |          |

| 1 | 1 | 1     | 1                  | unstable |

|          | Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br><b>Clocking conventions</b><br>D flip-flop |  |

|----------|----------------------------------------------------------------|---------------------------------------------------------------------------------|--|

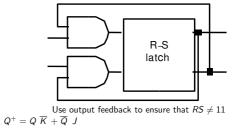

| JK latch |                                                                |                                                                                 |  |

Robert Dick A

|        | $Q^+$ | Q | Κ | J |  |

|--------|-------|---|---|---|--|

| hold   | 0     | 0 | 0 | 0 |  |

| noiu   | 1     | 1 | 0 | 0 |  |

| reset  | 0     | 0 | 1 | 0 |  |

| reset  | 0     | 1 | 1 | 0 |  |

| set    | 1     | 0 | 0 | 1 |  |

| Set    | 1     | 1 | 0 | 1 |  |

| ماسسط  | 1     | 0 | 1 | 1 |  |

| toggle | 0     | 1 | 1 | 1 |  |

|        |       |   |   |   |  |

| 25 Robert Dick                                                 | Advanced Digital Logic Design                                            |

|----------------------------------------------------------------|--------------------------------------------------------------------------|

|                                                                |                                                                          |

| Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br>Clocking conventions<br>D flip-flop |

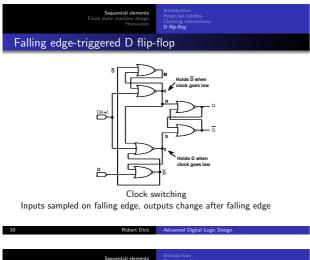

| Falling edge-triggered D flip-                                 | flop                                                                     |

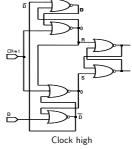

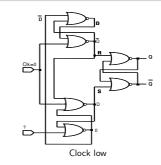

- Use two stages of latches

- When clock is high

- First stage samples input w.o. changing second stage

Second stage holds value

- When clock goes low

- First stage holds value and sets or resets second stage

Second stage transmits first stage

- $Q^+ = D$

23

• One of the most commonly used flip-flops

bert Dick

nced Digital Logic D

| 32 Robert Dick                                                 | Advanced Digital Logic Design                                            |

|----------------------------------------------------------------|--------------------------------------------------------------------------|

| Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br>Clocking conventions<br>D flip-flop |

| JK flip-flop                                                   |                                                                          |

- Versatile building block

- Building block for D and T flip-flops

- Has two inputs resulting in increased wiring complexity

- Don't use master/slave JK flip-flops

- Ones or zeros catching

- Edge-triggered varieties exist

# Falling edge-triggered D flip-flop

obert Dick Ad

- Storage element in narrow width clocked systems

- Dangerous

- Fundamental building block of many flip-flop types

- D flip-flop

- Minimizes input wiring

- Simple to use

- Common choice for basic memory elements in sequential circuits

| 34 Robert Dick                                                 | Advanced Digital Logic Design                                            | 35                             |

|----------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|

|                                                                |                                                                          |                                |

| Sequential elements<br>Finite state machine design<br>Homework | Introduction<br>Reset/set latches<br>Clocking conventions<br>D flip-flop | <b>Seque</b><br>Finite state n |

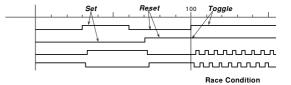

| Toggle (T) flip-flops                                          |                                                                          | Asynchronous inputs            |

|                                                                |                                                                          |                                |

- How can a circuit with numerous distributed edge-triggered flip-flops be put into a known state

- · Could devise some sequence of input events to bring the machine into a known state

- ComplicatedSlowNot necessarily possible, given trap states

- Can also use sequential elements with additional asynchronous reset and/or set inputs

- State changes each clock tick

- Useful for building counters

- Can be implemented with other flip-flops

- JK with inputs high

- D with XOR feedback

Robert Dick Advanced Digital Logic D

| Finite s          | Sequential elements<br>Late machine design<br>Homework<br>D flip-flop |                | Sequential elements<br>Finite state machine design<br>Homework D flip-flop<br>D flip-flop |

|-------------------|-----------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------|

| tch and flip-flop | equations                                                             | Latch and flip | -flop equations                                                                           |

|                   |                                                                       |                |                                                                                           |

|                   |                                                                       |                |                                                                                           |

| RS                | $Q^+ = S + \overline{R} Q$                                            | JK             |                                                                                           |

|                   | $Q^{*} = 3 + K Q$                                                     | _              | $Q^+ = J \ \overline{Q} + \overline{K} \ Q$                                               |

|                   | $Q^+ = D$                                                             | Т              | $Q^+ = \mathcal{T} \oplus Q$                                                              |

|                   |                                                                       |                | <b>~</b> · · <b>~ ~</b>                                                                   |

|                   |                                                                       |                |                                                                                           |

|                   |                                                                       |                |                                                                                           |

|                   | Robert Dick Advanced Digital Logic Design                             | 39             | Robert Dick Advanced Digital Logic Design                                                 |

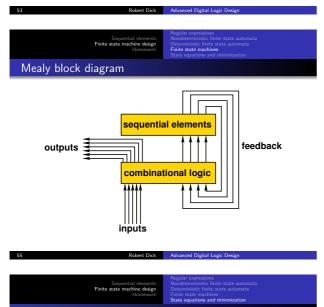

| Sequential elements<br>Finite state machine design<br>Homework | Regular expressions<br>Nondeterministic finite state automata<br>Deterministic finite state automata<br>Finite state machines<br>State equations and minimization |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sequential FSM design example                                  |                                                                                                                                                                   |  |

- $\bullet\,$  We'll walk through the design of an example finite state machine (FSM)

- Some of the stages will be covered in more detail in later lectures

- I want you to have a high-level understanding of our overall goal before covering every detail of FSM synthesis

$0\ 1\ 1\ 1$

Robert Dick

| Sequential elements<br>Finite state machine design<br>Homework | Regular expressions<br>Nondeterministic finite state automata<br>Deterministic finite state automata<br>Finite state machines<br>State equations and minimization |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

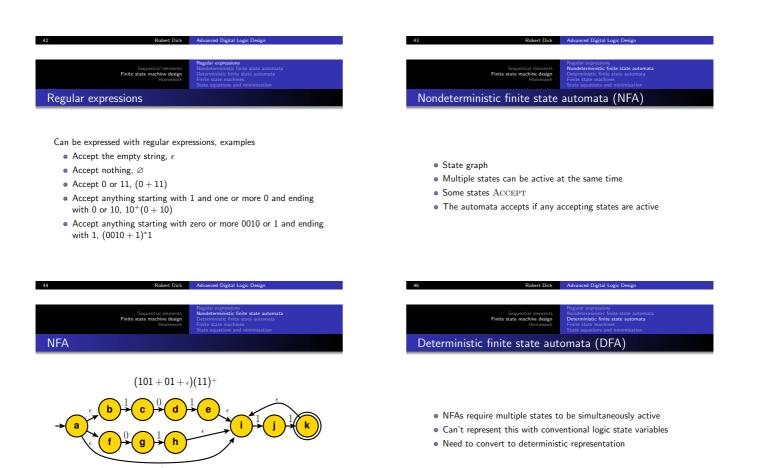

| Regular expressions                                            |                                                                                                                                                                   |

Robert Dick Advanced Digital Logic D

- Naturally express control

- However, no simple direct HW implementation

- We want to get to sequential logic

- $\bullet\,$  Need to go though other stages first

Seq Finite state

|            | Sequential elements<br>Finite state machine design<br>Homework | Regular expressions<br>Nondeterministic finite state automata<br>Deterministic finite state automata<br>Finite state machines<br>State equations and minimization |

|------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFA to FSM |                                                                |                                                                                                                                                                   |

|            |                                                                |                                                                                                                                                                   |

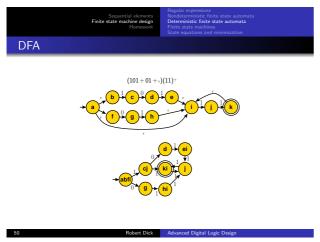

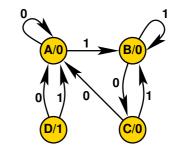

- DFA may only accept or reject

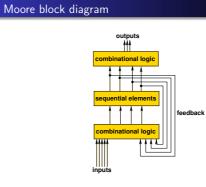

- Simple to convert Moore FSM

- Add explicit output values to states

Introduction to state reduction

Robert Dick Advanced Digital Logic

Moore FSMs

|                                                                | Regular expressions                                                                                                                        |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sequential elements<br>Finite state machine design<br>Homework | Nondeterministic finite state automata<br>Deterministic finite state automata<br>Finite state machines<br>State equations and minimization |  |

| Introduction to state reduction                                |                                                                                                                                            |  |

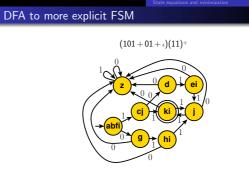

|    | s <sup>+</sup> |    |   |

|----|----------------|----|---|

| s  | 0              | 1  | q |

| AC | AC<br>AC       | В  | 0 |

| В  | AC             | В  | 0 |

| D  | AC             | AC | 1 |

Robert Dick Advanced Digital Logic Desig

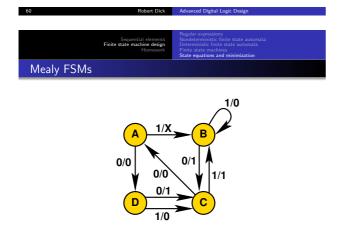

####

| Finite state machine design<br>Homework | Deterministic finite state automata<br>Finite state machines<br>State equations and minimization |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|--|

| Mealy tabular form                      |                                                                                                  |  |

|                                         |                                                                                                  |  |

|                                         |                                                                                                  |  |

<page-header><table-cell><section-header><section-header><complex-block><image>

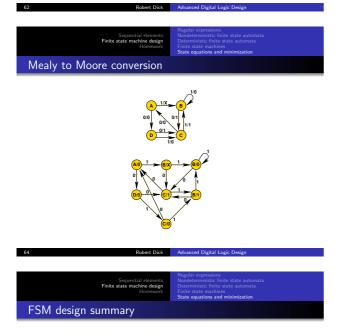

- Specify requirements in natural form regular expression or NFA

- Converting from NFA to DFA is straightforward

- $\bullet\,$  Converting from DFA to FSM is straightforward

- Minimize the number of states using compatible states, class sets, and binate covering

- ${\ensuremath{\, \bullet \,}}$  Assign values to states to minimize logic complexity

- Allow only adjacent or path transitions for asynchronous machines

- Optimize implementation of state and output functions

• M. Morris Mano and Charles R. Kime. *Logic and Computer Design Fundamentals*. Prentice-Hall, NJ, third edition, 2004

Robert Dick Advanced Digital Logic De

- Chapter 7

- Chapter 6

#### Sequential elements Finite state machine design Homework

Video controller repair lab

69

- Design a finite state machine based on an English problem specification

- The design problem isn't very difficult

- Going from a real-world problem to a formal representation may be difficult

Robert Dick Advanced Digital Logic Design

- Be careful not to use too many state variables!!!

- Could easily turn it from a 6-hour lab to a 12-hour lab

Sequential el Finite state machine

Next lecture

70

• More detail and examples on FSM design and optimization

Robert Dick Advanced Digital Logic Design