- Need to map to efficient implementation in target technology

- Target technology consists of a set of gates

- Each has area, power consumption, and timing properties

- Map to those gates minimizing some combination of area, power, and delay

Robert Dick Advanced Digital Logic Design

| Technology mapping<br>Homework | Overview<br>Binate covering formulation<br>Tree covering formulation<br>Decomposition |

|--------------------------------|---------------------------------------------------------------------------------------|

| Technology mapping example     | e library                                                                             |

| gate   | area cost |

|--------|-----------|

| NOT    | 1         |

| NAND2  | 2         |

| NAND3  | 3         |

| NAND4  | 4         |

| XNOR2  | 5         |

| ANDOR4 | 4         |

|        |           |

| 7 Robert Dick                                  | Advanced Digital Logic Design                                                         |

|------------------------------------------------|---------------------------------------------------------------------------------------|

| Technology mapping<br>Homework                 | Overview<br>Binate covering formulation<br>Tree covering formulation<br>Decomposition |

| Technology mapping for area as binate covering |                                                                                       |

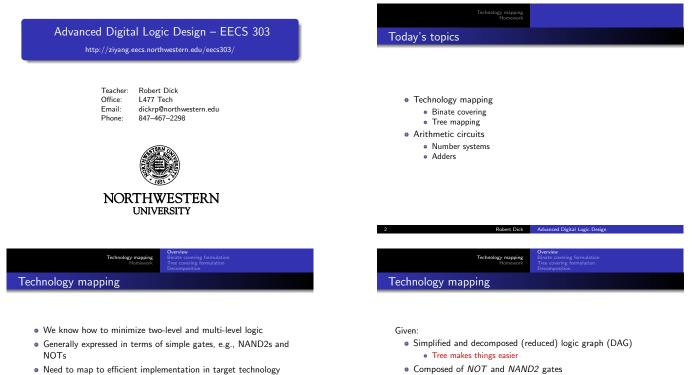

- Find all possible matches

- However, complete cover insufficient

- Need match outputs to align with inputs of other matches

Robert Dick Advanced Digital Logic Design

• Can represent problem as binate covering

• Library: NOT, NAND2, NAND3, ANDOR4 (AO4), and XNOR

Robert Dick Advanced Digital Logic D

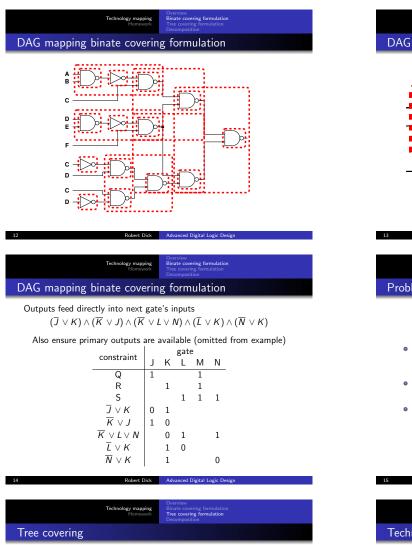

Decide minimal area/delay/power cost mapping from logic tree to

Technology m

Potentially overlapping maps

rt Dick

ology mapping

Binate covering

gates

technology library

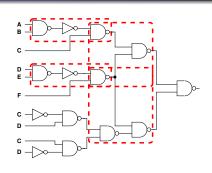

| term  | column |   |   |   |

|-------|--------|---|---|---|

| term  | А      | В | С | D |

| $J_1$ | 1      |   |   |   |

| $J_2$ | 1      | 1 |   |   |

| $J_3$ |        | 1 | 1 |   |

| $J_4$ |        |   | 1 | 1 |

| $J_5$ | 1      |   | 0 |   |

Robert Dick Advanced Digital Logic

• Find a set of columns, S, such that, for every row • A 1-colum in the row is in S or...

• ... a 0-column in the row is not in S

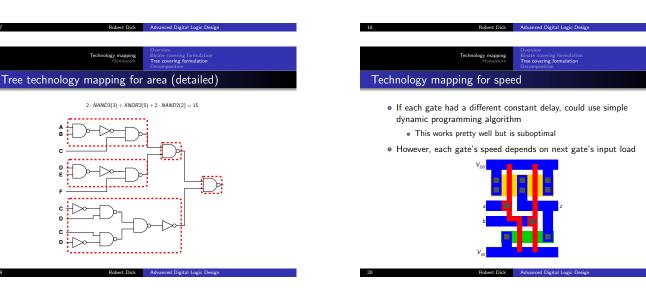

- Split DAG at multiple output nodes to form trees

- Optimally and quickly map trees using dynamic programming

- Reconnect result into a DAG

- Locally improve connection points

- Result: Nearly (but not quite) optimal, fast DAG mapping

| Technology mapping<br>Homework | Binate covering formulation<br>Tree covering formulation<br>Decomposition |

|--------------------------------|---------------------------------------------------------------------------|

| mapping binate coverin         | g formulation                                                             |

## $(\overline{J} \lor K) \land (\overline{K} \lor J) \land (\overline{K} \lor L \lor N) \land (\overline{L} \lor K) \land (\overline{N} \lor K)$

Technology mapping for area complexity

- Reduced logic tree RLT = (V, E)

- Technology library with T gates

- $\bullet\,$  Maximum gate size of S, i.e., no gate covers more than S vertices

Algorithm is

- Linear in |V|

- Linear in T

- Exponential in S

## Technology mapping

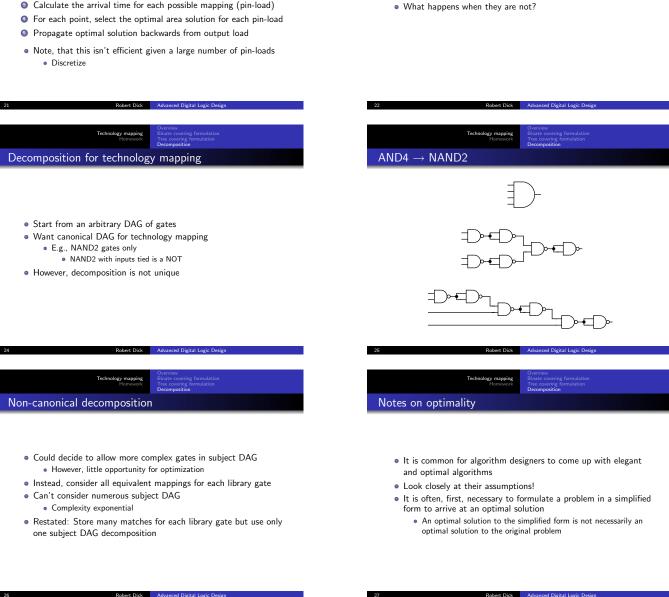

Two-pass delay optimization

Problem: Optimize area under timing constraint

- Ind the set of all possible pin-loads

- Irom leafs, build array of minimal-area solutions, one for each pin-load

- Salculate the arrival time for each possible mapping (pin-load)

- The technology mapping algorithms in this lecture are polynomial-time (fast) and optimal...

- ... however, they aren't polynomial-time (fast) in every term • Maximum library gate size

- ... or optimal for the original problem

- The original problem can be a DAG, instead of a tree

- The decomposition is not unique

- · Better solutions might be possible for other decompositions

Robert Dick Advanced Digital Logic D

- ogy mapping

- Notes on optimality

- The algorithms are high-quality and efficient

Technology mapping

Technology mapping

• Are circuits really trees?

- However

- They are only optimal with respect to the simplified inputs

- . They are only polynomial in the most important terms

- This situation is very common in EDA/CAD because the original problems are often  $\mathcal{NP}\text{-}\mathrm{complete}$

- Too slow to solve for large problem instances

- Whenever you see or use the word "optimal", think very carefully about what is meant

Robert Dick Advanced Digital Logic

## Technology mapping

Technology mapping summary

- Technology mapping is taking a set of functions and determining how to implement them using gates from a library

- Optimal and fast approaches exist for trees

- However, no optimal solution is known for arbitrary circuit topologies

- $\bullet\,$  This is what you are doing when you type "map" in SIS

Next lecture

Robert Dick Advanced Digital Logic De

- Multipliers and ALUs

- Sequential logic networks

- Latches (RS Latch)

- Flip-flops (D and JK)

- Timing issues (setup and hold times)

Technology mapping

| 30         | Robert Dick                    | Advanced Digital Logic Design |  |

|------------|--------------------------------|-------------------------------|--|

|            |                                |                               |  |

|            |                                |                               |  |

|            | Technology mapping<br>Homework |                               |  |

| _          |                                |                               |  |

| Reading as | signment                       |                               |  |

• M. Morris Mano and Charles R. Kime. *Logic and Computer Design Fundamentals*. Prentice-Hall, NJ, third edition, 2004

Robert Dick Advanced Digital Logic Design

• Chapter 5

33