### Advanced Digital Logic Design - EECS 303

http://zivang.eecs.northwestern.edu/eecs303/

Teacher: Robert Dick Office: L477 Tech

Email: dickrp@northwestern.edu

Phone: 847-467-2298

Administration Implementation technologies Scripting languages Review of implementation technologies Homework

Lab two

- Lab two is more substantial than lab one

- If you find a problem and figure out the solution, yourself, please send me an email or post to the newsgroup

- Don't think you'll be able to fully understand the effects all the SIS commands, options, and sequences will have

- If you have a basic understanding of how to get reasonably good results with the software, that's good

4 Robert Dick

Administration

Implementation technologies

Review of im

- We have considered implementing Boolean functions using discrete logic gates

- NOT, AND, OR, NAND, NOR, XOR, and XNOR

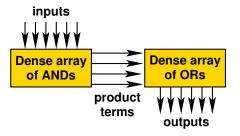

- Can arrange AND and OR gates (or NAND and NOR gates) into a general array structure

- Program array to implement logic functions

- Two popular variants

- Programmable logic arrays (PLA) and programmable array logic (PAL)

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Scripting languages

Review of implementation technologies

Homework

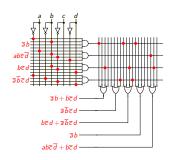

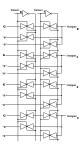

SOP programmable array block diagram

Implementation technologie

Scripting language

Review of implementation technologie

### Today's topics

- Can use today's class for Q&A

- PALs/PLAs

- Review, Q&A on MOS transistors

- Multiplexers, Demultiplexers

- Transmission gates

- Perl/Python

Advanced Digital Logic Design

Administration

Implementation technologies

Service of implementation technologies

Review of implementation technologies

Homework

Midterm exam

Suggesting 21 or 23 October

Advanced Digital Logic Design

PALs and PLAs

CMOS for logic states

Transmission gates and MUXs

- $\bullet$  Pre-fabricated building block of many AND and OR (or NAND and NOR) gates

- "Personalized" (programmed) by making or breaking connections among the gates

9 Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting Januages

Review of implementation technologies

PALs and PLAs

CMOs for logic gates

Transmission gates and MUXs

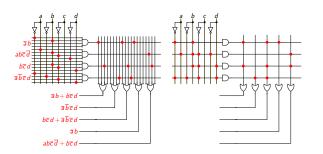

PLAs efficiency

- PLAs can share terms Share product terms

- Consider the following set of functions

Implementation technologies Scripting languages Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MHX

### PLA programming

All connections available

#### All exist

Some removed

#### None exist

Connections made

Robert

Implementation technologies

DALE and DLAS

# PLA diagram shorthand

Robert Di

Advanced Digital Logic Design

Administration Implementation technologies Scripting languages Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MUVe

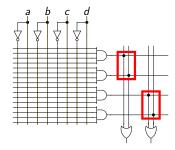

### PAL/PLA differences

### PAL

- $\bullet$  Only the AND array is programmable

- $\bullet$  A column of the OR array only has access to a subset of the product terms

- Generally, no sharing of product terms

### PLA

- A column has access to any desired product terms

- Can share product terms

Rober

Advanced Digital Logic Design

Implementation technologies Scripting languages Review of implementation technologies PALs and PLAs

CMOS for logic gates

Transmission gates and MUX

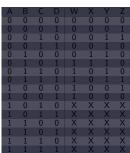

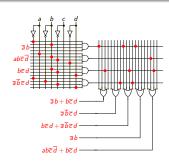

# BCD-Gray code converter

| A A A A

Implementation technologies Scripting languages Review of implementation technologies

ges CMOS gies Transm

### PLA programming

Robert Dick

Advanced Digital Logic Design

Administration Implementation technologies Scripting languages w of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

# Shorthand – Draw subset of wires

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

### PAL/PLA differences

D. I. . D. I

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs CMOS for logic gates Transmission gates and MUXs

# BCD-Gray code converter

Advanced Digital Logic Design

# Minimized BCD-Gray functions

$$W = A + BD + BC$$

$$X = B\overline{C}$$

$$Y = B + C$$

$$Z = \overline{A}\overline{B}\overline{C}D + BCD + A\overline{D} + \overline{B}C\overline{D}$$

Advanced Digital Logic Design

Implementation technologies

Scripting languages

v of implementation technologies

PALS and PLAS CMOS for logic gates Transmission gates and MUXs

# BCD-Gray PAL

Robert Di

Advanced Digital Logic Design

Administration Implementation technologies Scripting languages Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MIIXs

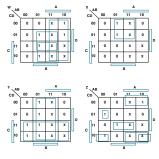

### Comparator Karnaugh map

Robert

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

CMOS for logic gates

Transmission gates and MUX

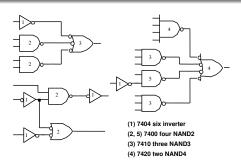

# **Transistors**

- Basic device in NMOS and PMOS (CMOS) technologies

- Can be used to construct any logic gate

Implementation technologies Scripting languages Review of implementation technologies

PALs and PLAs CMOS for logic gates

# BCD-Gray discrete logic

Pohort Dick

Administration

Implementation technologies

Scripting languages

PALs and PLAs CMOS for logic gates

Comparator example

Determine whether a the first two-bit number (AB) is

- Equal to (EQ),

- Not equal to (NE),

- Less than (LT),

- Or greater than (GT)

- a second two-bit number (CD)

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

# Comparator PLA

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

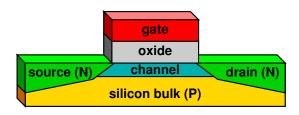

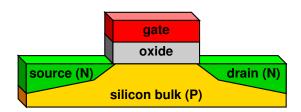

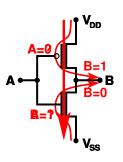

NMOS transistor

Implementation technologies Scripting languages Review of implementation technologies

CMOS for logic gates

Transmission gates and MUX

NMOS transistor

# Metal–oxide semiconductor (MOS)

- Then, it was polysilicon-oxide semiconductor

- Now, it is MOS again

P-type bulk silicon doped with positively charged ions

N-type diffusion regions doped with negatively charged ions

### Gate can be used to pull a few electrons near the oxide

Forms channel region, conduction from source to drain starts

Robert Dick Advanced Digital Logic Design

Implementation technologies Scripting languages PALs and PLAs CMOS for logic gates Transmission gates and MUXs

CMOS NAND gate

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

PALs and PLAs CMOS for logic gates

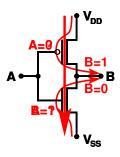

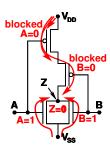

CMOS inverter operation

Robert I

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MU)

NOR operation

Implementation technologie Scripting language Review of implementation technologie Homewor PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

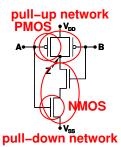

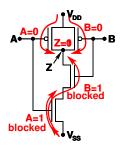

**CMOS**

- NMOS turns on when the gate is high

- PMOS just like NMOS, with N and P regions swapped

- PMOS turns on when the gate is low

- NMOS good at conducting low (0s)

- PMOS good at conducting high (1s)

- Use NMOS and PMOS transistors together to build circuits

- Complementary metal oxide silicon (CMOS)

Advanced Digital Logic Design

Advanced Digital Logic Design

Advanced Digital Logic Design

Advanced Digital Logic Design

PALs and PLAs

CMOS or logic gates

Transmission gates and MUXs

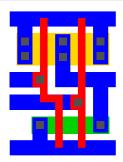

CMOS NAND gate layout

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs CMOS for logic gates

NAND operation

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

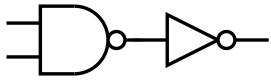

CMOS inefficient for ANDs/ORs

- Recall that NMOS transmits low values easily. . .

- ...transmits high values poorly

- PMOS transmits high values easily. . .

- ... transmits low values poorly

Robert Dick

Advanced Digital Logic Design

Implementation technologies Scripting languages Review of implementation technologies

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

# CMOS inefficient for ANDs/ORs

- ullet  $V_T$ , or threshold voltage, is commonly 0.7 V

- ullet NMOS conducts when  $V_{GS} > V_T$

- $\bullet$  PMOS conducts when  $V_{GS} < -V_T$

- What happens if an NMOS transistor's source is high?

- Or a PMOS transistor's source is low?

- Alternatively, if one states that  $V_{TN}=0.7~{

m V}$  and  $V_{TP}=-0.7~{

m V}$  then NMOS conducts when  $V_{GS}>V_{TN}$  and PMOS conducts when  $V_{GS}< V_{TP}$

Advanced Digital Logic Design

PALS and PLAS

CMOS for logic gates

Transmission gates and MUXs

CMOS inefficient for ANDS/ORS

- If an NMOS transistor's input were  $V_{DD}$  (high), for  $V_{GS}>V_{TN}$ , the gate would require a higher voltage than  $V_{DD}$

- If an PMOS transistor's input were  $V_{SS}$  (low), for  $V_{GS} < V_{TP}$ , the gate would require a lower voltage than  $V_{SS}$

$\ensuremath{\mathsf{AND}}/\ensuremath{\mathsf{OR}}$  requires more area, power, time

Advanced Digital Logic Design

Administration Implementation technologies Review of implementation technologies Review of Implementation technologies Tontenoors

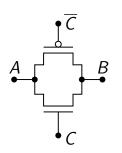

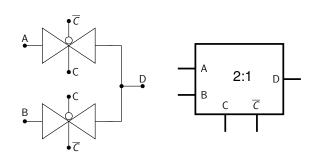

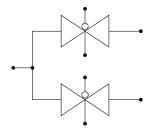

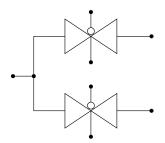

CMOS transmission gate (TG)

Administration

Implementation technologies

Review of implementation technologies

Homework

NMOS transistor

Administration

Implementation technologies

Homework

AMOS to logic gates

CMOS for logic gates

Transmission gates and MUXs

Administration Implementation technologies Scripting languages Review of implementation technologies Homework

Implications of using CMOS

Robert Dick

Advanced Digital Logic Design

Advanced Digital Logic Design

Advanced Digital Logic Design

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

NAND/NOR easy to build in CMOS

Advanced Digital Logic Design

PLAs and PLAs

CMOS for logic gates

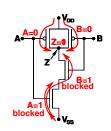

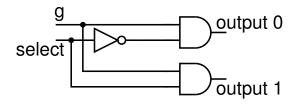

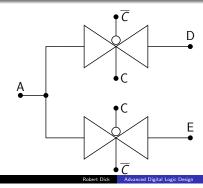

CMOS transmission gates and MUXs

CMOS transmission gates with MUXs

NMOS is good at transmitting 0s

Bad at transmitting 1s

PMOS is good at transmitting 1s

Bad at transmitting 0s

To build a switch, use both: CMOS

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

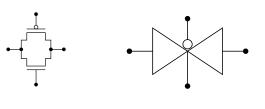

Other TG diagram

Administration

Implementation technologies

Scripting languages

Homework

Transmission gates and MUXs

Robe

Advanced Digital Logic Desig

Robert Di

Advanced Digital Logic Design

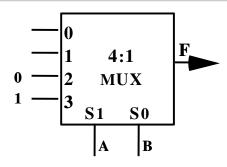

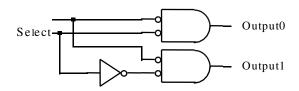

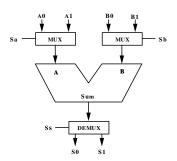

# MUX functional table

# Multiplexer (MUX) definitions

- Also called selectors

- 2<sup>n</sup> inputs

- n control lines

- One output

Robert I

Advanced Digital Logic Design

Implementation technologies Scripting languages view of implementation technologies

PALS and PLAS EMOS for logic gates Fransmission gates and MUXs

MUX truth table

| 1 | 10 | C | Ζ |

|---|----|---|---|

| 0 | 0  | 0 | 0 |

| 0 | 0  | 1 | 0 |

| 0 | 1  | 0 | 1 |

| 0 | 1  | 1 | 0 |

| 1 | 0  | 0 | 0 |

| 1 | 0  | 1 | 1 |

| 1 | 1  | 0 | 1 |

| 1 | 1  | 1 | 1 |

Robert Dick

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

CMOS for logic gates Transmission gates and MUXs

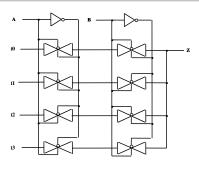

# MUX using TGs

Robert

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

CMOS for logic gates

Transmission gates and MUXs

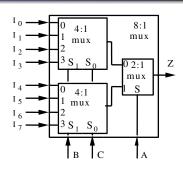

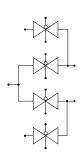

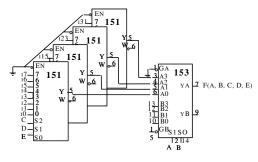

# Hierarchical MUX implementation

Robert

Administration Implementation technologies Scripting languages Review of implementation technologies

PALS and PLAS CMOS for logic gates Transmission gates and MUXs

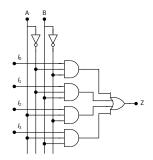

MUX using logic gates

Robert Dick

Advanced Digital Logic Design

Administration Implementation technologies Scripting languages Review of implementation technologies Homework

ALs and PLAs MOS for logic gates

MUX

Robert Dick

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

PALs and PLAs

CMOS for logic gates

Transmission gates and MUXs

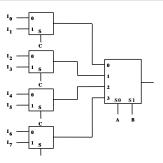

# Alternative hierarchical MUX implementation

5

ert Dick Advanced Digital

Robert Dick

Advanced Digital Logic Desig

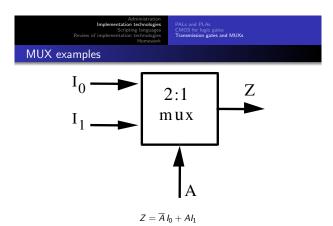

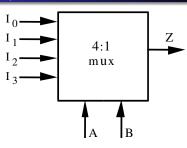

Robert Dick Advanced Digital Logic Design MUX examples

> $Z = \overline{A}\,\overline{B}\,\overline{C}\,I_0 + \overline{A}\,\overline{B}\,CI_1 + \overline{A}\,B\,\overline{C}\,I_2 + \overline{A}\,BCI_3 +$  $A\overline{B} \overline{C} I_4 + A\overline{B} C I_5 + AB\overline{C} I_6 + ABC I_7$

Robert Dick Advanced Digital Logic Design

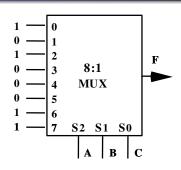

MUX example

$$F(A, B, C) = \sum_{A} (0, 2, 6, 7)$$

$$= \overline{A} \overline{B} \overline{C} + \overline{A} B \overline{C} + AB \overline{C} + ABC$$

# Lookup table implementation

MUX examples

$Z = \overline{A}\,\overline{B}\,I_0 + \overline{A}\,BI_1 + A\overline{B}\,I_2 + ABI_3$

Robert Dick Advanced Digital Logic Design

MUX properties

- A  $2^n : 1$  MUX can implement any function of n variables

- ullet A  $2^{n-1}:1$  can also be used

- Use remaining variable as an input to the MUX

Truth table

MUX example

$$F(A, B, C) = \sum_{A \in \overline{B}} (0, 2, 6, 7)$$

=  $\overline{A} \overline{B} \overline{C} + \overline{A} B \overline{C} + AB \overline{C} + ABC$

Therefore,

$$\overline{A}\overline{B} \to F = \overline{C}$$

$\overline{A}B \to F = \overline{C}$

$A\overline{B} \to F = 0$

$AB \to F = 1$

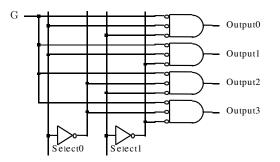

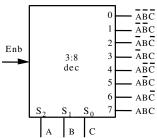

Demultiplexer (DMUX) definitions

- Closely related to decoders

- n control signals

- Single data input can be routed to one of  $2^n$  outputs

- A genius colleague is an ASIC (Application-Specific Integrated Circuit) design engineer at PMC-Sierra

- He glues together standard cells to make high-performance special-purpose circuits

- When he talks about perl, his eyes get all watery

- Why do digital design engineers get so excited about a system administrator's scripting language?

Lookup table implementation

Decoders vs. demultiplexers

- Decoders have n inputs and 2<sup>n</sup> outputs.

- They activate only the output indicated by the binary input value.

- Demultiplexers have one input,  $2^n$  select lines, and  $2^n$  outputs.

- They route the input to the output indicated by the binary select value, and inactivate the other outputs.

- In practice, decoders have an output enable input.

- If you treat a decoder output enable as a demultiplexer input and treat the decoder inputs as demultiplexer select lines, the two are equivalent.

- In practice decoders and demultiplexers are interchangeable.

- Lab two has a tedious portion

- You'll need to lookup gates in a library

- I wrote a perl and python script for you to accelerate this process ... and serve as examples

- You'll still need to do this manually once

- Can use my scripts afterward

- Read and understand it

- Different tools that don't quite work together

- Translation

- Tools that don't quite finish the job

- Pre-post processing

- Poor support for complex testing, e.g., comparing a high-level language model's behavior with circuit simulation

- 10 processing and command scripting

- Perl (python, etc.) allow quick (although sometimes inelegant) solutions to these problems

Robert Dick Advanced Digital Logic D

```

Implementation technologies

Scripting languages

Review of implementation technologies

```

### Perl code example motivation – Library

```

GATE

"1310:physical"

16

O=!1A;

PIN

* INV 1 999 1 .2 1 .2

"1120:physical"

GATE

24

O=!(1A+1B);

PIN

* INV 1 999 1 .2 1 .2

"1130:physical"

GATE

32

0=!(1A+1B+1C);

PIN

* INV 1 999 1 .2 1 .2

"1220:physical"

Π=!(1A*1B):

GATE

24

PIN

* INV 1 999 1 .2 1 .2

```

Robert Dick Advanced Digital Logic Design

Implementation technologie: Scripting language: Review of implementation technologie:

# Perl code example

```

# Make sure number of args is correct

if (scalar @ARGV != 2) {

die "Usage: lookup-gate.perl " .

"[library] [file]\n";

}

my $lib = $ARGV[0];

my $file = $ARGV[1];

my %lab_op = ();

```

Robert D

Robert Dick Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

eview of implementation technologies

### Perl code example

```

# Loop on input file

open FILE, "< $file";

while (<FILE>) {

# Chop up the line on whitespace

my @ln = split ' ', $_;

if (scalar(@ln) == 3) {

# Grab the node and label

my ($node, $lab) = @ln;

```

Robert

Advanced Digital Logic Design

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

### Perl code output

```

Node [348] implemented with gate 0=!(1A*1B+!1A*!1B);

Node {cout} implemented with gate 0=1A*1B+2C*2D;

Node [345] implemented with gate 0=!1A;

Node [364] implemented with gate 0=!1A;

Node {sum} implemented with gate 0=!((1A+1B)*(2C+2D));

```

Implementation technologie

Scripting language

Review of implementation technologie

### Perl code example motivation – Gates

```

[348] 2310:physical 40.00 {cout} 1970:physical 56.00 [345] 1310:physical 16.00 [364] 1310:physical 16.00 {sum} 1860:physical 40.00

```

Robert

Implementation technologies

Scripting languages

Review of implementation technologies

# Perl code example

```

# Read in library

open LIB, "< $lib";

while (<LIB>) {

if (m/^GATE\s+"([^"]+)"\s+\d+\s+(.+)$/) {

# Put the data into a hash map

my ($label, $op) = ($1, $2);

$lab_op{$label} = $op;

}

} close LIB;

```

Robert Dick Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

### Perl code example

Rober

Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

Review of implementation technologies

Homework

### Python code example

```

# Make sure number of args is correct

if len(sys.argv) < 3:

print 'Usage: lookup-gate.py [library] [file]'

sys.exit(0)

lib, file = sys.argv[1:]

lab_op = dict();</pre>

```

### Python code example

```

# Read in library

fl = open(lib)

for ln in fl.readlines():

m = re.match('^GATE\s+"([^"]+)"\s+\d+\s+(.+)$', ln)

if m:

# Put the data into a hash map

label, op = m.group(1, 2)

lab_op[label] = op

fl.close()

```

Robert Dick Advanced Digital Logic Design

Back to implementation technologies What is this?

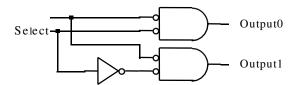

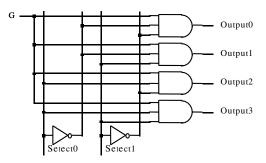

### Active-high 2:4 decoder/demultiplexer

# Dangers when implementing with TGs

What if an output is not connected to any input?

### Python code example

# Loop on input file fl = open(file)

for ln in fl.readlines():

# Chop up the line on whitespace ln\_ar = ln.split() if len(ln\_ar) == 3:

# Grab the node and label node, lab = ln\_ar[:2]

$\mbox{\tt\#}$  Look it up in the hash map and display the results print 'Node %s implemented with gate %s' % (node, lab\_op fl.close()

Robert Dick Advanced Digital Logic Des

What is this?

### Active-low 2:4 decoder/demultiplexer

# Consider undriven inverter inputs

# Dangers when implementing with TGs

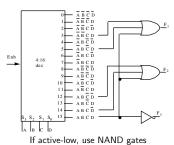

# Demultiplexer

# Demultiplexers as building blocks

Generate minterm based on control signals

Scripting language Review of implementation technologie

# Demultiplexers as building blocks

# Set all outputs

# TG decoder/demultiplexer implementation

Consider alternative paths

### Example function

$$\begin{split} F_1 &= \overline{A}\,\overline{B}\,CD + \overline{A}\,B\overline{C}\,D + ABCD \\ F_2 &= AB\overline{C}\,\overline{D} + ABC = AB\overline{C}\,\overline{D} + ABC\overline{D} + ABCD \\ F_3 &= \overline{A} + \overline{B} + \overline{C} + \overline{D} = \overline{ABCD} \end{split}$$

# Implementation of 32:1 MUX

# Administration Implementation technologies Scripting languages Review of implementation technologies

# 1:32 demultiplexer

Robert

Advanced Digital Logic Design

Administration Implementation technologies Scripting languages ew of implementation technologies

# Summary

- Q&A

- PALs/PLAs

- Review, Q&A on MOS transistors

- Multiplexers, Demultiplexers

- Transmission gates

- Perl/Python

98 Robert Dick Advanced Digital Logic Design

Administration

Implementation technologies

Scripting languages

# Next lecture

- ROMs

- Multilevel logic minimization

- Review: NAND/NOR implementation

101 Robert Dick Advanced Digital Logic Desig

Administration

Implementation technologi

Scripting languag

Review of implementation technologi

# Multiple I/O circuit

Robert Dick

Advanced Digital Logic Design

Implementation technologies

Scripting languages

ew of implementation technologies

Homework

Homework

# Recommended reading

- M. Morris Mano and Charles R. Kime. Logic and Computer Design Fundamentals. Prentice-Hall, NJ, fourth edition, 2008

- Chapters 3 and 4

# Lab two

Espresso and SIS logic minimization

Robert Dic

dvanced Digital Logic Design