## Advanced Digital Logic Design - EECS 303

http://ziyang.eecs.northwestern.edu/eecs303/

Teacher: Robert Dick Office: L477 Tech dickrp@northwestern.edu Email: Phone 847-467-2298

Specification

- Sometimes, system specified in way that naturally maps to FSM

- Sometimes, path from specification to FSM is unclear

- ${\ensuremath{\, \bullet }}$  Transform the specifications so they can naturally be represented as FSMs

- $\bullet~$  E.g., regular expression  $\rightarrow~$  NFA  $\rightarrow~$  DFA  $\rightarrow~$  FSM

- It's fine to go directly to FSM

- Use transformations when they help you

## FSM design overview Specification State diagram for FSM • State table

- State minimization

- State assignment

- Derive state variable and output functions

- Simplify and implement the functions

### Word description to state diagram

• Design a vending machine controller that will release (output signal r) an apple as soon as 30¢ have been inserted

ert Dick Adv

- The machine's sensors will clock your controller when an event occurs. The machine accepts only dimes (input signal d) and quarters (input signal q) and does not give change

- When an apple is removed from the open machine, it indicates this by clocking the controller with an input of  $\boldsymbol{d}$

- The sensors use only a single bit to communicate with the controller

### Word description to state diagram

• We can enumerate the inputs on which an apple should be released

$$ddd + ddq + dq + qd + qq$$

$$d(dd + dq + q) + q(d + q)$$

$$d(d(d + q) + q) + q(d + q)$$

For

$$d$$

,  $i = 0$ , for  $q$ ,  $i = 1$

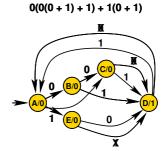

$0(0(0+1)+1)+1(0+1)$

# Word description to state diagram

State diagram to state table

| current<br>state | ne<br>sta<br>i=0 | ×t<br>ate<br>  i=1 | output ( <i>r</i> ) |

|------------------|------------------|--------------------|---------------------|

| A                | В                | E                  | 0                   |

| В                | C                | D                  | 0                   |

| С                | D                | D                  | 0                   |

| D                | A                | Α                  | 1                   |

| Е                | D                | D                  | 0                   |

Robert Dick Advanced Digital Logic

- Implication chart algorithm

- Onstruct implication chart, one square for each combination of states taken two at a time.

- **2** Square labeled  $S_i$ ,  $S_j$ , if outputs differ than square gets X (0). Otherwise write down implied state pairs for all input combinations.

- 3 Advance through chart top-to-bottom and left-to-right. If square  $S_i$ ,  $S_j$ contains next state pair  $S_m$ ,  $S_n$  and that pair labels a square already labeled X (0), then  $S_i$ ,  $S_j$  is labeled X.

- Ontinue executing Step 3 until no new squares are marked with X (0).

- **5** For each remaining unmarked square  $S_i$ ,  $S_j$ , then  $S_i$  and  $S_j$  are equivalent

|                  |     | state machines<br>state machines<br>Homework | Specific<br>State n<br>State a<br>Output | n <mark>inimiza</mark><br>ssignme |   |  |

|------------------|-----|----------------------------------------------|------------------------------------------|-----------------------------------|---|--|

| nplication chart | miı | nimizatic                                    | n                                        |                                   |   |  |

|                  |     |                                              |                                          |                                   |   |  |

|                  |     |                                              |                                          |                                   |   |  |

|                  | _   |                                              | ı                                        |                                   |   |  |

|                  | B   | BC, DE                                       |                                          |                                   |   |  |

|                  | С   | BD, DE                                       | CD                                       |                                   |   |  |

|                  | D   | 0                                            | 0                                        | 0                                 |   |  |

|                  | Е   | BD, DE                                       | CD                                       | 1                                 | 0 |  |

|                  |     | A                                            | В                                        | С                                 | D |  |

|                  |     | $D \neq any c$                               | ther s                                   | tate                              |   |  |

|                  |     |                                              |                                          |                                   |   |  |

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework | Specification<br>State minimization<br>State assignment<br>Output and state variable function synthesis |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| Minimization can be more complicated                                                              |                                                                                                         |  |

• Incompletely specified machines are difficult to minimize

Robert Dick

- Therefore, some merges can block others

- Need a formulation amenable to backtracking

|                | s    | s'          |              |

|----------------|------|-------------|--------------|

| s              | 0    | 1           | q            |

| A              | D    | В           | 0            |

| В              | X    | А           | Х            |

| C              | A    | A<br>X<br>C | 1            |

| D              | В    | С           | 1            |

| Consider mergi | ng A | and         | B or B and C |

Incompletely specified Moore state reduction

| 14 Robert Dick                                                                                    | Advanced Digital Logic Design                                                                                  |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                                                                   |                                                                                                                |

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework | Specification<br>State minimization<br><b>State assignment</b><br>Output and state variable function synthesis |

| State assignment                                                                                  |                                                                                                                |

|                                                                                                   |                                                                                                                |

• Keep state variable functions and output variable functions simple

• Allow cubes to be reused among different state variable functions

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework | Specification<br>State minimization<br>State assignment<br>Output and state variable function synthesis |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| State assignment is difficult                                                                     |                                                                                                         |

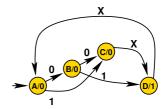

Therefore, we have

$$\frac{p!}{(p-p)!} = \frac{p!}{0!} = \frac{p!}{1} = \frac{p!}{1} = \frac{p!}{1}$$

possible assignments

$$p! \in \mathcal{O}(2^p)$$

$\bullet$   $\ldots$  and that's a loose bound

- State assignment has a huge solution space

- It's also a hard problem

• Assign values to states

- Allow the extraction of common cubes for different state variable functions

- State variables

State assignment

- States connected by transitions should be adjacent • Output functions

- States with equivalent outputs should be adjacent

- Heuristic assignment popular

- MUSTANG is popular

Attraction between states based on ability to extract common cubes

Robert Dick Advanced Digital Logic Des

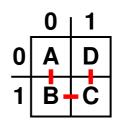

### State assignment State map • Recall that Karnaugh maps help us visualize adjacency Can do reasonably good state assignment by following guidelines. Make states have adjacent assignments (differing by only one bit) if: • Use state maps to visualize state adjacency • They have the same next (child) state in the state diagram for • Recall that we have *n* states, so we require $\lceil \lg_2(4) \rceil$ bit state the same input variables • $\lceil \lg_2(4) \rceil = 2$ • They have the same previous (parent) state in the state diagram • What if we hadn't done state minimization? $\bullet\,$ They have the same output for the same input $\bullet\,$ Five states $\rightarrow\,$ three state variable bits required Robert Dick A ed Digital Logic

| Finite s<br>inimization of incompletely-specified finite s | <b>tate machines</b><br>tate machines<br>Homework | State m<br>State a: | iinimization<br>ssignment | iable function | synthesis |  |

|------------------------------------------------------------|---------------------------------------------------|---------------------|---------------------------|----------------|-----------|--|

| tate map                                                   |                                                   |                     |                           |                |           |  |

| <u>0</u><br>1                                              | 00<br>A<br>B                                      | 01<br>C<br>D        | 11<br>E<br>F              | 10<br>G<br>H   |           |  |

- *a*, *b*, and *c* are state variable bits

- A, B, C, etc. are states

- State maps help select adjacent assignments for adjacent states

Robert Dick Advanced Digital Logic D

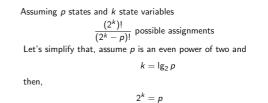

- States with same child for same input:  $\{B,C\}$

- States with same parent:  $\{B,C\},\{C,D\}$

- States with same output:  $\{A, B, C\}$

25

• Prioritize:  $\{B, C\}, \{C, D\}, \{A, B, C\},$  etc.

Specification

Specification

Specification

Minimization of incompletely specified finite state machines

Specification

Specification

Minimization

Minimization

State assignment

O(O(0 + 1) + 1) + 1(0 + 1)

Finite state machines Minimization of incompletely-specified finite state machines Homework State assignment Output and state variable function synthesis

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework | Specification<br>State minimization<br>State assignment<br>Output and state variable function synthesis |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Symbolic state state table                                                                        |                                                                                                         |

| current<br>state | ne<br>sta<br>i=0 | ext<br>ate<br>  i=1 | output ( <i>r</i> ) |

|------------------|------------------|---------------------|---------------------|

| А                | В                | С                   | 0                   |

| В                | C                | D                   | 0                   |

| С                | D                | D                   | 0                   |

| D                | A                | A                   | 1                   |

Robert Dick Advanced Digital Logic De

Finite state machines Minimization of incompletely-specified finite state machines Homework State assignment Output and state variable function synthesis

|   | rent<br>e ( <i>jk</i> ) |    | $ \substack{ (j^+k^+) \\ i=1 } $ | output ( <i>r</i> ) |

|---|-------------------------|----|----------------------------------|---------------------|

| 0 | 0                       | 01 | 11                               | 0                   |

| 0 | 1                       | 11 | 10                               | 0                   |

| 1 | 1                       | 10 | 10                               | 0                   |

| 1 | 0                       | 00 | 00                               | 1                   |

Robert Dick Advanced Digital Logic Design

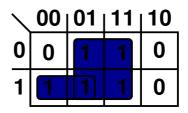

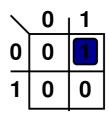

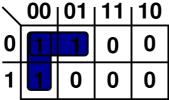

State variable and output simplification

- Use Karnaugh maps (or other methods) to simplify functions

- j<sup>+</sup>(j, k, i)

- k<sup>+</sup>(j, k, i)

- r(j, k)

State variable and output simplification

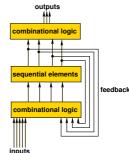

## Moore block diagram

### Finite state mac

### State minimization with Don't-Cares

- Can use advanced technique introduced in previous lecture

- Find the maximal compatibles

- Use these to generate the prime compatibles

- Write expression in POS form

- Multiply to get SOP form

- Formulate as a binate covering problem

- This technique is optimal but difficult

- State minimization for incompletely specified machines is a hard problem

Robert Dick Advanced Digital Logic D

| <b>\</b> | 00 + 01 | ī. |

|----------|---------|----|

State variable and output simplification

| Advanced Digital Logic Design                                                                           |

|---------------------------------------------------------------------------------------------------------|

|                                                                                                         |

| Specification<br>State minimization<br>State assignment<br>Output and state variable function synthesis |

|                                                                                                         |

|                                                                                                         |

- Implement the state variable functions in combinational logic

- Use sequential elements along feedback paths

- Implement the output variable functions in combinational logic

Mealy block diagram sequential elements feedback outputs 🛓 וה combinational logic inputs

| Finite state machines<br>Minimization of incompletely-specified finite state machines                                                                                                                                                                                                                                                      | Finite state machines<br>Minimization of incompletely-specified finite state machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Incompletely specified Moore state reduction                                                                                                                                                                                                                                                                                               | Maximal compatibles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                    | <ul> <li>Choosing the compatible state sets is not straight-forward</li> <li>Some combinations block potential future combinations</li> <li>Know conflicting states from the compatibility table</li> </ul>                                                                                                                                                                                                                                                                                                                                                |

| 39 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                               | 40 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework<br>Compatibles and implications                                                                                                                                                                                                          | Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework<br>Class sets                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B 1<br>C 0 1<br>D 0 0 AB<br>A B C {C, D}, {B, C}, {A, B}                                                                                                                                                                                                                                                                                   | <ul> <li>The combination of a pair of states may require the combination of another state pair</li> <li>Thus, using the maximal compatibles is insufficient</li> <li>Need additional prime compatibles that have smaller <i>class sets</i></li> <li>Starting from the maximal compatibles, which are primes, generate other primes</li> <li>In order of decreasing compatible size, if the compatible has a non-empty class set, enter all subsets that are not already contained in other prime compatibles with empty class sets in the table</li> </ul> |

| 41 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                               | 42 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework                                                                                                                                                                                                                                          | Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Prime compatibles                                                                                                                                                                                                                                                                                                                          | Prime compatible selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B       1       A, B         C       0       1       B, C         D       0       0       AB       C, D         A       B       C       D                                                                                                                                                                                                  | <ul> <li>Once the prime compatibles are known, it is necessary to select a subset that</li> <li>Has minimal number of selected prime compatibles</li> <li>Covers all states <ul> <li>Would be unate covering</li> </ul> </li> <li>Contains all class sets implied by the selected prime compatibles <ul> <li>This makes it binate covering</li> </ul> </li> <li>Recall unate covering, similar solution works <ul> <li>Branch and bound</li> </ul> </li> </ul>                                                                                             |

| 43 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                               | 44 Robert Dick Advanced Digital Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Knownee block     Anvances biggas coge breggi     Finite state machines     Homework     Binate covering                                                                                                                                                                                                                                   | Minimization of incompletely-specified finite state machines         Minimization         Minimization           Binate covering         Binate covering         Binate covering                                                                                                                                                                                                                                                                                                                                                                           |

| $\frac{\{C,D\} \rightarrow \{A,B\}}{\{C,D\} + \{A,B\}}$                                                                                                                                                                                                                                                                                    | $J_{1} = \{A, B\}$ $J_{2} = (\{A, B\} + \{B, C\})$ $J_{3} = (\{B, C\} + \{C, D\})$ $J_{4} = (\{C, D\} + \{D\})$ $J_{5} = (\overline{\{C, D\}} + \{A, B\})$ form prime compatible                                                                                                                                                                                                                                                                                                                                                                           |

| { <i>A</i> , <i>B</i> } need to include A<br>({ <i>A</i> , <i>B</i> } + { <i>B</i> , <i>C</i> }) need to include B<br>({ <i>B</i> , <i>C</i> } + { <i>C</i> , <i>D</i> }) need to include C<br>({ <i>C</i> , <i>D</i> } + { <i>D</i> }) need to include D<br>$\overline{({C, D} + {A, B})}$ { <i>C</i> , <i>D</i> } class set requirements | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Robert Dick Advanced Digital Logic De

| $\{A, B\}$                                                     | need to include A |

|----------------------------------------------------------------|-------------------|

| $({A,B} + {B,C})$                                              | need to include B |

| $(\{B, C\} + \{C, D\})$                                        | need to include C |

| $(\{C, D\} + \{D\})$                                           | need to include D |

| $(\overline{\{C,D\}} + \{A,B\})$ {C, D} class set requirements |                   |

Robert Dick Advanced Digital Logic D

| Homework                                                                                                                         | Finite state machines Minimization of incompletely-specified finite state machines Homework                                           |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| nate covering                                                                                                                    | Additional examples                                                                                                                   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                            | $ \begin{array}{cccc} CS & NS(I) & Out \\ \hline A & A & C & 0 \\ B & B & B & X \\ C & A & C & 1 \end{array} $                        |

|                                                                                                                                  | C A C 1                                                                                                                               |

| <ul> <li>Find a set of columns, S, such that, for every row</li> <li>A 1-column in the row is in S or</li> </ul>                 |                                                                                                                                       |

| <ul> <li>a 0-column in the row is not in S</li> </ul>                                                                            |                                                                                                                                       |

|                                                                                                                                  |                                                                                                                                       |

|                                                                                                                                  |                                                                                                                                       |

| Robert Dick Advanced Digital Logic Design                                                                                        | 48 Robert Dick Advanced Digital Logic Design                                                                                          |

| Robert Dick Advanced Digital Logic Design                                                                                        |                                                                                                                                       |

|                                                                                                                                  | 48 Robert Dick Advanced Digital Logic Design<br>Finite state machines<br>Minimization of incompletely-specified finite state machines |

| Robert Dick Advanced Digital Logic Design                                                                                        | Finite state machines<br>Minimization of incompletely-specified finite state machines                                                 |

| Robert Dick Advanced Digital Logic Design Finite state machines ization of incompletely-specified finite state machines Homework | Finite state machines<br>Minimization of incompletely-specified finite state machines<br>Homework                                     |

| Finite state machines<br>Minimization of incompletely-specified finite state machines<br><b>Homework</b> |  |

|----------------------------------------------------------------------------------------------------------|--|

| Recommended reading                                                                                      |  |

- http://www.deepchip.com/gadfly/gad040703.html

- http://www.deepchip.com/gadfly/gad042803.html

- Jayaram Bhasker. A VHDL Primer. Prentice-Hall, NJ, 1992

Robert Dick Ad

- Chapter 1

- Chapter 2

52

## Minimization of incompletely-specified finite state machines Homework Next lecture

• Design representations

53

$\bullet~\mbox{VHDL}$  for combinational and sequential systems

Robert Dick Adva