#### Advanced Digital Logic Design - EECS 303

http://ziyang.eecs.northwestern.edu/eecs303/

Teacher: Robert Dick Office: L477 Tech

Email: dickrp@northwestern.edu Phone: 847–467–2298

UNIVERSITY

# Administration Overview of course Homework Misc. Administration

- Lecture notes handed out before class

- PDF files posted after lectures

- http://ziyang.eecs.northwestern.edu/~dickrp/eecs303/

- If something isn't clear and you ask about it in class, I'll sometimes add more detail to the slides before posting

- EECS 347: Microprocessor System Projects

- EECS 357: Introduction to VLSI CAD

- EECS 361: Computer Architecture

- EECS 362: Computer Architecture Projects

- EECS 391: Introduction to VLSI Design

- EECS 392: VLSI Design Projects

- EECS 393: Design and Analysis of High-Speed Integrated Circuits

- Allen Dewey. Analysis and Design of Digital Systems With VHDL. PWS Publishing Company, International Thompson Publishing, 1997

- Zvi Kohavi. Switching and Finite Automata Theory. McGraw-Hill Book Company, NY, 1978

- A. V. Aho, R. Sethi, and J. D. Ullman. Compilers principles, techniques, and tools. Addison-Wesley, MA, 1986

- Randy H. Katz. Contemporary Logic Design. The Benjamin/Cummings Publishing Company, Inc., 1994

T 1. 2. . . . . .

#### Today's goals

- Know how to get access to the resources you'll need for this course

- Books, computer lab, website, newsgroup

- Understand work and grading policies

- 4 Have a rough understanding of the topics we will cover

- 1 Have a rough understanding of an example design

- You'll soon be designing similar systems on your own

- ECE 203: Introduction to Computer Engineering

- Need to have basic understanding of digital systems, logic gates, combinational logic, and sequential logic

- Need Unix experience (or need to catch up) since we will use the Mentor Graphics tools on Sun workstations

- Expect you to familiarize yourself with the basics of using this OS on your own but will give some hints

- Use search engine, e.g., google: "unix beginners"

- http://www.ee.surrey.ac.uk/Teaching/Unix/ not a bad place to start

M. Morris Mano and Charles R. Kime. Logic and Computer Design Fundamentals. Prentice-Hall, NJ, fourth edition, 2008

Homeworks: 25% of grade Labs: 25% of grade Midterm exam: 20% of grade Final exam: 30% of grade

- Homeworks and labs due at beginning of class on due date

- 5% penalty for handing after start of class but still on due date

- 10% penalty per late working day

- No credit if more than three working days late

Robert Dick Advanced Digital Logic Design 9 Robert Dick

#### **Administratio** Overview of cours Homewor Misc

#### Grading style

- Homeworks and some labs will be graded quite strictly

- Learn from the feedback

- See the TA or me if something doesn't make sense

- Don't assume a 75% grade on the homework implies a C in the course – it doesn't

- Will cover a limited amount material in lectures that does not appear in the course textbook

- However, you'll have access to the full set of lecture notes

- I will do my best not to make exams surprising

- $\bullet$  However, they won't be easy and the best students in the class probably won't get 100% on the exams

10 Robert Dick Advanced Digital Logic Design

Administration

Overview of counts

Homework

Lab work

- Computer aided-design (CAD) software from Mentor Graphics

- Sun workstations in the Wilkinson Lab (M338 Tech)

- Lab Hours: Open

- Topics

- Tutorial on Mentor Graphics (simple logic)

- Design of combinational logic

- Design of sequential logic

- Use of VHDL for combinational and sequential design

12 Robert Dick Advanced Digital Logic Design

Administration

Overview of management Homework

Homework

Misc.

Subscribe to mailing list

- Very useful for getting questions rapidly answered

- If you email an academic question to the TA or me, we will post the question and the answer to the newsgroup/mailing list but remove your name

- Send mail to "listserv@listserv.it.northwestern.edu"

- No subject

- Body of SUBSCRIBE ADLD [Firstname] [Lastname]

- Send mail to "adld@listserv.it.northwestern.edu" to post

- I will archive posts and make them available via the course web page

Administration

Overview of course

Homeory

Met.

Course topics in context II

- Heuristic logic minimization

- Complexity and algorithms

- Implementation technologies

- Useful starting point for prototyping designs

- Implementation technologies are constantly changing

- Graph definitions, critical path, and topological sort

- Basic understanding of graph algorithms

- Number systems, binary arithmetic (more detail, advanced operations)

Robert Dick Advanced Digital Logic Des

• Fundamental meaning of mathematical operations

Overview H

#### Lab assignments

#### Tried to make lab assignments get to the point w.o. wasting time

- In this area, lab assignments necessarily require some time

- May take you much longer than some other students if you need to refresh your memory or fill in gaps in your background

- You probably will not be able to finish labs on time if you start them the day before they're due

Advanced Digital Logic Design

# We can reschedule office hours based on your comments Person Day Time Room Robert Dick Tuesday 5:00-6:00 L477 Tech Robert Dick Thursday 5:00-6:00 L477 Tech

We'll go to the Wilkinson Lab (M338 Tech) when requested.

- Boolean algebra (brief review)

- Formulating problems as Boolean expressions

- Can use to solve problems in many fields of engineering

- Karnaugh maps (brief review)

- Helps visualize problem in which adjacency is important

- Quine–McCluskey (fairly quick coverage, depending on background)

- Covering

- Technology mapping

- Covering

- FSM design, non-deterministic intermediate representations

- Compiler, languages, CS theory

- Incompletely specified FSM state minimization

- Covering

- CAD software

- $\bullet$  Testing ideas in other fields, e.g., computer architecture

- Testing (if time permits)

n 19 Robert Dick Advanced Digital Logic Design

- Learn to manually design, optimize, and implement small digital combinational circuits.

- Have a basic understanding of the building blocks and implementation technologies available to digital designers.

- Understand how to use schematic capture software to design digital circuits.

- Be capable of doing automatic and manual timing analysis of combinational circuits.

- Be capable of using CAD software to automatically optimize large digital combinational circuits and map them to a target technology.

- Understand the differences between synchronous and asynchronous finite state machines and know the advantages of each.

- Be capable of doing simple VHDL designs.

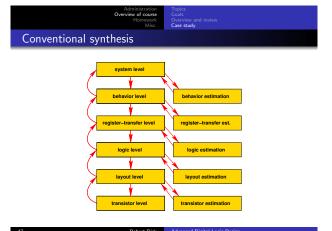

- Start from single system-level description

- Automatically build all hardware

- Where do we start?

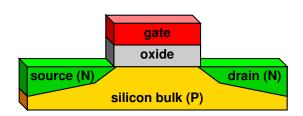

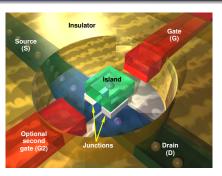

- Metal Oxide Silicon

- Positive and negative carriers

- Complimentary MOS

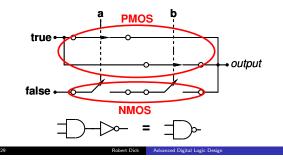

- PMOS gates are like normally closed switches that are good at transmitting only true (high) signals

- NMOS gates are like normally open switches that are good at transmitting only false (low) signals

- Have a high-level understanding of the algorithms such synthesis software uses (e.g., logic optimization and technology mapping). This first portion of the course was dedicated to combinational design. I went into depth on a few more advanced topics because I wanted you to see some of the beauty of the algorithms used to automatically design circuits, e.g., my description of portions of the Espresso algorithm.

- Understand how to design, optimize, and implement finite state machines.

- Understand that sequential behavior can be specified in different ways and have a reasonably good understanding of how to start from a few different types of specifications and end up with working logic.

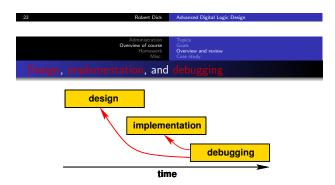

- Fault isolation: Design flaws, implementation flaws, component flaws

- Hypothesis formation and testing

- Good design and implementation make debugging easier

- 4–5 hours  $\rightarrow$  12–14 hours

Therefore, NAND and NOR gates are used in CMOS design instead of AND and OR gates

Administration

r course

Goals

mework

Overview and review

Misc.

Case study

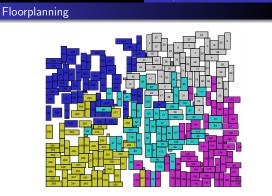

### New technologies

2 Robert Dick Advanced Digital Logic Design

Administration **Overview of course** Homework Misc.

Goals

Overview and review

Case study

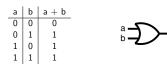

AND

| _ |

|---|

|   |

| _ |

|   |

|   |

$\mathsf{a}\; \mathit{AND}\; \mathsf{b} = \mathsf{a} \; \land \; \mathsf{b} = \mathsf{a}\; \mathsf{b}$

34 Robert Dick Advanced Digital Logic Design

Administration

Overview of course

HOmework

Misc.

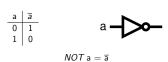

NOT

Administration

Overview of course

Goals

Goals

Case study

Case study

1 Robert Dick Advanced Digital Logic Design

Administration **Overview of course** Homework Misc.

Overview and revie Case study

Review: Boolean algebra

- ullet The only values are 0 (or false) and 1 (or true)

- $\bullet \ \, {\sf One} \ \, {\sf can} \ \, {\sf define} \ \, {\sf operations/functions/gates} \\$

- Boolean values as input and output

- A truth table enumerates output values for all input value combinations

$\mathsf{a}\,\, \mathit{OR}\,\, \mathsf{b} = \mathsf{a}\, \vee\, \mathsf{b} = \mathsf{a}\, +\, \mathsf{b}$

Advanced Digital Logic Design

Advanced Digital Logic Design

Advanced Digital Logic Design

Topics

Overview of course Homeoork

Misc.

Case study of simple combinational logic design —

seven-segment display

- Given: A four-bit binary input

- Display a decimal digit ranging from zero to nine

- Use a seven-segment display

8 Robert Dick A

# Case study – seven-segment display

| iз | i <sub>2</sub> | i <sub>1</sub> | i <sub>0</sub> | dec |

|----|----------------|----------------|----------------|-----|

| 0  | 0              | 0              | 0              | 0   |

| 0  | 0              | 0              | 1              | 1   |

| 0  | 0              | 1              | 0              | 2   |

| 0  | 0              | 1              | 1              | 3   |

| 0  | 1              | 0              | 0              | 4   |

| 0  | 1              | 0              | 1              | 5   |

| 0  | 1              | 1              | 0              | 6   |

| 0  | 1              | 1              | 1              | 7   |

| 1  | 0              | 0              | 0              | 8   |

| 1  | 0              | 0              | 1              | 9   |

| iз | i <sub>2</sub> | $i_1$ | i <sub>0</sub> | dec |

|----|----------------|-------|----------------|-----|

| 0  | 0              | 0     | 0              | 0   |

| 0  | 0              | 0     | 1              | 1   |

| 0  | 0              | 1     | 0              | 2   |

| 0  | 0              | 1     | 1              |     |

| 0  | 1              | 0     | 0              | 4   |

| 0  | 1              | 0     | 1              | 5   |

| 0  | 1              | 1     | 0              | 6   |

| 0  | 1              | 1     | 1              | 7   |

| 1  | 0              | 0     | 0              | 8   |

| 1  | 0              | 0     | 1              | 9   |

| 39           | Robert Dick                                      | Advanced Digital Logic Design                        |

|--------------|--------------------------------------------------|------------------------------------------------------|

|              |                                                  |                                                      |

|              | Administration Overview of course Homework Misc. | Topics<br>Goals<br>Overview and review<br>Case study |

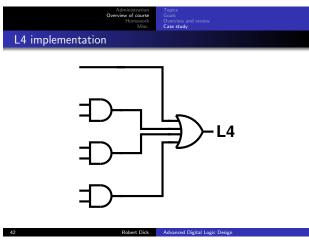

| Implement L4 |                                                  |                                                      |

| i3 | i <sub>2</sub> | i <sub>1</sub> | i <sub>0</sub> | dec | L4 |

|----|----------------|----------------|----------------|-----|----|

| 0  | 0              | 0              | 0              | 0   | 1  |

| 0  | 0              | 0              | 1              | 1   | 0  |

| 0  | 0              | 1              | 0              | 2   | 0  |

| 0  | 0              | 1              | 1              | 3   | 0  |

| 0  | 1              | 0              | 0              | 4   | 1  |

| 0  | 1              | 0              | 1              | 5   | 1  |

| 0  | 1              | 1              | 0              | 6   | 1  |

| 0  | 1              | 1              | 1              | 7   | 0  |

| 1  | 0              | 0              | 0              | 8   | 1  |

| 1  | 0              | 0              | 1              | 9   | 1  |

- No feedback between inputs and outputs combinational

- Outputs a function of the current inputs, only

- Feedback sequential

- Finite state machine design

- Logic minimization

- Implementation with gates

- Need a lot more depth, and a lot more detail!

| iş | 3 i | <sub>2</sub> i | 1 | i <sub>0</sub> | dec | L1 | L2 | L3 | L4 | L5 | L6 | L7 |

|----|-----|----------------|---|----------------|-----|----|----|----|----|----|----|----|

| 0  | ) ( | ) (            | ) | 0              | 0   | 1  | 0  | 1  | 1  | 1  | 1  | 1  |

| 0  | ) ( | ) (            | ) | 1              | 1   | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 0  | ) ( | ) :            | 1 | 0              | 2   | 1  | 1  | 1  | 0  | 1  | 1  | 0  |

| 0  | ) ( | ) :            | 1 | 1              | 3   | 1  | 1  | 1  | 0  | 0  | 1  | 1  |

| 0  | ) ] | L (            | ) | 0              | 4   | 0  | 1  | 0  | 1  | 0  | 1  | 1  |

| 0  | ) ] | L (            | ) | 1              | 5   | 1  | 1  | 1  | 1  | 0  | 0  | 1  |

| 0  | ) ] | L :            | 1 | 0              | 6   | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| 0  | ) ] | L :            | 1 | 1              | 7   | 1  | 0  | 0  | 0  | 0  | 1  | 1  |

| 1  | . ( | ) (            | ) | 0              | 8   | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1  | . ( | ) (            | ) | 1              | 9   | 1  | 1  | 0  | 1  | 0  | 1  | 1  |

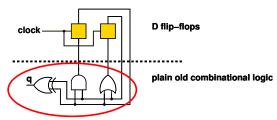

- Sequential logic

- Outputs depend on current state and (maybe) current inputs

- Next state depends on current state and input

- For implementable machines, there are a finite number of states

- Synchronous

- State changes upon clock event (transition) occurs

- Asynchronous

- State changes upon inputs change, subject to circuit delays

- Start from single system-level description

- Automatically build all hardware

- Where do we start?

- What are the fundamental barriers?

- What new discoveries are necessary?

Administration

Overview of course

Homework

Homework

Misc.

Combinational design

- Let's start by reviewing combinational design

- A lot of amazing stuff will build upon this later

Administration

Overview of Market

Homework

Market

Introductory reading assignments

- In general, reading assignments will cover material that will be presented in the next class.

- It may seem like a lot but most should be review from EECS 203.

- Even if you think you remember the material from EECS 203, spend a few minutes with the book to confirm.

- M. Morris Mano and Charles R. Kime. *Logic and Computer Design Fundamentals*. Prentice-Hall, NJ, fourth edition, 2008

- Chapters 2, 3, and 4

Administration

Overview of course

Homeoork

Misc.

Status and approach

Topics

Goals

Goals

Case study

- Understand a few combinational logic design techniques

- Much left to learn

- · Have scratched the surface of sequential logic design

- Much left to learn

- Little knowledge of automation and its fundamental barriers

- Approach: Start from the core we learned in EECS 203

- Build breadth and depth

- Confirm that you are registered for the course at http://courses.northwestern.edu/

- The administrators have a list of students.

- They will create accounts and add physical access to M334 to your card.

- RLE

- $\hbox{ \begin{tabular}{l} {\bf c} Compression geek culture: compression = prediction = classification \end{tabular} }$