# Advanced Digital Logic Design – EECS 303

http://ziyang.eecs.northwestern.edu/eecs303/

Teacher:Robert DickOffice:L477 TechEmail:dickrp@northwestern.eduPhone:847-467-2298

NORTHWESTERN UNIVERSITY

Overview Number systems Adders

# Outline

- 1. Addition and subtraction

- 2. Multiplication

- 3. Homework

Overview Number systems Adders

### Section outline

### 1. Addition and subtraction Overview Number systems Adders

Overview Number systems Adders

# Arithmetic/logic operations

- Increment

- Addition

- Negation

- Subtraction

- Multiplication

- Slow or large

- Division

- Slow or large

Overview Number systems Adders

# Arithmetic/logic operations

- Shift left

- Fast, multiplication by two

- Shift right

- Fast, division by two

- Bit-wise operations

- AND, OR, NOT, NAND, NOR, XOR, and XNOR

Overview Number systems Adders

# Arithmetic

- Number systems review

- Adders

- Multipliers

- Memory overview

Overview Number systems Adders

### Arithmetic circuits

- Administration

- Number systems

- Adders

- Ripple carry

- Carry lookahead

- Carry select

Overview Number systems Adders

### Section outline

### 1. Addition and subtraction

Overview Number systems Adders

Overview Number systems Adders

### Number systems

- Representation of positive numbers same in most systems

- A few special-purpose alternatives exist, e.g., Gray code

- Alternatives exist for signed numbers

Overview Number systems Adders

### Standard unsigned binary numbers

Given an *n*-bit number in which  $d_i$  is the *i*th digit, the number is  $\sum_{i=1}^{n} 2^{i-1} d_i$

Overview Number systems Adders

# Unsigned addition

#### Consider adding 9 (1001) and 3 (0011)

Overview Number systems Adders

# Unsigned addition

#### Consider adding 9 (1001) and 3 (0011) 1 1 0 + 00

Overview Number systems Adders

### Unsigned addition

#### Consider adding 9 (1001) and 3 (0011) 1 1 1 0 0 1 + 0 0 1 10 0

Overview Number systems Adders

### Unsigned addition

#### Consider adding 9 (1001) and 3 (0011) 1 1 1 0 0 1 + 0 0 1 11 0 0

Overview Number systems Adders

### Unsigned addition

#### Consider adding 9 (1001) and 3 (0011) 1 1 1 0 0 1 + 0 0 1 11 1 0 0

Overview Number systems Adders

### Unsigned addition

#### Consider adding 9 (1001) and 3 (0011) $1 \quad 1$ $1 \quad 0 \quad 0 \quad 1$ $+ \quad 0 \quad 0 \quad 1 \quad 1$ $1 \quad 1 \quad 0 \quad 0$ Why an extra column?

Robert Dick Advanced Digital Logic Design

Overview Number systems Adders

# Overflow

- If the result of an operation can't be represented in the available number of bits, an *overflow* occurs

- E.g., 0110 + 1011 = 10001

- Need to detect overflow

Overview Number systems Adders

# Overflow

- If the result of an operation can't be represented in the available number of bits, an *overflow* occurs

- E.g., 0110 + 1011 = 10001

- Need to detect overflow

Overview Number systems Adders

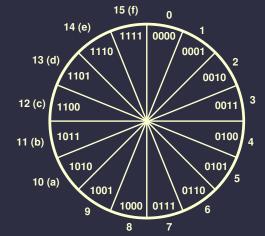

### Gray code

Overview Number systems Adders

# Gray code

- To convert from a standard binary number to a Gray code number XOR the number by it's half (right-shift it)

- To convert from a Gray code number to a standard binary number, XOR each binary digit with the parity of the higher digits

Given that a number contains *n* digits and each digit,  $d_i$ , contributes  $2^{i-1}$  to the number

$$\mathcal{P}_j^k = d_j \oplus d_{j+1} \cdots \oplus d_{k-1} \oplus d_k$$

$d_i = d_i \oplus \mathcal{P}_{i+1}^n$

Overview Number systems Adders

# Gray code

- Converting from Gray code to standard binary is difficult

- Take time approximately proportional to n

- Doing standard arithmetic operations using Gray coded numbers is difficult

- Generally slower than using standard binary representation

- E.g., addition requires two carries

- Why use Gray coded numbers?

- Analog to digital conversion

- Reduced bus switching activity

Overview Number systems Adders

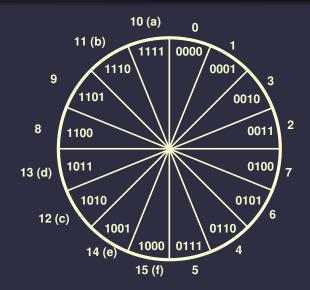

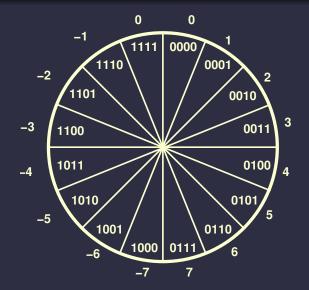

### Signed number systems

- Three major schemes

- Sign and magnitude

- One's complement

- Two's complement

Overview Number systems Adders

### Number system assumptions

- Four-bit machine word

- 16 values can be represented

- Approximately half are positive

- Approximately half are negative

Overview Number systems Adders

- *d<sub>n</sub>* represents sign

- 0 is positive, 1 is negative

- Two representations for zero

- What is the range for such numbers?

- *d<sub>n</sub>* represents sign

- 0 is positive, 1 is negative

- Two representations for zero

- What is the range for such numbers?

- Range:  $[-2^{n-1}+1, 2^{n-1}-1]$

- How is addition done?

- If both numbers have the same sign, add them like unsigned numbers and preserve sign

- If numbers have differing signs, subtract smaller magnitude from larger magnitude and use sign of large magnitude number

- Consider 5 + -6

- Note that signs differ

- $\bullet\,$  Use magnitude comparison to determine large magnitude: 6-5

- Subtract smaller magnitude from larger magnitude: 1

- Use sign of large magnitude number: -1

Overview Number systems Adders

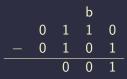

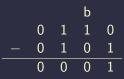

### Direct subtraction

#### Consider subtracting 5 (0101) from 6 (0110)

- Note that this operation is different from addition

- Sign and magnitude addition is complicated

Overview Number systems Adders

### Direct subtraction

$$\begin{array}{cccccccc} & & b & \\ & 0 & 1 & 1 & 0 \\ - & 0 & 1 & 0 & 1 \\ \hline & & & & 1 \end{array}$$

- Note that this operation is different from addition

- Sign and magnitude addition is complicated

Overview Number systems Adders

### Direct subtraction

$$\begin{array}{ccccccc} & & b & \\ & 0 & 1 & 1 & 0 \\ - & 0 & 1 & 0 & 1 \\ & & & 0 & 1 \end{array}$$

- Note that this operation is different from addition

- Sign and magnitude addition is complicated

Overview Number systems Adders

### Direct subtraction

- Note that this operation is different from addition

- Sign and magnitude addition is complicated

Overview Number systems Adders

### Direct subtraction

- Note that this operation is different from addition

- Sign and magnitude addition is complicated

Overview Number systems Adders

### One's compliment

# One's compliment

- If negative, complement all bits

- Addition somewhat simplified

- Do standard addition except wrap around carry back to the 0th bit

- Potentially requires two additions of the whole width

- Slow

Overview Number systems Adders

### One's complement addition

#### Consider adding -5 (1010) and 7 (0111)

Overview Number systems Adders

## One's complement addition

Overview Number systems Adders

## One's complement addition

Overview Number systems Adders

## One's complement addition

$$egin{array}{ccccccccc} 1 & 1 & & & \ 1 & 0 & 1 & 0 & \ + & 0 & 1 & 1 & 1 & \ & & 0 & 0 & 1 & \end{array}$$

Overview Number systems Adders

## One's complement addition

Overview Number systems Adders

## One's complement addition

|   | 1 | 1 |   |   |

|---|---|---|---|---|

|   | 1 | 0 | 1 | 0 |

| + | 0 |   |   |   |

|   | 0 | 0 | 0 | 0 |

Overview Number systems Adders

## One's complement addition

|   | 1 | 1 |   |   |

|---|---|---|---|---|

|   | 1 | 0 | 1 | 0 |

| + | 0 |   |   |   |

|   | 0 | 0 | 1 | 0 |

Overview Number systems Adders

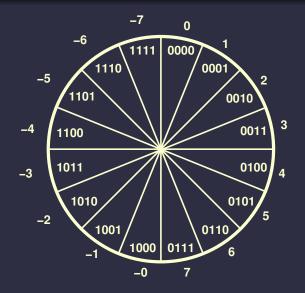

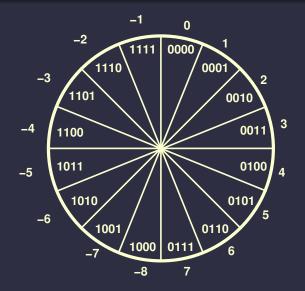

- To negate a number, invert all its bits and add 1

- · Like one's complement, however, rotated by one bit

- Counter-intuitive

- However, has some excellent properties

Overview Number systems Adders

Overview Number systems Adders

- Only one zero

- Leads to more natural comparisons

- One more negative than positive number

- This difference is irrelevant as *n* increases

- Substantial advantage Addition is easy!

Overview Number systems Adders

## Two's complement addition

$$egin{array}{ccccccccc} 1 & & & & & \ 1 & 1 & 0 & 0 & \ + & 0 & 1 & 1 & 0 & \ & & 0 & 1 & 0 & \ \end{array}$$

Overview Number systems Adders

## Two's complement addition

Overview Number systems Adders

- No looped carry Only one addition necessary

- If carry-in to most-significant bit ≠ carry-out to most-significant bit, overflow occurs

- What does this represent?

- Both operands positive and have carry-in to sign bit

- Both operands negative and don't have carry-in to sign bit

Overview Number systems Adders

# Two's complement overflow

| а | b | cin | cout |

|---|---|-----|------|

| 0 | 0 | 0   | 0    |

| 0 | 0 | 1   | 0    |

| 0 | 1 | 0   | 0    |

| 0 | 1 | 1   | 1    |

| 1 | 0 | 0   | 0    |

| 1 | 0 | 1   | 1    |

| 1 | 1 | 0   | 1    |

| 1 | 1 | 1   | 1    |

Overview Number systems Adders

# Two's complement overflow

| а | b | cin | cout |

|---|---|-----|------|

| 0 | 0 | 0   | 0    |

| 0 | 0 |     | 0    |

| 0 | 1 | 0   | 0    |

| 0 | 1 | 1   | 1    |

| 1 | 0 | 0   | 0    |

| 1 | 0 | 1   | 1    |

| 1 | 1 | 0   | 1    |

| 1 | 1 | 1   | 1    |

Overview Number systems Adders

# Section outline

#### 1. Addition and subtraction

Overview Number systems Adders

Overview Number systems Adders

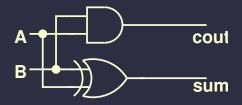

### Half adder review

#### For two's complement, don't need subtracter А В cout sum 0 0 0 0 0 1 1 0 1 1 0 0 1 1 1 0 cout = AB $sum = A \oplus B$

Overview Number systems Adders

# Half adder review

Overview Number systems Adders

# Full adder review

| Need to deal with carry-in |   |     |      |     |

|----------------------------|---|-----|------|-----|

| А                          | В | cin | cout | sum |

| 0                          | 0 | 0   | 0    | 0   |

| 0                          | 0 | 1   | 0    | 1   |

| 0                          | 1 | 0   | 0    | 1   |

| 0                          | 1 | 1   | 1    | 0   |

| 1                          | 0 | 0   | 0    | 1   |

| 1                          | 0 | 1   | 1    | 0   |

| 1                          | 1 | 0   | 1    | 0   |

| 1                          | 1 | 1   | 1    | 1   |

Overview Number systems Adders

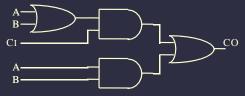

# Full adder

$sum = A \oplus B \oplus cin$ cout = AB + A ci + B ci

Overview Number systems Adders

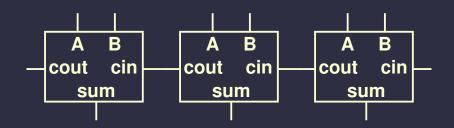

# Cascaded full-adders

Overview Number systems Adders

# Full adder standard implementation

Six logic gates

Overview Number systems Adders

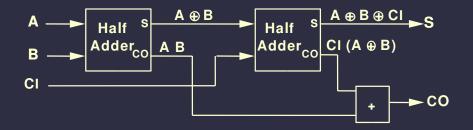

## Full adder composed of half-adders

$AB + ci(A \oplus B) = AB + B ci + A ci$

Overview Number systems Adders

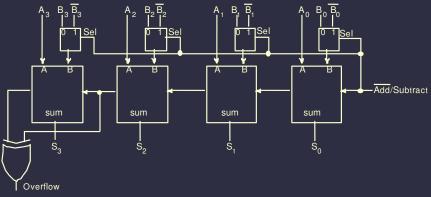

### Adder/subtracter

#### Consider input to cin

Overview Number systems Adders

# Ripple-carry delay analysis

- The critical path (to *cout*) is two gate delays per stage

- Consider adding two 32-bit numbers

- 64 gate delays

- Too slow!

- Consider faster alternatives

Overview Number systems Adders

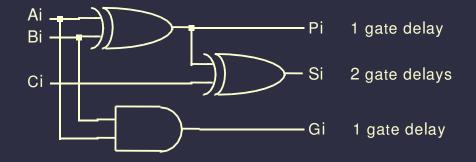

# Carry lookahead adder

- Carry generate: G = AB

- Carry propagate:  $P = A \oplus B$

- Represent sum and cout in terms of G and P

Overview Number systems Adders

# Carry lookahead adder

$$\mathsf{Sum} = \mathsf{A} \oplus \mathsf{B} \oplus \mathsf{cin}$$

=  $\mathsf{P} \oplus \mathsf{cin}$

$$cout = AB + A cin + B cin$$

$= AB + cin(A + B)$

$= AB + cin(A \oplus B)$

$= G + cin P$

Overview Number systems Adders

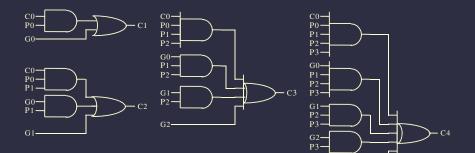

# Carry lookahead adder

#### Flatten carry equations

$$\begin{aligned} cin_1 &= G_0 + P_0 \ cin_0 \\ cin_2 &= G_1 + P_1 \ cin_1 = G_1 + P_1G_0 + P_1P_0 \ cin_0 \\ cin_3 &= G_2 + P_2 \ cin_2 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0 \ cin_0 \\ cin_4 &= G_3 + P_3C_3 = G_3 + P_3G_2 + P_3P_2G_1 + \\ P_3P_2P_1G_0 + P_3P_2P_1P_0 \ cin_0 \\ \text{Each } cin \text{ can be implemented in three-level logic} \end{aligned}$$

Overview Number systems Adders

# Carry lookahead building block

Overview Number systems Adders

# Carry lookahead adder

G3-

Overview Number systems Adders

# Carry lookahead delay analysis

- Assume a 4-stage adder with CLA

- Propagate and generate signals available after 1 gate delays

- Carry signals for slices 1 to 4 available after 3 gate delays

- Sum signal for slices 1 to 4 after 4 gate delays

Overview Number systems Adders

# Carry lookahead

- No carry chain slowing down computation of most-significant bit

- Computation in parallel

- More area required

- Each bit has more complicated logic than the last

- Therefore, limited bit width for this type of adder

- Can chain multiple carry lookahead adders to do wide additions

- Note that even this chain can be accelerated with lookahead

- Use internal and external carry lookahead units

Overview Number systems Adders

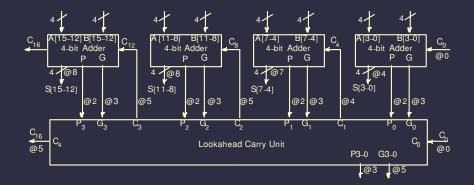

## Cascaded carry lookahead adder

Overview Number systems Adders

Delay analysis for cascaded carry lookahead

- Four-stage 16-bit adder

- cin for MSB available after five gate delays

- sum for MSB available after eight gate delays

- 16-bit ripple-carry adder takes 32 gate delays

- Note that not all gate delays are equivalent

- Depends on wiring, driven load

- However, carry lookahead is usually much faster than ripple-carry

Overview Number systems Adders

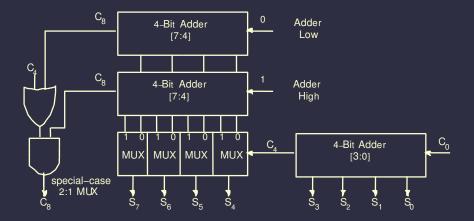

### Carry select adders

- Trade even more hardware for faster carry propagation

- Break a ripple carry adder into two chunks, low and high

- Implement two high versions

- *high*<sub>0</sub> computes the result if the carry-out from *low* is 0

- *high*<sub>1</sub> computes the result if the carry-out from *low* is 1

- Use a MUX to select a result once the carry-out of *low* is known

- high<sub>0</sub>'s cout is never greater than high<sub>1</sub>'s cout so special-case MUX can be used

Overview Number systems Adders

#### Carry select adder

Overview Number systems Adders

Delay analysis of carry select adder

- Consider 8-bit adder divided into 4-bit stages

- Each 4-bit stage uses carry lookahead

- The 2:1 MUX adds two gate delays

- 8-bit sum computed after 6 gate delays

- 7 gate delays for carry lookahead

- 16 gate delays for ripple carry

# Outline

- 1. Addition and subtraction

- 2. Multiplication

- 3. Homework

#### Arithmetic operations

- Digital logic circuits frequently need to carry out arithmetic operations

- Addition, subtraction, and multiplication

- A number of design decisions affect the performance, area, and power consumption of arithmetic sub-circuits

- Number systems

- Trade-off between area/power consumption and speed

# Multiplication

- To understand why these trade-offs exist, we need to understand the fundamentals of arithmetic circuits

- We have already discussed the selection of number systems and the design of adders/subtracters

- Similar alternatives exist for multipliers

# Multiplication

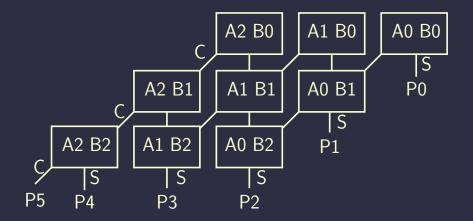

- Multiplication is the repeated application addition of ANDed bits and shifting (multiplying by two)

- Multiplication is the sum of the products of each bit of one operand with the other operand

- Consequence: A product has double the width of its operands

### Multiplication

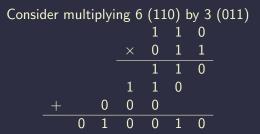

Recall that multiplying a number by two shifts it to the left one bit  $6 \cdot 3 = 6 \cdot (2^2 \cdot 0 + 2^1 \cdot 1 + 2^0 \cdot 1)$   $= 6 \cdot 2^2 \cdot 0 + 6 \cdot 2^1 \cdot 1 + 6 \cdot 2^0 \cdot 1$   $110 \cdot 011 = 11000 \cdot 0 + 1100 \cdot 1 + 110 \cdot 1$  = 110 + 1100 = 10010 = 18

# Multiplication

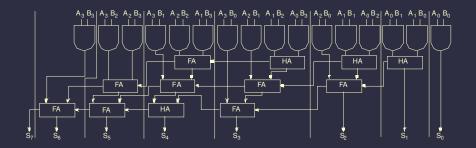

|   |                  |                  |                  | $A_2$            | $A_1$            | $A_0$            |

|---|------------------|------------------|------------------|------------------|------------------|------------------|

|   |                  |                  | ×                | $B_2$            | $B_1$            | $B_0$            |

|   |                  |                  |                  | $A_2B_0$         | $A_1B_0$         | $A_0B_0$         |

|   |                  |                  | $A_2B_1$         | $A_1B_1$         | $A_0B_1$         |                  |

| + |                  | $A_2B_2$         | $A_1B_2$         | $A_0B_2$         |                  |                  |

|   | sum <sub>5</sub> | sum <sub>4</sub> | sum <sub>3</sub> | sum <sub>2</sub> | sum <sub>1</sub> | sum <sub>0</sub> |

### Multiplication

# Multiplier implementation

- Direct implementation of this scheme possible

- Partial products formed with ANDs

- For four bits, 12 adders and 16 gates to form the partial products

- 88 gates

- Note that the maximum height (number of added bits) is equal to the operand width

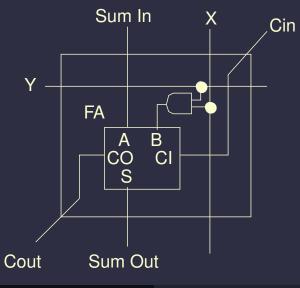

### Combinational multiplier

### Multiplier building block

Robert Dick Advanced Digital Logic Design

# Combinational multiplier

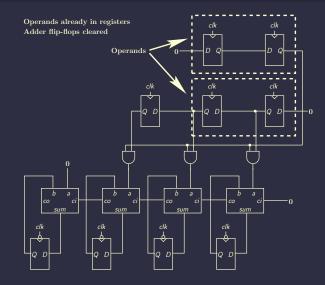

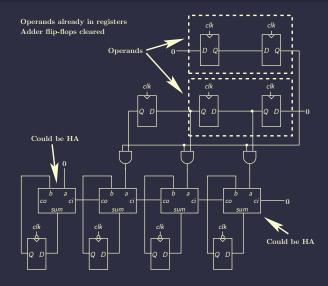

### Sequential multiplier

- Can iteratively one row of adders to carry out multiplications

- Advantage: Area reduced to approximately its square root

- Disadvantage: Takes *n* clock cycles, where *n* is the operand bit width

### 2X2 sequential multiplier

Robert Dick Advanced Digital Logic Design

### 2X2 sequential multiplier

Robert Dick Advanced Digital Logic Design

### Arithmetic/logic units

- Possible to implement functional units that can carry out many arithmetic and logic operations with little additional area or delay overhead

- Already saw example: Combined adder/subtracter

- Other operations possible

- Could you generalize the approach used for two's compliment addition and subtraction to another pair of operations?

# Arithmetic/logic operations

- Increment

- Addition

- Negation

- Subtraction

- Multiplication

- Slow or large

- Division

- Slow or large

Arithmetic/logic operations

- Shift left

- Fast, multiplication by two

- Shift right

- Fast, division by two

- Bit-wise operations

- AND, OR, NOT, NAND, NOR, XOR, and XNOR

### Memory types

- ROM, PROM, EPROM, EEPROM: Already know these

- SRAM: Fast, low-density, relies on feedback

- DRAM: Fast, high-density, requires refresh, relies on stored charge

- Flash: Already know these Non-volatile, slow, relies on floating gate

# Outline

- 1. Addition and subtraction

- 2. Multiplication

- 3. Homework

### Recommended reading

- M. Morris Mano and Charles R. Kime. Logic and Computer Design Fundamentals. Prentice-Hall, NJ, third edition, 2004

- Chapter 9