|             |                                                                                          |                                                                                                                                                                                                           | Grading scheme                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Email: dick | 7 Tech C<br>«rp@northwestern.edu P<br>4672298 E<br>T<br>C<br>P                           | A: Neal Oza<br>Diffice: Tech. Inst. L375<br>Thone: 847-467-0033<br>mail: nealoza@u.northwestern.edu<br>T: David Bild<br>Diffice: Tech. Inst. L470<br>Thone: 847-491-2083<br>mail: d-bild@northwestern.edu | <ul> <li>15% homeworks</li> <li>35% labs</li> <li>20% midterm exam</li> <li>30% final exam</li> </ul>                                       |

|             | NORTHWE                                                                                  |                                                                                                                                                                                                           |                                                                                                                                             |

| ned schedı  | Administrative Stuff<br>Review<br>Switch Models<br>ansistors and CMOS Design<br>Homework |                                                                                                                                                                                                           | 3 R. Dick Introduction to Computer Engineering EECS 203 Administrative Stuff Review Switch Models Transistors and CMO Beign Homework Review |

- Mondays: Labs assigned and collected

- Wednesdays: Homeworks collected and assigned

- Friday's class will normally focus on the lab and homework of the week, and will be given by Neal Oza

- What is a truth table?

- Combinational vs. sequential logic?

- Symbol and notation for AND, OR, NOT?

- Other gates also exist, e.g., NAND, NOR, XOR, XNOR

| 4 R. Dick                                                                                                         | Introduction to Computer Engineering – EECS 203 |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Administrative Stuff<br><b>Review</b><br>Transistors and (MOS Design<br>Homework                                  |                                                 |

| Case study of simple combin<br>Seven-segment display                                                              | ational logic design                            |

| <ul> <li>Given: A four-bit binary input</li> <li>Display a decimal digit<br/>ranging from zero to nine</li> </ul> | L1<br>L4 L6<br>L2                               |

| <ul> <li>Use a seven-segment display</li> </ul>                                                                   | 15 17                                           |

L3

ing – EECS :

| Transistors a      | and CMC | Revie<br>h Mod | els<br>gn |                |     |

|--------------------|---------|----------------|-----------|----------------|-----|

| Case study – Seven | -seg    | gme            | nt        |                |     |

|                    |         |                |           |                |     |

|                    | i3      | i <sub>2</sub> | $i_1$     | i <sub>0</sub> | dec |

|                    | 0       | 0              | 0         | 0              | 0   |

|                    | 0       | 0              | 0         | 1              | 1   |

|                    | 0       | 0              | 1         | 0              | 2   |

|                    | 0       | 0              | 1         | 1              | 3   |

|                    | 0       | 1              | 0         | 0              | 4   |

|                    | 0       | 1              | 0         | 1              | 5   |

|                    | 0       | 1              | 1         | 0              | 6   |

|                    | 0       | 1              | 1         | 1              | 7   |

|                    | 1       | 0              | 0         | 0              | 8   |

|                    | 1       | 0              | 0         | 1              | 9   |

|                    |         |                |           |                |     |

| Administrative Stuff<br><b>Review</b><br>Switch Models<br>Transistors and CMOS Design<br>Homework |                |                |       |                |     |    |    |    |

|---------------------------------------------------------------------------------------------------|----------------|----------------|-------|----------------|-----|----|----|----|

| Case study – Seven-segment                                                                        |                |                |       |                |     |    |    |    |

|                                                                                                   |                |                |       |                |     |    |    |    |

|                                                                                                   | i <sub>3</sub> | i <sub>2</sub> | $i_1$ | i <sub>0</sub> | dec | L1 | L2 | L3 |

|                                                                                                   | 0              | 0              | 0     | 0              | 0   | 1  | 0  | 1  |

| L4 L6                                                                                             | 0              | 0              | 0     | 1              | 1   | 0  | 0  | 0  |

|                                                                                                   | 0              | 0              | 1     | 0              | 2   | 1  | 1  | 1  |

|                                                                                                   | 0              | 0              | 1     | 1              | 3   | 1  | 1  | 1  |

| L2                                                                                                | 0              | 1              | 0     | 0              | 4   | 0  | 1  | 0  |

|                                                                                                   | 0              | 1              | 0     | 1              | 5   | 1  | 1  | 1  |

|                                                                                                   | 0              | 1              | 1     | 0              | 6   | 1  | 1  | 1  |

| L5 L7                                                                                             | 0              | 1              | 1     | 1              | 7   | 1  | 0  | 0  |

|                                                                                                   | 1              | 0              | 0     | 0              | 8   | 1  | 1  | 1  |

|                                                                                                   | 1              | 0              | 0     | 1              | 9   | 1  | 1  | 0  |

R. Dick Introduction to Computer Engineering – EECS 203

R. Dick Introduction to Computer Engine

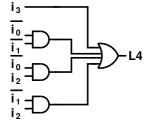

Implement L4

| i3 | i2 | i1 | i <sub>0</sub> | dec    | L4 |

|----|----|----|----------------|--------|----|

| 0  | 0  | 0  | 0              | 0      | 1  |

| 0  | 0  | 0  | 1              | 1      | 0  |

| 0  | 0  | 1  | 0              | 2<br>3 | 0  |

| 0  | 0  | 1  | 1              | 3      | 0  |

| 0  | 1  | 0  | 0              | 4      | 1  |

| 0  | 1  | 0  | 1              | 5      | 1  |

| 0  | 1  | 1  | 0              | 6      | 1  |

| 0  | 1  | 1  | 1              | 7      | 0  |

| 1  | 0  | 0  | 0              | 8      | 1  |

| 1  | 0  | 0  | 1              | 9      | 1  |

|    |    |    |                |        |    |

R. Dick Introduction to Computer Engineering – EECS 203

| Administrative Stuff<br>Review<br>Switch Models<br>Transistors and CMOS Design<br>Homework |

|--------------------------------------------------------------------------------------------|

|                                                                                            |

## L4 implementation

In a future lecture, I'll explain how to do this sort of design.

| 14 R. Dick                                                                                | Introduction to Computer Engineering – EECS 203 |

|-------------------------------------------------------------------------------------------|-------------------------------------------------|

|                                                                                           |                                                 |

| Administrative Stuff<br>Review<br>Switch Modes<br>Transistors and CMOS Design<br>Homework |                                                 |

| Constraints on network outp                                                               | ut                                              |

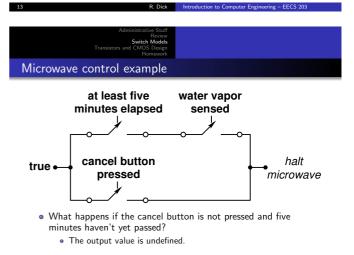

Under all possible combinations of input values

- Each output must be connected to an input value

- No output may be connected to conflicting input values

R. Dick

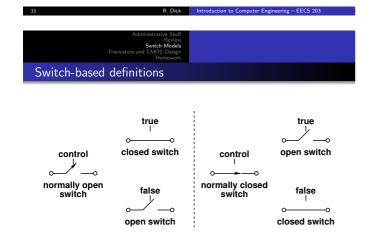

- A switch shorts or opens two points dependant on a control signal

- Used as models for digital transistors

- Why is using normally open and normally closed particularly useful for CMOS?

- NMOS and PMOS transistors easy to model

R. Dick Introduction to Computer Engineering – EECS 203

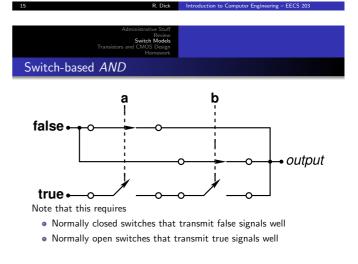

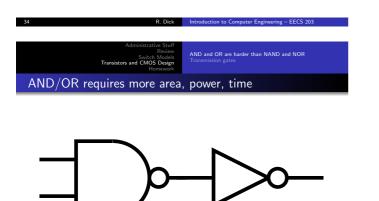

Therefore,  $\it NAND$  and  $\it NOR$  gates are used in CMOS design instead of  $\it AND$  and  $\it OR$  gates

- Administrative Stuff Rociov Switch Models Transmission and CMOS Design Homework Relationship with CMOS

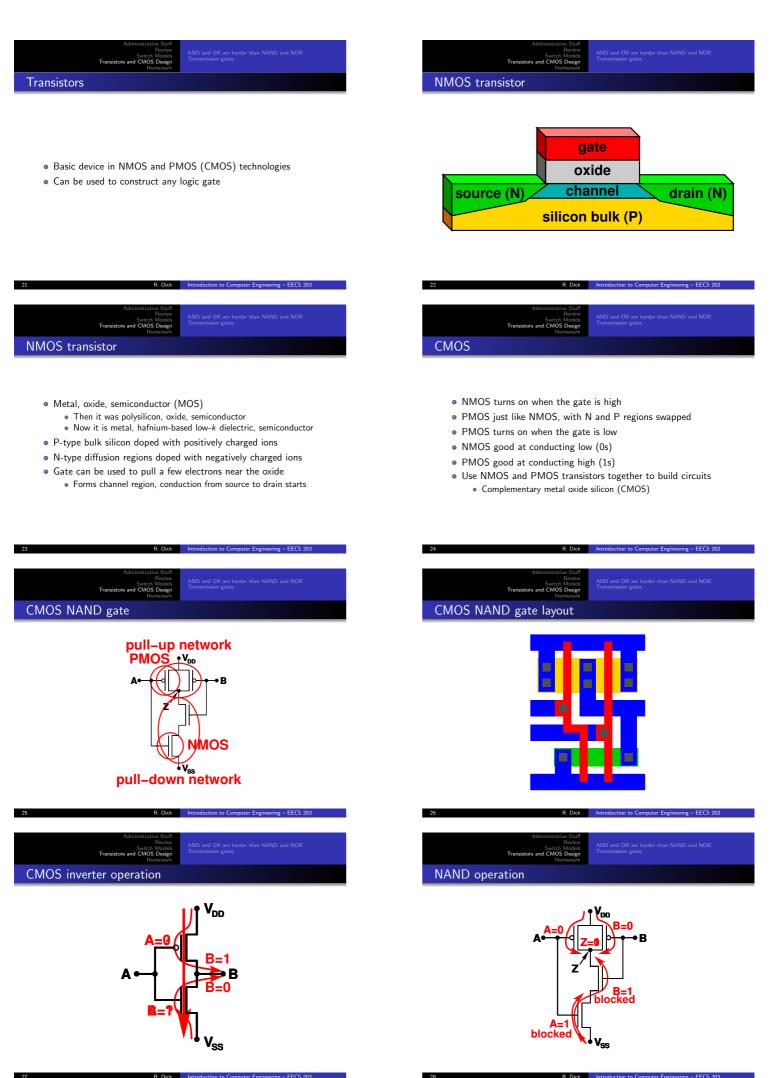

- Metal Oxide Semiconductor

- Positive and negative carriers

- Complimentary MOS

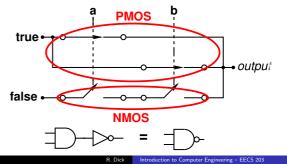

- PMOS gates are like normally closed switches that are good at transmitting only true (high) signals

- NMOS gates are like normally open switches that are good at transmitting only false (low) signals

Introduction to Computer Engi

| 29  | R. Dick                                                                                           | Introduction to Computer Engineering – EECS 203               | 31      |

|-----|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------|

|     |                                                                                                   |                                                               |         |

|     | Administrative Stuff<br>Review<br>Switch Models<br><b>Transistors and CMOS Design</b><br>Homework | AND and OR are harder than NAND and NOR<br>Transmission gates |         |

| NMC | S/PMOS transistors fo                                                                             | r AND/OR                                                      | NMOS tr |

|     |                                                                                                   |                                                               |         |

- $V_T$ , or threshold voltage, is commonly 0.7 V

- NMOS conducts when  $V_{GS} > V_T$

- PMOS conducts when  $V_{GS} < -V_T$

- What happens if an NMOS transistor's source is high?

- Or a PMOS transistor's source is low?

- Alternatively, if one states that  $V_{TN}=0.7$  V and  $V_{TP}=-0.7$  V then NMOS conducts when  $V_{GS}>V_{TN}$  and PMOS conducts when  $V_{GS}< V_{TP}$

| 32                               | R. Dick            | Introduction to Computer Engineering – EECS 203               |  |  |

|----------------------------------|--------------------|---------------------------------------------------------------|--|--|

|                                  |                    |                                                               |  |  |

| Transistors and CMOS             | Review<br>1 Models | AND and OR are harder than NAND and NOR<br>Transmission gates |  |  |

| NMOS/PMOS transistors for AND/OR |                    |                                                               |  |  |

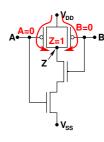

- If an NMOS transistor's input were  $V_{DD}$  (high), for  $V_{GS} > V_{TN}$ , the gate would require a higher voltage than  $V_{DD}$

- If an PMOS transistor's input were  $V_{SS}$  (low), for  $V_{GS} < V_{TP}$ , the gate would require a lower voltage than  $V_{SS}$

33 R. Dick Introduction to Computer Engineering – EECS 203

Administrative Stuff

Review

Switch Models

Transistors and CMOS Design

Homework

NAND/NOR easy to build in CMOS

gate

oxide

channel

silicon bulk (P)

AND and OR are ha

drain (N)

Switch Mo s and CMOS De

ansistor

source (N)

R. Dick Introduction to Computer Engineering - EECS 203

- NMOS is good at transmitting 0s

Bad at transmitting 1s

- PMOS is good at transmitting 1s

Bad at transmitting 0s

- To build a switch, use both: CMOS

| Administrative Stuff<br>Review<br>Transistors and CMOS Design<br>CCMOS transmission gate (TG) | Administrative Stuff<br>Review<br>Switch Models<br>Transistors and CMOS Design<br>Homework<br>Other TG diagram |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                                                               |                                                                                                                |

| 39 R. Dick Introduction to Computer Engineering EECS 203                                      | 40 R. Dick Introduction to Computer Engineering – EECS 203                                                     |

| Administrative Stuff<br>Review<br>Switch Models<br>Transistors and CMOS Design<br>Homework    | Administrative Stuff<br>Review<br>Switch Models<br>Transistors and CMOS Design<br>Homework                     |

| What can we build with TGs?                                                                   | Computer geek culture reference                                                                                |

|                                                                                               |                                                                                                                |

| • Anythingtry some examples.                                                                  | <ul><li>http://slashdot.org/</li><li>http://www.python.org/</li></ul>                                          |

42

R. Dick Introduction to Computer Engineering – EECS 203

| Administrative Stuff<br>Review<br>Switch Models<br>Transistors and CMOS Design<br><b>Homework</b> |  |

|---------------------------------------------------------------------------------------------------|--|

| Reading assignment                                                                                |  |

R Dick Introd

ing - FECS 203

er Eng

• M. Morris Mano and Charles R. Kime. *Logic and Computer Design Fundamentals*. Prentice-Hall, NJ, fourth edition, 2008

44 R. Dick Introduction to Computer Engineering – EECS 203

• Sections 2.3–2.5

//1