#### Introduction to Computer Engineering - EECS 203 Change in style http://ziyang.eecs.northwestern.edu/~dickrp/eecs203/ Instructor Office: Robert Dick L477 Tech TA: Office Neal Oza Tech. Inst. L375 Micro-controller based design Email: dickrp@northwestern.edu Phone 847-467-0033 Phone 847-467-2298 Email nealoza@u.northwestern.edu • In this lecture, I want a lot of help and participation TT: David Bild • You now have the fundamental knowledge to design a processor Office: Phone Tech. Inst. L470 847-491-2083 • Let's build a simple one on paper d-bild@northwestern.edu Email: • You'll be programming a slightly more complex processor in next week's lab assignment NORTHWESTERN

UNIVERSITY

3

R. Dick

Introduction to Computer Engineering - EECS 203

Instruction processors Homework

Instruction processors Homework

Instruction processors Homework

RSE processor

RSE registers

- All registers are 8-bit

- Four general-purpose registers, A, B, C, and D

Used to do computation

- Program counter PC

- Stack pointer SP (sometimes called TOS for top of stack), which may also be used as a general-purpose register

- ALU capable of adding (0) and subtracting (1)

- Already understand building FSMs

- Can use array of latches to store multiple bits: register

- Consider simple processor, called RSE (Rob's simplified example)

R Dick Introduction to Computer Engli

- EECS 203

### RSE arithmetic instructions

- add R<sub>D</sub>, R<sub>S1</sub>, R<sub>S2</sub>

- sub *R<sub>D</sub>*, *R<sub>S1</sub>*, *R<sub>S2</sub>*

Do computation on source registers and put result in destination register

R. Dick In

R Dick Introduction to Computer Enginee

ng - FECS 2

- R. Dick Introduction to Computer Engineering EECS 203

Instruction processors

Homework

RSE data motion

- Idm *R<sub>D</sub>*, [*R<sub>S</sub>*]

- Load from memory location indicated by the source register into destination register

- stm [*R<sub>D</sub>*], *R<sub>S</sub>*

- Store to memory location indicated by the destination register from source register

- Idi R<sub>D</sub>, I

- Load immediate into destination register

- ldpc R<sub>S</sub>

- Load from program counter to destination register

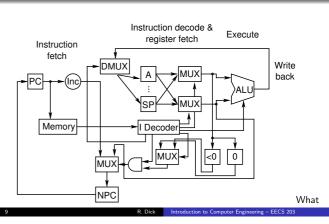

#### Architecture

#### Branch instructions

blz *R<sub>T</sub>*, *R<sub>C</sub>*

Set *PC* to *R<sub>T</sub>* if *R<sub>C</sub>* < 0</li>

bz *R<sub>T</sub>*, *R<sub>C</sub>*

Set *PC* to *R<sub>T</sub>* if *R<sub>C</sub>* = 0

| Instruction processors                                                                                                                                                                               | Instruction processors                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Homework                                                                                                                                                                                             | Homework                                                                                 |

| <ul> <li>How many instructions?</li> <li>Worst-case operands? <ul> <li>3 registers (each how many bits?)</li> <li>1 register and 1 immediate</li> <li>To pack or not to pack?</li> </ul> </li> </ul> | <ul> <li>Chip has reset line</li> <li>Set PC to byte 2</li> <li>Start running</li> </ul> |

| 10 R. Dick Introduction to Computer Engineering – EECS 203                                                                                                                                           | 11 R. Dick Introduction to Computer Engineering – EECS 203                               |

| Instruction processors                                                                                                                                                                               | Instruction processors                                                                   |

| Homework                                                                                                                                                                                             | Homework                                                                                 |

| Memory                                                                                                                                                                                               | Program counter                                                                          |

- Acts like a collection of byte-wide registers

- Address using a decoder

- Can put other devices at some memory locations • Memory-mapped input-output

- Can also use special-purpose output instructions or registers

- Let's build some from D flip-flops

- Multiplexing address and data lines?

Example high-level code

Sum up the contents of memory locations 2-6 ● *A* = 0 I For B from 2 to 6 3 A = A + [B]

Example low-level code

Every clock tick the processor

Decodes the instruction

• Executes the instruction

• Increments the program counter

• Fetches the operands

• Stores the results

РС

PC

Sum up the contents of memory locations 2-6

| 2. <i>A</i> = 0                               | ldi A, 0 or sub A, A, A         |

|-----------------------------------------------|---------------------------------|

| 4. <i>B</i> = 2                               | ldi <i>B</i> , 2                |

| 6. <i>C</i> = [ <i>B</i> ] (loop start point) | ldm <i>C</i> , [ <i>B</i> ]     |

| 8. $A = A + C$                                | add A, A, C                     |

| 10. $B = B + 1$                               | ldi C, 1 — add B, B, C          |

| 14. $C = 6$ (loop start)                      | ldi <i>C</i> , 6                |

| 16. If $B \leq 6$ ( $B < 7$ ) branch to C     | ldi D, 7 — sub D, B, D — blz C, |

| D                                             |                                 |

| (Done)                                        |                                 |

${\ensuremath{\, \bullet }}$  Fetches an instruction from the memory location pointed to by

• Can jump to another code location by moving a value into the

ing - EECS 203

Assemble to our encodings

- What happens on overflow or underflow?

- Special register?

Error conditions

• Special value associated with each register?

Introduction to Computer Engin

- Single-instruction compare and branch?

- Advantages and disadvantages of each?

- After assembling, can put program contents into memory, starting at byte 2

- Compiling from higher-level languages also possible

| Instruction processors<br>Honework                            | Instruction processors<br>Homework                                                                |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Example high-level code                                       | Lesson                                                                                            |

|                                                               |                                                                                                   |

|                                                               | <ul> <li>With only a few registers and instructions, powerful actions are<br/>possible</li> </ul> |

| Sum up the contents of memory locations 2-6<br>• <i>i</i> = 0 | <ul> <li>Less time and power efficient than special-purpose hardware<br/>design</li> </ul>        |

| For j from 2 to 6                                             | <ul> <li>Instruction processors are flexible</li> </ul>                                           |

| i = i + [j]                                                   | <ul> <li>Allows massive use of a single type of IC</li> </ul>                                     |

|                                                               | <ul> <li>Assembly is painful</li> </ul>                                                           |

|                                                               | <ul> <li>However, much better than doing hardware design</li> </ul>                               |

|                                                               | <ul> <li>Compilation also possible</li> </ul>                                                     |

|                                                               |                                                                                                   |

|                                                               |                                                                                                   |

| 18 R. Dick Introduction to Computer Engineering - EECS 203    | 19 R. Dick Introduction to Computer Engineering - EECS 203                                        |

## Assigned reading

• M. Morris Mano and Charles R. Kime. *Logic and Computer Design Fundamentals.* Prentice-Hall, NJ, fourth edition, 2008

R. Dick Introduction to Computer Engineering – EECS 203

n processors Homework

- Refer to Chapter 7 and 8

- Read Sections 9.1-9.7, 10.1-10.6, 10.8

# Computer geek culture references

- Building multicontroller-based devices for the fun of it

- http://www.bdmicro.com

- http://www.commlinx.com.au/microcontroller.htm

- http://members.home.nl/bzijlstra/

- http://www.robotcafe.com/dir/Companies/Hobby/more3.shtml

R. Dick Introduction to Computer Engin

ing - FECS 203

• Etc.

23

Today's topics

ArchitectureAssembly

• Compilation

• PIC16C74A

R. Dick Introduction to Computer Engineering – EECS 203