|                                         | uction to Compute<br>tp://ziyang.eecs.northwe                           |                                                                          | eering – EECS 203<br>µ/~dickrp/eecs203/                                      |

|-----------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Instruct<br>Office:<br>Email:<br>Phone: | or: Robert Dick<br>L477 Tech<br>dickrp@northwestern.edu<br>847–467–2298 | TA:<br>Office:<br>Phone:<br>Email:<br>TT:<br>Office:<br>Phone:<br>Email: | A47-467-0033<br>nealoza@u.northwestern.edu<br>David Bild<br>Tech. Inst. L470 |

|                                         | NORTHV                                                                  | WEST                                                                     | ERN                                                                          |

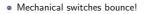

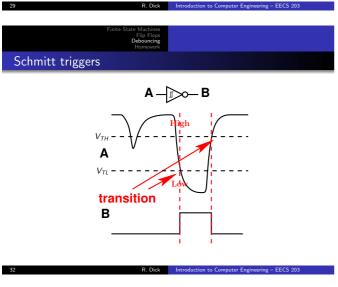

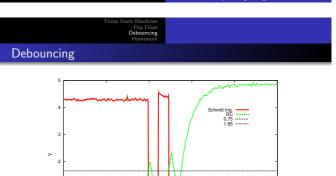

|                                         | Finite State Machines<br>Flip Flops<br>Debouncing<br>Homework           |                                                                          |                                                                              |

| Word des                                | cription to state dia                                                   | agram                                                                    |                                                                              |

|                                         |                                                                         |                                                                          |                                                                              |

• We can enumerate the inputs on which an apple should be released

$$\label{eq:dd} \begin{aligned} ddd+ddq+dq+qd+qq\\ d(dd+dq+q)+q(d+q)\\ d(d(d+q)+q)+q(d+q) \end{aligned}$$

For  $d,\ i=0,\ \text{for}\ q,\ i=1$

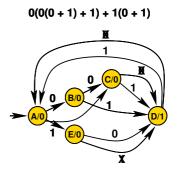

$$0(0(0+1)+1)+1(0+1)$$

| Finite State Machines                |  |

|--------------------------------------|--|

| Flip Flops<br>Debouncing<br>Homework |  |

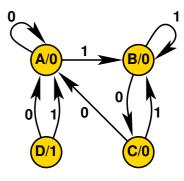

| State diagram to state table         |  |

|                                      |  |

ng – EECS

| Current<br>state | ne<br>sta<br>i=0 | ext<br>ate<br>  i=1 | output (r) |

|------------------|------------------|---------------------|------------|

| А                | В                | E                   | 0          |

| В                | С                | D                   | 0          |

| С                | D                | D                   | 0          |

| D                | А                | A                   | 1          |

| Е                | D                | D                   | 0          |

### Word description to state diagram

- Design a vending machine controller that will release (output signal r) an apple as soon as 30¢ have been inserted

- The machine's sensors will clock your controller when an event occurs. The machine accepts only dimes (input signal *d*) and quarters (input signal *q*) and does not give change

- When an apple is removed from the open machine, it indicates this by clocking the controller with an input of d

- The sensors use only a single bit to communicate with the controller

#### R. Dick Introduction to Computer Engineering – EECS 203

| Finite State Machines<br>Filip Flops<br>Debouncing<br>Homework |

|----------------------------------------------------------------|

| Word description to state diagram                              |

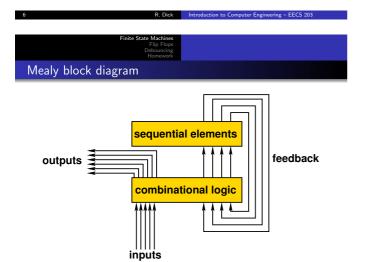

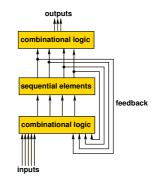

Finite State Machines Plip Flogs Debuncing Homework Moore block diagram

R. Dick Introduction to Computer Engineering – EECS 203

### Moore FSMs

#### Flip Flips Debouncing Homework

#### Mealy FSMs

#### Finite State Machines Flip Flops Debouncing Homework

#### FSM design summary

- Specify requirements in natural form

- Manually derive state diagram

- Automatic way to go from English to FSM, however more theory required

- Can minimize state count, however, more theory also required

- See me if you want more information on this, or take a compilers course and a graduate-level switching theory course, or take my ECE 303

- ${\ensuremath{\, \bullet \,}}$  Assign values to states to minimize logic complexity

- Optimize implementation of state and output functions

R. Dick Introduction to Computer Engineering – EECS 203

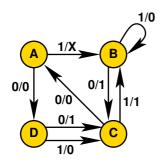

| Mealv | tabular | form |  |

|-------|---------|------|--|

|   |   | $s^+/q$ |       |

|---|---|---------|-------|

|   | s | 0       | 1     |

|   | A | D/C     | ) B/X |

|   | В | C/1     | B/0   |

|   | С | A/0     | B/1   |

| I | D | C/1     | C/0   |

• Latches: Level sensitive

11

• Flip-flops: Edge-triggered

| 14            | R. Dick                             | Introduction to Computer Engineering - EECS 203 |

|---------------|-------------------------------------|-------------------------------------------------|

|               |                                     |                                                 |

|               | Finite State Machines<br>Flip Flops |                                                 |

|               | Debouncing<br>Homework              |                                                 |

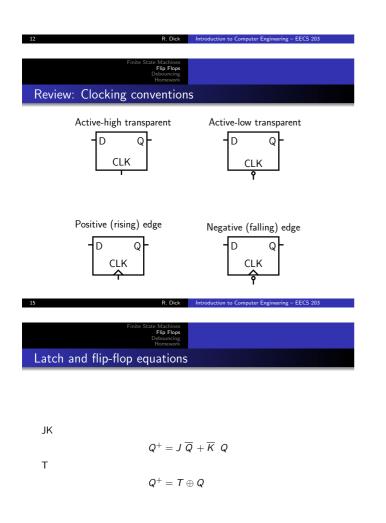

| Latch and fli | ip-flop equations                   |                                                 |

|               |                                     |                                                 |

|               |                                     |                                                 |

|               |                                     |                                                 |

| RS            |                                     |                                                 |

| K5            |                                     | _                                               |

|               | $Q^+ = S$                           | +R Q                                            |

| D             |                                     |                                                 |

|               | $Q^+ = D$                           |                                                 |

|               | 4 5                                 |                                                 |

|               |                                     |                                                 |

|               |                                     |                                                 |

| 16       | R. Dick                                                              | Introduction to Computer Engineering – EECS 203 |

|----------|----------------------------------------------------------------------|-------------------------------------------------|

|          |                                                                      |                                                 |

|          | Finite State Machines<br><b>Flip Flops</b><br>Debouncing<br>Homework |                                                 |

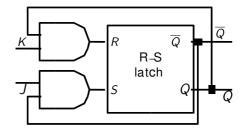

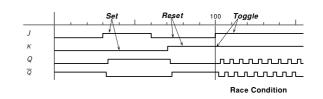

| JK latch |                                                                      |                                                 |

ing - EECS 203

Use output feedback to ensure that  $RS \neq 11$   $Q^+ = Q ~\overline{K} ~+ \overline{Q} ~J$

## Flip Flops Debouncing

JK latch

| J | Κ | Q | $Q^+$ |        |

|---|---|---|-------|--------|

| 0 | 0 | 0 | 0     | hold   |

| 0 | 0 | 1 | 1     | noiu   |

| 0 | 1 | 0 | 0     | reset  |

| 0 | 1 | 1 | 0     | reset  |

| 1 | 0 | 0 | 1     | cot    |

| 1 | 0 | 1 | 1     | set    |

| 1 | 1 | 0 | 1     | torrlo |

| 1 | 1 | 1 | 0     | toggle |

R. Dick Introduction to Co

ing - EECS 203

ing - FECS 203

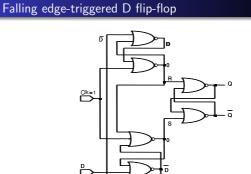

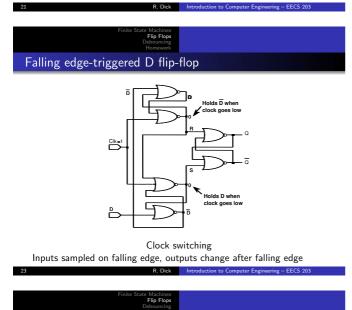

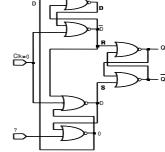

### 19 R. Dick Int Flip Flops Falling edge-triggered D flip-flop

- Use two stages of latches

- When clock is high

- First stage samples input w.o. changing second stage

- Second stage holds value

- When clock goes low

- First stage holds value and sets or resets second stage

- Second stage transmits first stage

- $Q^+ = D$

- One of the most commonly used flip-flops

R Dick Int

Flip Flop

Clock high

## Another view of an edge-triggered DFF

# Flip Flops Falling edge-triggered D flip-flop

Flip Flops

Clock low

R. Dick ng - EECS 203

R. Dick Introduction to Computer Engineering – EECS 203

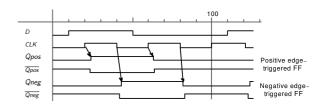

### Edge triggered timing

| Finite State Machines<br>Fip Flops<br>Debouncing<br>Homework | Finite State Machines<br><b>Filip Flops</b><br>Debourcing<br>Homework |

|--------------------------------------------------------------|-----------------------------------------------------------------------|

| RS clocked latch                                             | JK flip-flop                                                          |

|                                                              |                                                                       |

|                                                              |                                                                       |

|                                                              |                                                                       |

- Storage element in narrow width clocked systems

- Dangerous

- Fundamental building block of many flip-flop types

- Versatile building block

- Building block for D and T flip-flops

- Has two inputs resulting in increased wiring complexity

- Edge-triggered varieties exist

| 27 R. Dick                                                   | Introduction to Computer Engineering – EECS 203 | 28 R. Dick                                                           | Introduction to Computer Engineering – EECS 203 |

|--------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------|

| Finite State Machines<br>Flip Flop<br>Debouncing<br>Homework |                                                 | Finite State Machines<br>Flip Flops<br><b>Debouncing</b><br>Homework |                                                 |

| D flip-flop                                                  |                                                 | Debouncing                                                           |                                                 |

- Minimizes input wiring

- Simple to use

- Common choice for basic memory elements in sequential circuits

- What happens if multiple pulses? • Mutliple state transitions

- Need to clean up signal

- M. Morris Mano and Charles R. Kime. Logic and Computer Design Fundamentals. Prentice-Hall, NJ, fourth edition, 2008

- Review Sections 5.1–5.7

- If FSMs don't make sense now, please ask questions, or see me

FSMs are tricky at first Almost everybody has this moment of

R. Dick Introduction to Computer Engineering – EECS 203

- epiphany at which they suddenly make sense

- Section 9.1-9.6

- EECS 202

ing – EECS 20

Flip Fl Debounc Home Computer geek culture references

R. Dick

- Parsers and lexical analyzers

- Writing problem-specific languages

- A. V. Aho, R. Sethi, and J. D. Ullman. Compilers principles, techniques, and tools. Addison-Wesley, MA, 1986

- Lex and yacc

- Flex and bison